Fターム[5F038CA06]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 対称配置 (380)

Fターム[5F038CA06]に分類される特許

1 - 20 / 380

半導体装置

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

半導体装置

【課題】VIAホールを高密度に形成したとしても半導体素子が割れやすくなるのを防止し、素子の形成歩留りを向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板110と、基板の第1表面に配置され、それぞれ複数のフィンガーを有するゲート電極124、ソース電極120およびドレイン電極122と、ソース電極120の下部に配置されたVIAホールSCと、基板の第1表面とは反対側の第2表面に配置され、VIAホールを介してソース電極に接続された接地電極とを備え、VIAホールSCは、基板110を形成する化合物半導体結晶のへき開方向とは異なる方向に沿って配置される。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における抵抗の比精度の改善にある。

【解決手段】第1抵抗R1の第1抵抗体10は、長さL、幅Wを有する。第1コンタクト12aは、第1抵抗体10の一端に形成され、第2コンタクト12bは、第1抵抗体10の他端に形成される。第2抵抗R2の第2抵抗体10は、長さL/2、幅Wを有する。第2抵抗体10の一端には、N個の第1コンタクト12aが形成され、第2抵抗体10の他端には、N個の第2コンタクト12bが形成される。

(もっと読む)

半導体装置

【課題】パワー半導体素子において、周辺の電界強度を緩和する構造を小さな面積で実現する。

【解決手段】周辺領域Qにおいては、半導体層との間に周辺層間絶縁層(絶縁層)を介して複数の多結晶シリコン層70が、ソース電極30から端部ドレイン電極41の間にかけて設けられる。多結晶シリコン層70には、その長手方向が水平方向から傾斜した(傾斜角θ、0<θ<90°)傾斜部が設けられている。多結晶シリコン層70の傾斜部においては、p型領域71と、n型領域72とが長手方向に交互に多数形成されている。

(もっと読む)

半導体装置

【課題】インダクタの下方の層間絶縁膜への水の浸入を抑制し、かつ、インダクタ性能の低下を抑制する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に設けられた層間絶縁膜と、前記層間絶縁膜の上部に設けられたインダクタと、前記半導体基板上に設けられ、前記インダクタの下方の前記層間絶縁膜を前記半導体基板の平面方向で囲む第一の金属壁と、前記半導体基板上に設けられ、前記第一の金属壁で囲まれた領域の外側の前記層間絶縁膜を前記半導体基板の平面方向で挟む一対の第二の金属壁と、を備え、前記第一の金属壁は、前記第一の金属壁の両端部を非接触の状態とする開口を有し、前記第二の金属壁は、前記第一の金属壁の両端部にそれぞれの一端を連結するとともに、前記第一の金属壁で囲まれた領域の外側の位置に開口を有する。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

半導体装置

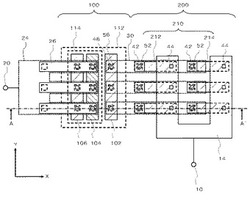

【課題】Y方向に隣接する2つの回路ブロックに対しX方向に延在する制御線からタイミング信号を同時に供給する。

【解決手段】例えば、Y方向に配列されたポートPT1,PT2と、ポートPT1,PT2にそれぞれ接続された回路C1,C2と、X方向に延在し回路C1,C2それぞれに含まれるサブ回路SC1,SC2を共通に制御する制御線CTL1を備える。サブ回路SC1,SC2のY方向における中間座標である座標Y1は、ポートPT1,PT2のY方向における中間座標Y0とは異なる。制御線CTL1からサブ回路SC1,SC2へのY方向における距離は互いに等しい。本発明によれば回路C1,C2の動作タイミングを正確に一致させることが可能となる。しかも、複数の制御線を必要とする場合であっても、制御線ごとに対応するサブ回路までの距離を一定とすることが可能となる。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

半導体集積回路

【課題】電源ノイズを抑制する。

【解決手段】電源電圧Vddまたは基準電圧Vssが印加される主配線(第1基準電圧幹線VSS1)と、複数の副配線(基準電圧枝線VSSB)と、複数の基準電圧枝線VSSBに接続されている複数の回路セル(不図示)と、入力される制御信号に応じて、複数の基準電圧枝線VSSBのうち、所定の回路セルが接続されている基準電圧枝線VSSBと第1基準電圧幹線VSS1との接続および遮断を制御する電源スイッチセルSW1,SW2,…と、複数の基準電圧枝線VSSBを相互に接続する補助配線50と、を有する。

(もっと読む)

半導体装置、DC−DCコンバータ及び受像器

【課題】配線抵抗を低減し導通損失による効率低下を改善した半導体装置、DC−DCコンバータ及び受像器を提供する。

【解決手段】第1の導電体と、半導体素子搭載部と、半導体素子と、第1の接続部と、第2の接続部とを備えた半導体装置が提供される。前記第1の導電体は、前記半導体素子搭載部の周囲に設けられている。前記半導体素子は、前記半導体素子搭載部に設けられ、第1のスイッチ素子と、前記第1のスイッチ素子と並列的に設けられた第2のスイッチ素子とを有する。前記第1の接続部と前記第2の接続部とは、前記第1のスイッチ素子と前記第2のスイッチ素子との境界を延長した仮想的な境界線よりも前記第1のスイッチ素子の側に設けられ、前記第1のスイッチ素子と前記第2のスイッチ素子とに電気的に接続され、前記第1の導電体と電気的に接続される。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

レイアウト方法及び半導体装置の製造方法

【課題】ダブルパターニングによるトランジスタの特性ばらつきを抑える。

【解決手段】並列に配置される複数のゲート電極パターン10〜15を交互に、ダブルパターニングの第1の露光工程で形成する第1のパターン及び第2の露光工程で形成する第2のパターンとして設定し(ステップS1)、第1のパターンと第2のパターンとを並列に接続したトランジスタ対を含む回路をレイアウトすることで(ステップS2)、ダブルパターニングによるトランジスタの特性ばらつきが抑えられる。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

半導体装置

【課題】従来の入出力セルよりも回路面積の大きな入出力セルを面積効率良く配置する。

【解決手段】半導体装置において、複数の第1バッファセル31〜34は、基板の一辺に沿って1列に設けられる。複数の第2バッファセル21,22は、複数の第1バッファセルよりも基板の中央寄りの位置に、複数の第1バッファセルの配列方向に沿って1列に設けられる。複数の第1パッド81〜88は、複数の第1バッファセルの上部に上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、複数の第1パッドよりも基板の中央寄りの位置に、上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、各々が、複数の第1バッファセルのいずれか1つと個別に接続される複数の第3のパッド61,63,65,66と、各々が、複数の第2バッファセルのいずれか1つと個別に接続される複数の第4パッド62,64とを含む。

(もっと読む)

半導体装置

【課題】複数のスパイラルを直列に接続してインダクタを形成する場合において、スパイラルを大面積化することなく、スパイラルの巻線を長くする。

【解決手段】インダクタ10は、第1スパイラル100及び第2スパイラル200を有している。第1スパイラル100は、インダクタ10の巻軸と平行な第1の方向から見た場合、中心から外側に向かって巻かれている。第2スパイラル200は、第1の方向から見た場合、外側から中心に向かって、第1スパイラル100と同一の向きに巻かれている。第1スパイラル100及び第2スパイラル200は、外側の端部同士、または中心側の端部同士が、外側接続部材300又は中心側接続部材400を介して接続されている。第2スパイラル200は、第1スパイラル100を、巻軸を回転中心として右回りに90°回転させてから、巻軸に直交する平面に含まれる水平線を基準に鏡映させ、かつ縦横比を変更した形状である。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

データ保持装置及びこれを用いた論理演算回路

【課題】マスクパターンの疎密に起因する強誘電体素子の特性ばらつきを適切に低減することが可能なデータ保持装置及び、これを用いた論理演算回路の提供。

【解決手段】データ保持装置において、不揮発性記憶部に含まれる複数の強誘電体素子X(素子幅m)は、各々よりも素子幅の小さいダミー素子Y(素子幅n、ただしn<m)によって包囲されている。これによってマスクパターンの疎密に起因するエッチングのローディング効果を抑制する事が可能となる。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

半導体装置、及びその製造方法

【課題】ピラーを確実に配置することが可能な半導体装置、及びその製造方法を提供する。

【解決手段】本発明の一態様にかかる半導体装置30は、内部回路領域20と、内部回路領域20の外側に設けられたI/O領域10と、を備える半導体チップ1と、半導体チップ1とフリップチップ接続されたパッケージ基板6と、半導体チップ1とパッケージ基板6との間に配置され、半導体チップ1の最上層配線層12に含まれる2本以上の接地配線12a上に形成されて、2本以上の接地配線12aを接続する導電性のピラー4と、を備えるものである。

(もっと読む)

1 - 20 / 380

[ Back to top ]