Fターム[5F038CD14]の内容

半導体集積回路 (75,215) | 配電、布線 (8,653) | 配線容量(寄生容量) (860) | 容量付加安定化 (354)

Fターム[5F038CD14]に分類される特許

1 - 20 / 354

半導体集積回路、半導体集積回路の制御方法

半導体装置

半導体装置

【課題】異なる配線を介して異なる電源端子から内部回路を構成する第1の回路および第2の回路にそれぞれ給電する際に、第1の回路に給電する配線と第2の回路に給電する配線との間に発生するノイズを抑制する。

【解決手段】半導体装置は、第1の回路に給電を行う第1の電源配線と、第2の回路に給電を行う第2の電源配線と、第1の電源配線と第2の電源配線との間に容量素子を設けることにより、両端子間のインピーダンスを、大幅に低減させることにより異種電源間のノイズを低減する。

(もっと読む)

半導体集積回路及びその設計方法

【課題】チップサイズを増大することなく、キャパシタの容量を増やすことができる半導体集積回路を提供する。

【解決手段】半導体基板10上にメインブロック11と周辺ブロック12とが混載された半導体集積回路において、半導体基板10上のメインブロック11に形成され、第1のトレンチキャパシタを有するメイン回路と、半導体基板10上の周辺ブロック12に形成され、第2のトレンチキャパシタを有するアナログ回路とを備える。

(もっと読む)

半導体装置

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体集積回路及びその制御方法

【課題】デカップリング容量素子の信頼性と、フラッシュメモリの動作モードに対応した供給電流の補償を損なわずに、フラッシュメモリの面積増加を抑制する。

【解決手段】本発明に係る半導体集積回路10は、フラッシュメモリ部12と、フラッシュメモリ部12に電圧を供給する昇圧回路13と、昇圧回路13の出力に一端が接続されたデカップリング容量素子15と、フラッシュメモリ部12の動作モードに応じて、デカップリング容量素子15の他端の電位を制御する制御回路14とを備える。

(もっと読む)

半導体集積回路及びその電源制御方法

【課題】電源遮断状態からの復帰の際に、周辺回路の動作に影響を与えない半導体集積回路及び電源制御方法が、望まれる。

【解決手段】半導体集積回路は、第1及び第2の電源線と、サブ電源線と、第1の電源線とサブ電源線との間に配置される第1のスイッチ回路と、第2の電源線とサブ電源線との間に配置される論理回路と、第1の端子が第1の電源線と接続される容量素子と、容量素子の第1の端子の他方の第2の端子の接続を、第1の電源線、又は、サブ電源線、のいずれかに切り替える第2のスイッチ回路と、論理回路を非活性化状態から活性化状態に遷移させる場合に、第1のスイッチ回路により、第1の電源線及びサブ電源線の接続を遮断しつつ、第2のスイッチ回路により、第2の端子の接続を少なくても1回以上、サブ電源線に接続した後、第1の電源線に接続する制御回路と、を備えている。

(もっと読む)

半導体集積回路

【課題】保護素子とガードリング領域との間のウィークスポットが破壊される危険性を軽減する。

【解決手段】半導体集積回路は、静電保護回路の保護素子Mn2を形成するために、第1導電型の半導体領域P−Wellと第2導電型の第1不純物領域Nと第1導電型の第2不純物領域Pにより形成されたガードリングGrd_Rngを具備する。第1不純物領域Nは、長辺と短辺を有する長方形の平面構造として半導体領域の内部に形成される。ガードリングは、第1不純物領域Nの周辺を取り囲んで半導体領域の内部に形成される。第1不純物領域Nの長方形の平面構造の短辺には、ウィークスポットWk_SPが形成される。長方形の長辺と対向するガードリングの第1部分では、複数の電気的コンタクトが形成される。長方形の短辺に形成されるウィークスポットと対向するガードリングの第2部分では、複数の電気的コンタクトの形成が省略される。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

誘電体膜及びその製造方法、並びにキャパシタ

【課題】結晶粒のサイズを制御し、誘電体膜を貫通する結晶粒界やクラックの発生を抑制することによって、リーク電流の少ない高性能のキャパシタを提供する。

【解決手段】電極3,5の間に誘電体膜4が挟持されてなるキャパシタであって、誘電体膜4は、アルカリ土類金属と遷移金属との酸化物に、アルカリ土類金属の炭酸塩を0.1〜10mol%の範囲で含む。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積を削減することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施形態に係る不揮発性半導体記憶装置は、半導体基板と、半導体基板上に積層され、垂直方向に直列接続された複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられ、所望の電圧をメモリセルアレイに供給する電源回路とを備える。電源回路は、電圧を生成するポンプ回路と、ポンプ回路の出力端子に接続され、出力端子の電圧値が所定の値を下回った場合にポンプ回路へ制御信号を出力するリミッタ回路と、出力端子に一端が接続され、出力端子の電圧を調整するように構成されたキャパシタと、キャパシタの他端に接続され、制御信号に基づき所定の電流値の定電流を用いてキャパシタを充電するブースト回路と、ブースト回路の充電動作を停止させるスイッチとを備える。キャパシタは、メモリセルアレイの直下に設けられる。

(もっと読む)

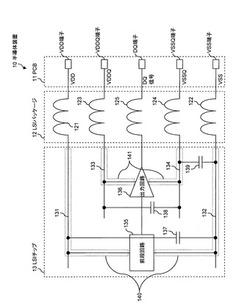

半導体集積回路装置

【課題】内部コアエリアのトランジスタを犠牲にすることなく、周辺エリアのトランジスタを用いてリップルフィルタによる電源供給回路を構成する。

【解決手段】入出力回路を構成するためのトランジスタが配列されてなる周辺エリア(図2の12に相当)をチップ上に有する半導体集積回路装置であって、ドレインを電源に接続し、ソースを負荷側に接続し、ゲートを容量素子(図2のC1)を介して交流的に接地する第1のトランジスタ(図2のMN1)と、容量素子をゲート・基板間によって形成する第2のトランジスタと、を周辺エリアに備える。

(もっと読む)

半導体装置及びその駆動方法

【課題】2つの電位の誤差を増幅して出力する半導体装置におけるスタンバイ状態からの復帰に際して生じる動作遅延を抑制する。

【解決手段】チャネルが酸化物半導体層に形成されるトランジスタによって、トランスコンダクタンスアンプの出力端子とキャパシタの一方の電極の電気的な接続を制御する。よって、トランスコンダクタンスアンプがスタンバイ状態となる場合であっても、当該トランジスタをオフ状態とすることでキャパシタの一方の電極において長期に渡って電荷の保持を行うことが可能となる。また、トランスコンダクタンスアンプをスタンバイ状態から復帰する際には、当該トランジスタをオン状態とすることで、キャパシタの充放電を早期に収束させることができる。これにより、早期に当該半導体装置の動作を定常状態とすることが可能となる。

(もっと読む)

集積回路装置

【課題】被電源遮断回路の十分な安定化容量を確保しつつ、総回路面積の低減を図る。

【解決手段】高電位電源線VDDと低電位電源線VSSとの間に設けられ、各々が電源遮断スイッチPSW1, PSW2と直列に接続された複数段の被電源遮断回路CC1, CC2を含む集積回路装置であって、奇数段の前記被電源遮断回路CC1と直列に接続された前記電源遮断スイッチPSW1は、第1導電型の第1MOSトランジスタであり、偶数段の前記被電源遮断回路CC2と直列に接続された前記電源遮断スイッチPSW2は、前記第1導電型とは異なる第2導電型の第2MOSトランジスタであり、前記偶数段の前記第2MOSトランジスタPSW2のゲートが、当該偶数段の前段の奇数段における前記第1MOSトランジスタと前記被電源遮断回路の第1電源端子との接続ノードN1に接続される。

(もっと読む)

半導体装置

【課題】 電源遮断機能を有する半導体装置において試験用パッドを設けることなく電源ショート試験の実施を可能にする。

【解決手段】 半導体装置は、回路ブロックと、第1電源線と回路ブロックに電源電圧を供給する第2電源線との間に設けられる第1スイッチと、第1電源線と第2電源線との間に設けられる第2スイッチとを備え、第1スイッチは、テストモード時にオンし、第2スイッチは、テストモード時にオフし、第2スイッチのオン/オフに応じて、通常動作モード時に、回路ブロックの動作状態がオン/オフする。

(もっと読む)

半導体装置

【課題】配線層の空きスペースを利用して電源補償容量を形成する。

【解決手段】Y方向に配列された複数のメモリマットMATと、Y方向に隣接するメモリマットMAT間にそれぞれ配置されたセンス領域SAと、カラム選択信号を生成するカラムデコーダ13と、複数のメモリマットMAT上をY方向に延在し、カラム選択信号をカラムデコーダ13から複数のセンス領域SAに供給するカラム選択線YSと、カラムデコーダ13からみて最も遠いメモリマットMATa上に設けられた電源補償容量30とを備える。電源補償容量30は、容量電極として機能する電源配線VL1,VL2を含み、その少なくとも一方がカラム選択線YSと同じ配線層に形成されている。本発明によれば、カラム選択線YSを形成する必要のないメモリマットMATa上に電源補償容量30を設けていることから、チップ面積を縮小することが可能となる。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

1 - 20 / 354

[ Back to top ]