Fターム[5F038DF03]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 特定機能回路(単一機能) (5,304) | AD又はDAコンバータ (388)

Fターム[5F038DF03]に分類される特許

1 - 20 / 388

半導体装置

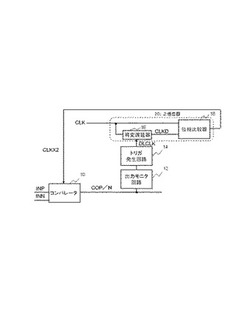

【課題】回路構成の簡素化を図るとともに、遅延回路の遅延時間のばらつき等に起因して生じる問題点を解消し、コンパレータの動作を保証する2逓倍器を備えた半導体装置を提供する。

【解決手段】入力クロック信号CLKを可変遅延器16で遅延させた遅延クロック信号CLKDと、前記入力クロック信号の位相を位相比較器18で比較することで前記入力クロック信号CLKの周波数を2逓倍した2逓倍クロック信号CLKX2を生成する2逓倍器20と、前記2逓倍器20からの2逓倍クロック信号CLKX2が第1の論理レベルのとき入力信号の大小の比較動作を行い、前記2逓倍クロック信号CLKX2が第2の論理レベルのとき、比較動作を停止するコンパレータ10と、前記コンパレータ10の出力をモニタし、前記コンパレータ10が比較結果を出力したことを検出した時点でトリガ信号DLCLKを生成する第1の回路12、14を備える。

(もっと読む)

半導体集積回路、電子機器及びマルチチップ半導体パッケージ

【課題】比較的簡単な構成でありながらも動的で高分解能の電圧制御可能な半導体集積回路、電子機器及びマルチチップ半導体パッケージを提供すること。

【解決手段】電子機器100は、電源IC110と、電源IC110から出力される電源電圧Vsrcで動作するSoC#0〜2とを備える。SoC#0〜2は、三次元実装されたマルチチップ半導体パッケージに搭載される。SoC#0〜2は、第3の端子123から入力されるアナログ制御信号の電位と、内部配線124の電位とに基づいて、第2の端子122から出力するアナログ制御信号を生成する電位制御回路125と、電源フィードバック(FB)電圧入力端子である第2の端子122及び第3の端子123と、を備える。SoC#0〜2は、FB出力端子FB_out/FB入力端子FB_inをカスケード接続し、最終段のSoC#0のFB出力を電源IC110に接続している。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】アナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の抵抗器で分圧して複数の比較用電圧を生成する。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧との比較結果に応じたデジタル信号を出力する。各比較器は、2つの入力の電位差を検出する差動対回路を含む。差動対回路は、第1回路部50と第2回路部60とを有する。第1回路部は、第1入力トランジスタ51と、第1入力トランジスタと直列に接続される抵抗器Rrefとを含む。第2回路部は、第1入力トランジスタと差動対を形成する第2入力トランジスタ61と、第2入力トランジスタと直列に接続される可変抵抗器Rvとを含む。可変抵抗器は、直列に接続されるとともに、制御信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。

(もっと読む)

半導体装置

【課題】半導体素子を、より小型化することができる半導体装置、当該半導体素子、及び基板を得る。

【解決手段】半導体素子12は、階調電圧を出力する半導体素子内部出力部30C,30D(第1及び第2の階調電圧出力部)と、半導体素子内部出力部30Cの周辺に配置され、半導体素子内部出力部30Cに電源を供給する第1の電源端子電極52aと、半導体素子内部出力部30Dの周辺に配置され、半導体素子内部出力部30Dに電源を供給する第2の電源端子電極52aと、を備え、基板18は、半導体素子内部出力部30C,30Dの両方に共通して接続され、半導体素子12の下側に設けられた共通接続部94(第1の配線パターン)と、共通接続部94と外部入力端子(22)とを電気的に接続するインピーダンス調整部96(第2の配線パターン)と、を備える。

(もっと読む)

半導体集積回路装置

【課題】レベル変換回路のレイアウト面積の縮小を図る。

【解決手段】半導体集積回路装置(10)は、レベル変換回路(14)と、D/A変換回路(12)とを備える。このとき、パラレル形式のデジタル信号をシリアル形式に変換して上記レベル変換回路に供給するためのパラレル・シリアル変換回路(15)と、上記レベル変換回路の出力をパラレル形式のデジタル信号に変換して上記D/A変換回路に供給するためのシリアル・パラレル変換回路(13)とを設ける。上記レベル変換回路は、シリアル形式のデジタル信号に対応するレベル変換機能を備えていれば良く、パラレル形式のデジタル信号に対応させる場合に比べて、レベル変換回路のレイアウト面積を縮小することができる。

(もっと読む)

R−2Rラダー抵抗回路、そのR−2Rラダー抵抗回路を備えるD/A変換器及びR−2Rラダー抵抗回路の製造方法

【課題】抵抗Rと抵抗2Rとの抵抗比を1:2に近付けることにより、D/A変換精度の悪化を抑制することを可能にするR−2Rラダー抵抗回路、そのR−2Rラダー抵抗回路を備えるD/A変換器及びR−2Rラダー抵抗回路の製造方法を提供すること

【解決手段】本発明にかかるR−2Rラダー抵抗回路10は、1ビットに対応する抵抗値Rの第1抵抗及び抵抗値2Rの第2抵抗を備える。第1抵抗及び第2抵抗は、1列に並んでいる複数の単位抵抗により構成される。R−2Rラダー抵抗回路10は、前記複数の単位抵抗が並設されて構成されており、第1抵抗に含まれる単位抵抗131がR−2Rラダー抵抗回路10の一端に配置され、単位抵抗131と第1抵抗に含まれる単位抵抗132との間に第2抵抗に含まれる単位抵抗121〜124が配置されている。

(もっと読む)

半導体装置

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

受光デバイス、これを用いた光受信機、及び受光デバイスの製造方法

【課題】 従来のPD製造プロセスと同じ工程で大受光径PDの帯域を拡大して、光受信部の高速化を図る。

【解決手段】 受光デバイスは、半導体基板の上方に形成された第1導電型の第1半導体層、前記第1半導体層上の光吸収層、および前記光吸収層上の第2導電型の第2半導体層の積層構造を有する光検出素子と、前記半導体基板の上方で、前記光検出素子に接続されるインダクタと、前記光検出素子で生成された電流を前記インダクタを介して取り出す出力電極と、前記光検出素子にバイアス電極を印加するバイアス印加用電極と、前記インタダクタの金属配線と交差して、前記光検出素子と、前記出力電極又は前記バイアス印加用電極との間を電気的に接続する交差配線と、を含む。

(もっと読む)

半導体装置および半導体装置の測定方法

【課題】半導体ウエハ上の半導体チップのアナログ特性の測定を精度良く行えるようにする。

【解決手段】半導体チップ1の被測定部3は半導体素子3a、回路3bである。被測定部3のアナログ特性を測定する測定回路4を設けている。測定回路4は、外部電源からプローブ針Pa、Pbを介して給電され、内部で測定用印加電圧を生成し、配線パターン5を介して被測定部3に印加する。測定回路4は、被測定部3の出力を配線パターン5から入力し、デジタルデータに変換する。測定回路4と配線パターン7を介して半導体チップ2の不揮発性メモリ6に接続され、デジタルデータが転送記憶される。一連の測定が終了した後に、不揮発性メモリ6からデジタルデータを取り出す。プローブ針の接触抵抗や浮遊容量の影響を低減して精度良いアナログ特性の測定ができる。

(もっと読む)

半導体装置、電子機器、および半導体装置の検査方法

【課題】電源端子または接地端子の接続不良を容易に検出する。

【解決手段】半導体装置の電源端子TCと第1の入出力端子T1との間には、電源端子TCがカソード側となり、第1の入出力端子T1がアノード側となるようにダイオードD11が設けられる。判定部10Aは、電源電圧Vccに等しいハイレベルの信号が第1の入出力端子T1に入力されたとき、電源端子TCの電圧が第1の入出力端子T1の電圧よりも低いか否かを判定する。

(もっと読む)

半導体装置

【課題】レイアウト面積を大きくすることなく、差動対を高速/高消費電流と、低速/低消費電流の両方で動作させることができるようにした半導体装置を提供する。

【解決手段】差動回路5aは、差動対トランジスタN1,N2と、差動対トランジスタN1,N2に流れる電流量が少なくとも2つのレベルで切替わるように、切替可能なテール電流を供給するテール電流源68とを備える。差動対トランジスタN1,N2は、差動対トランジスタN1,N2に流れる電流の減少に伴って、σ(ΔI/gm)の値が単調に減少する特性を有する、ただし、σは標準偏差、ΔIは、差動対トランジスタN1,N2の電流量の差分、gmは、差動対トランジスタN1,N2のトランスコンダクタンスを表わす。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

温度検出装置、温度検出回路およびパワー半導体モジュール

【課題】温度検出回路と絶縁素子とを同一の基板上に形成できるようにし、装置全体の小型化を容易にする温度検出装置を提供する。

【解決手段】温度検出回路200は、温度センサ35で検出された温度をデジタル値に変換するAD変換回路44とデジタル比較回路45を備えている。デジタル比較回路45の出力は、第1パルス発生器52、第2パルス発生器53を経由して絶縁トランス回路101に入力される。絶縁トランス回路101で発生する誘導電流によりパルス信号が信号復調回路102に伝達される。また、温度センサ35で検出された温度が限界温度を越えたときにコンパレータ49からパルス信号が生成され、同様に、信号復調回路102に伝達される。

(もっと読む)

半導体抵抗素子及び半導体抵抗素子を有する半導体モジュール

【課題】無駄な電流や信号の歪み等を発生させることなく、抵抗素子層の電位と、その周辺の半導体基板や電源線、信号線等の電位との電位差によって抵抗素子層の抵抗値が変化してしまうことを抑えることのできる半導体抵抗素子及び半導体抵抗素子を有する半導体モジュールを提供する。

【解決手段】抵抗素子層13は、抵抗値変化係数K1,K2によって、正極領域である領域13Aと負極領域である領域13Bとに分かれている。基準位置oから領域13Aの中心位置a又は領域13Bの中心位置bまでの間の抵抗値を量とする指標値r1,r2と、当該抵抗値R1,R2と、抵抗値変化係数K1,K2との積の総和が零になるように形成される。つまり、領域13Aの抵抗値変化成分dR1と領域13Bの抵抗値変化成分dR2とを相殺して、抵抗素子層13の抵抗値が変化してしまうのを抑えることができる。

(もっと読む)

半導体集積回路

【課題】内蔵された回路の状態を確認する機能を備えた半導体集積回路を更に小型化することができる技術を提供

【解決手段】半導体集積回路1では、コアLSI11と周辺LSI12との間の内部配線WIが異常であると判定回路15が判定すると、判定回路15は、リングオシレータ16Aを発振させることを指示する情報(第1発振指示情報)をリングオシレータ制御部17へ出力する。そしてリングオシレータ制御部17が第1発振指示情報を取得すると、リングオシレータ制御部17が、発振周波数f1で発振するように構成されたリングオシレータ16Aを発振させる。そして、半導体集積回路1内で発生している磁界を近磁界プローブで測定し、発振周波数f1で大きさが変動する磁界を検出した場合に、リングオシレータ16Aが動作していると判断することができる。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を確保する。

【解決手段】基板と、基板に埋め込まれ、複数の開口部を有する絶縁膜と、複数の開口部内に位置する基板に設けられた複数のダミー拡散層20と、抵抗素子形成領域40において、平面視でダミー拡散層20と重ならないように絶縁膜上に設けられ、かつ第1方向に延伸する複数の抵抗素子10と、抵抗素子形成領域40において、絶縁膜上およびダミー拡散層20上に設けられ、かつ第1方向に延伸する複数のダミー抵抗素子12と、を備え、ダミー抵抗素子12は、平面視で、第1方向と基板に水平な面内において垂直な第2方向に並ぶ少なくとも二つのダミー拡散層20と重なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

半導体装置及びデータ取込方法

【課題】電源ノイズによるデジタル信号の取込エラーを低減すること。

【解決手段】パルス制御信号に応じてスイッチング動作を行なうスイッチング回路120と、デジタル信号を取り込むデジタル信号保持回路111と、を備え、デジタル信号保持回路111は、スイッチング動作による電源ノイズの発生期間におけるデジタル信号の取り込みを回避するためのマスク信号をパルス制御信号から生成するマスク信号生成回路114を含み、電源ノイズの発生期間にはデジタル信号を取り込まず、電源ノイズの非発生期間に前記デジタル信号を取り込む半導体装置。

(もっと読む)

半導体装置

【課題】電圧生成回路を備えた半導体装置において、電圧生成回路の電荷供給能力が十分でない場合であってもチャージシェアを引き起こすことなく、電圧生成回路の出力電圧を従来よりも高精度に検出できるようにする。

【解決手段】半導体装置1は、電圧生成回路11と、第1のスイッチSW2と、充電回路20とを備える。電圧生成回路11は、電圧を生成して出力し、生成する電圧の大きさを調整する機能を有する。第1のスイッチSW2は、オン状態のときに互いに導通する第1および第2の導通端子を有し、第1の導通端子が電圧生成回路11の出力ノードと配線を介して接続される。充電回路20は、第1のスイッチSW2の第2の導通端子に接続された配線を充電する。

(もっと読む)

半導体装置

【課題】消費電力を極力抑制することで電源の安定化を実現する半導体装置を提供する。

【解決手段】ロジック部11、メモリ部12、ロジック部とメモリ部の一方又は両方の動作頻度を検出する検出部13、検出部の検出結果に基づきロジック部及びメモリ部の一方又は両方にしきい値制御信号を供給するしきい値制御部14を有する半導体装置である。ロジック部とメモリ部の各々は複数のトランジスタを有しており、複数のトランジスタの各々は、論理信号が入力される第1のゲート電極と、しきい値制御信号が入力される第2のゲート電極と、半導体膜とを有する。

(もっと読む)

1 - 20 / 388

[ Back to top ]