Fターム[5F038DT02]の内容

Fターム[5F038DT02]に分類される特許

1 - 20 / 655

半導体集積回路

出力制御スキャンフリップフロップ、それを備えた半導体集積回路及び半導体集積回路の設計方法

半導体装置及びそのテスト方法

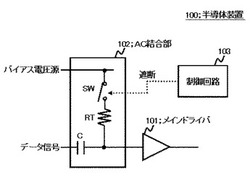

【課題】データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置のDCテストの実施には、振幅を維持できないという問題がある。そのため、データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置であって、DCテストを可能にする半導体装置が、望まれる。

【解決手段】半導体装置は、データ信号を外部に出力するメインドライバと、データ信号が伝達する配線と接続されているコンデンサと、一端がコンデンサと接続され、他の一端がバイアス電圧源に接続されている終端抵抗と、バイアス電圧源と終端抵抗との間に接続されている第1のスイッチと、を含むAC結合部と、テストモード時にAC結合部のバイアス電圧源と終端抵抗との接続を、第1のスイッチにより遮断する制御回路と、を備える。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路

【課題】 論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出する。

【解決手段】 第1および第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有する。制御点は、第1または第3ユーザロジックの第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する。

(もっと読む)

スキャン・チェーン用動的クロック領域バイパス

【課題】スキャン・テスト回路およびスキャン・テスト回路を使用して試験を受けるさらなる回路を備える集積回路を提供すること。

【解決手段】スキャン・テスト回路は、それぞれ別個のクロック領域に関連した複数のサブチェーンを有する少なくとも1つのスキャン・チェーン、および1つまたは複数のサブチェーンを選択的にバイパスするように構成されたクロック領域バイパス回路を備える。スキャン・チェーンは、スキャン・シフト・モードの動作において、サブチェーンを全部よりは少なく含む直列シフト・レジスタを形成するように構成可能であり、サブチェーンの少なくとも残りの1つが、スキャン・シフト・モードにおいて直列シフト・レジスタの部分でないように、クロック領域バイパス回路によりバイパスされる。特定のクロック領域に関連するスキャン・チェーンの部分を選択的にバイパスすることにより、クロック領域バイパス回路は、スキャン・テスト期間の試験時間と電力消費を減らす役割を果たす。

(もっと読む)

半導体装置

【課題】 貫通ビアを用い積層した半導体装置においては、信号を伝送する貫通ビアがオープンやショートした場合に、その貫通ビアを回避して積層チップ全体を正常動作させるために、複雑な回路を構成が必要であった。

【解決手段】 信号を伝送する貫通ビアにおいて、ビアの内壁を構成するシリコンに高い不純物の領域を形成して貫通導体とシリコン基板が接触したときに基板に接続されているVSSなどの基準電位に誘導する。故障モードを固定できるため、冗長化/復号化回路が簡単になるうえ、必要な冗長貫通ビアの本数を削減することができる。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】半導体集積回路の回路面積を小さくする。

【解決手段】被試験回路2の観測対象の複数の信号線TA1〜TA4上の観測点TP1〜TP4を複数の入力端子に接続し、複数の信号線TA1〜TA4を伝搬する値の、論理積、論理和、否定論理積、または否定論理和の何れかを演算し、複数の信号線TA1〜TA4の何れかを伝搬する値に応じた出力値を出力する論理回路(NOR回路3,NAND回路4)を設けることで、複数の観測点をEOR回路を用いて共用する半導体集積回路より回路面積を小さくできる。

(もっと読む)

半導体集積回路及びそのテスト方法

【課題】プローブ針を接触させる外部端子の数を抑制してDCテストを行うことが可能な半導体集積回路を提供すること

【解決手段】本発明にかかる半導体集積回路は、入出力端子P1を介して外部にデータを出力する出力バッファ21と、外部から入出力端子P1を介してデータが入力される入力バッファ22と、入出力端子P1と入力バッファ22の入力との間の信号線上のノードN1と第1入力端子T1との間に設けられたスイッチ26と、外部から第2入力端子T2に供給される第2基準電位とノードN1の電位とを比較して比較結果を出力する比較部23と、入力バッファ22から出力されるデータと比較部23の比較結果との何れかを選択しテスト結果として出力する選択部52と、を備える。

(もっと読む)

半導体テスト回路

【課題】スキャンチェーンを構成する回路でバーンイン試験を行う際に、シフトモードとキャプチャモードを切り替えるスキャンモードコントロール信号が接続された回路に対してもストレス印加を可能にする半導体テスト回路を提供する。

【解決手段】半導体テスト回路は、シフトモードとキャプチャモードを交互に切り替える内部スキャンモードコントロール信号と、スキャンチェーンのスキャンフリップフロップ回路に供給する内部クロック信号を生成するスキャンチェーン制御信号生成部を備える。スキャンチェーン制御信号生成部は、スキャンフリップフロップ回路の出力を遷移させる内部クロック信号のエッジのタイミングにおいて、内部スキャンモードコントロール信号がシフトモードになるように、内部スキャンモードコントロール信号と内部クロック信号の相互のタイミングを制御する。

(もっと読む)

半導体集積回路のテスト回路及びテスト方法

【課題】外部端子数の増加を抑えつつ、半導体集積回路のテスト時間を短縮する。

【解決手段】テスト回路は、入力されるリファレンスクロック109を逓倍して、テスト対象回路106をテスト動作させるための実動作クロック112及びサンプリングクロック105を生成するPLL108と、入力されるテストコマンドに従い、テスタ同期クロック103に同期してテスト対象回路106のテスト結果を出力するテスト結果出力回路107と、を備えるテスト回路であって、テストコマンドを含むテスト入力信号104とサンプリングクロック105とに基づきテスタ同期クロック103を生成するテスタ同期クロック生成回路100を備えるものである。

(もっと読む)

温度検出回路

【課題】 消費電流を抑えるため間欠動作するようにした温度検出用半導体集積回路において、外部端子を増加させることなく回路の評価および検査が行えるようにする。

【解決手段】 発振回路(16)を備え、消費電流を抑えるため間欠動作する温度検出用半導体集積回路において、温度検出回路(11)の出力と基準電圧とを比較する電圧比較回路(13)の出力に対応した信号を出力する外部端子(DET)と、該外部端子に負電位が印加されたことを検出した場合に、温度検出回路と基準電圧回路と電圧比較回路を活性化させる信号を生成する制御回路(17)と、制御回路が活性化信号を出力しかつ温度検出回路の出力が基準電圧を超えたと電圧比較回路(13)が判定した場合に電流を流す電流回路(SW1,R0,SW2)とを設けるようにした。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

半導体回路及びテスト方法

【課題】スキャンチェーンから出力される複数の被試験回路の試験結果情報に基づいて、不良の被試験回路を効率的に特定する半導体回路及びテスト方法を提供する。

【解決手段】複数の被試験回路と、試験回路に対応して設けられた複数の第1のラッチ回路と、第2のラッチ回路と、パターンアドレスに対応して入力信号が規定されたテストパターンのパターンアドレス順に入力される入力信号に基づいて、被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、複数の良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を第2のラッチ回路に出力する総合判定回路と、複数の第1のラッチ回路と第2のラッチ回路とを、第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、スキャンチェーンは、入力信号がスキャン出力モードを示す時に、第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する。

(もっと読む)

半導体装置

【課題】トリミング回路を備えた半導体装置において、内部電源の電圧レベルを半導体装置の外部から適切に制御できるようにすること。

【解決手段】半導体装置は、複数のレベルの間で遷移する第1のテストモード信号を受信し、第1のテストモード信号の遷移に応じてカウント動作を行うバイナリカウンタ回路と、バイナリカウンタ回路の所定のビットの値を示すビット信号、および、バイナリカウンタ回路のカウント動作を制御する第2のテストモード信号を受信し、ビット信号および第2のテストモード信号に応じて、第1のテストモード信号を遷移させるか否かを制御する制御回路と、バイナリカウンタ回路のカウント値に応じて、複数の基準電位の中からいずれかの基準電位を選択するセレクタと、セレクタにより選択された基準電位に応じて、内部電源を発生する内部電源発生回路と、を備える。

(もっと読む)

半導体集積回路装置

【課題】部品点数を増加させることなく、低コストでかつ効率的に半導体集積回路装置の高信頼性化を実現させる。

【解決手段】ユーザプログラムの実行時において、周期タイマ2からタイマカウンタ信号が出力されると、CPUコア6,7はASEメモリ3に格納されたテスト用プログラムを実行し、そのチェック結果をトレースメモリ11に格納する。デバッグ回路10は、トレースメモリ11に格納されたチェック結果のコンペア処理を行い、CPUコア6,7が正常か否かを判定する。正常の場合、CPUコア6,7は、再びユーザプログラムを実行する。異常の場合、デバッグ回路10は、状態信号をシステム停止回路12に出力する。この状態信号を受けると、システム停止回路12は、動作制御信号をCPUコア6,7にそれぞれ出力し、半導体集積回路装置1の再起動処理が行われる。

(もっと読む)

半導体装置

【課題】誤ってテストモードにエントリされたとしても、正常に動作させる。

【解決手段】半導体装置は、内部回路をテストするテスト回路2に対してテストを開始させるテストモードエントリ信号が入力されたことに応じて、内部のラッチ10をセットすることにより、テスト回路2に対し、テスト回路2の駆動を許可するテストイネーブル信号をラッチ10から出力するテスト信号発生回路1を備える。テスト信号発生回路1が、ラッチ10がテストイネーブル信号を出力している場合、テストイネーブル信号を遅延させて、ラッチ10をリセットするリセット信号を生成するリセット信号生成回路30と、ラッチ10がテストイネーブル信号を出力している場合に、外部から供給されるトグル信号に基づいて、リセット信号生成回路30によるリセット信号を生成する動作を初期化する遅延初期化信号を出力する遅延初期化回路40と、を有している。

(もっと読む)

ヒューズ回路及びトリミング良否判定方法

【課題】ヒューズ開口部の端部に必ず切断すべきヒューズを配設することにより、レーザー照射後のその切断/未切断をもって、端部のポリイミド膜の膜厚の良否を容易に判定する。

【解決手段】ヒューズ回路は、ヒューズ開口部FAの、ポリイミド膜の厚さが不本意に厚く残りやすい端部に配設された2つの切断確認用ヒューズ1a,1bと、ポリイミド膜の厚さ変動が端部に比べ少ない領域RAに配設された複数の実使用ヒューズ7a〜7dと、2つの切断確認用ヒューズ1a,1bからの信号を入力して当該ヒューズ1a,1bが確実に切断されているかを判定するヒューズ未切断判定回路2と、を備えている。なお、ヒューズ未切断判定回路2は、更にテストモード信号を入力すると共に、出力回路(例えばDQ回路)に判定結果を出力している。

(もっと読む)

半導体集積回路

【課題】テスト時の消費電力を低減することができる半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路100は、フリップフロップFF、制御回路10及び排他的論理和ブロックを有する。フリップフロップFFは、テスト入力Tにテストデータ信号TINが入力する。排他的論理和ブロック20は、一方の入力がフリップフロップFFのテスト入力Tと接続され、他方の入力がフリップフロップFFの出力Qと接続される。制御回路10は、排他的論理和ブロック20の出力XORとクロック信号CLKとが入力し、排他的論理和ブロックの出力XORの値に応じてフリップフロップFFへのクロック信号CLKの出力を制御する。

(もっと読む)

半導体集積回路および半導体集積回路のテスト方法

【課題】小さな回路規模で複数のパラレルシリアル変換回路を確実にテストすることが可能な半導体集積回路等を提供する。

【解決手段】第1および第2のパラレルシリアル変換回路と、第1および第2のテスト用パラレルデータ列を生成するテスト用パラレルデータ列生成回路と、第1および第2のパラレルシリアル変換回路が変換した第1および第2のシリアルデータビットの一致/不一致を検出する検出回路とを備えた半導体集積回路において、テスト用のパラレルデータ列生成回路が共通のテスト用パラレルデータ列を構成するそれぞれのパラレルデータのビットを第1のビット数だけシフトして第2のテスト用パラレルデータ列を生成するパラレルビットシフト回路を含み、検出回路が第1のシリアルデータと第2のシリアルデータとの一方のビットをシフトして比較回路に入力されるタイミングをそろえるシリアルビットシフト回路とを含む。

(もっと読む)

1 - 20 / 655

[ Back to top ]