Fターム[5F038DT16]の内容

Fターム[5F038DT16]の下位に属するFターム

結果の記憶 (275)

回路切換(テスト結果による) (426)

表示 (135)

Fターム[5F038DT16]に分類される特許

1 - 20 / 115

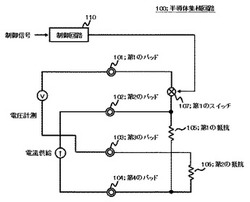

半導体集積回路

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】複数の出力トランジスタが並列接続された構成を備え、出力トランジスタを含む各電流経路間で分担電流を高精度に均一に揃えることができる半導体装置、および当該半導体装置の駆動方法を提供する。

【解決手段】互いに並列に接続された複数の出力トランジスタを備える半導体装置であって、出力トランジスタごとに設けられ第1の制御信号を供給する駆動回路と、第1の制御信号に含める出力トランジスタのコンダクタンスの情報を有するデータを記憶するメモリと、メモリにデータを入力するための第1の外部入力端子と、各駆動回路に出力トランジスタを1つずつ入れ替わり導通させる第2の制御信号を入力するための第2の外部入力端子とを備え、各駆動回路は、メモリに記憶されている駆動対象の出力トランジスタについてのデータを読み出して、コンダクタンスの情報を含む第1の制御信号を生成する。

(もっと読む)

集積回路への電力供給方法、システム及びそれに使用される集積回路

【課題】半導体チップに供給する電圧を、公称最大動作電圧を超えて増加可能にする電力供給方法の提供。

【解決手段】組立てパッケージ内に所定の最大動作電圧を超えない電源電圧で動作するようにされた少なくとも一つの電力入力を有する複数の論理回路16を有するチップ4を有する集積回路2への電力供給方法は、論理回路の選択された1つの論理回路の電力入力において、論理回路の1つにおける電力入力においてチップ内に位置する計測点61で第2の電源電圧を直接測定すること、および計測点と選択された1つの論理回路の電源入力間の電圧降下に基づいて第1の電源電圧を決定するステップと、第1の電源電圧を、論理回路の選択された1つにおける所定の最大動作電圧に調節されるような値を有する基準電圧に調節するステップ、を備える。

(もっと読む)

検証装置、検証方法及びプログラム

【課題】検証する範囲を少なくして、検証コストや検証時間の増大を抑制する。

【解決手段】抽出部12が、第1のクロック信号で動作する回路部21と、第2のクロック信号で動作する回路部22とを含む検証対象回路(論理回路20)から、ハンドシェイクの手順に従って回路部21と回路部22間でのデータの送受信を行うハンドシェイク部23を抽出し、検証部13が抽出されたハンドシェイク部23の信号が、その手順を満たすかを検証し、手順を満たさない信号があるとき、回路部21と回路部22のうち当該信号を出力する側で、当該信号が手順を満たさなくなる条件が回路動作時に起こり得るか検証する。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】ジッタ耐性検査における検査コストの低減を図りつつ、入力される主信号の特性劣化を抑制できる半導体集積回路を提供する。

【解決手段】半導体集積回路101は、主信号にジッタ信号が付加されてなる検査信号を生成する機能を有し、ジッタ信号の基となる信号を生成するジッタ信号生成部50と、電源線Vccと接地線GNDとの間に介在し、電源線Vccからの電力供給を受けて外部からの主信号を増幅して出力するバッファ回路10と、電源線Vccとバッファ回路10との間およびバッファ回路10と接地線GNDとの間に介在し電源線Vccからバッファ回路10への供給電力をジッタ信号の基となる信号の大きさに基づいて変化させることにより主信号にジッタ信号を付加するジッタ信号付加部30とを備える。

(もっと読む)

半導体素子の破壊を検知する検知回路

【課題】監視対象の素子の破壊を直接的に検知することを可能にする。

【解決手段】監視対象の半導体素子近傍にモニタ用配線を敷設する一方、所定のクロックを出力するクロック出力手段を当該モニタ用配線の一端に接続し、同モニタ用配線の他端に監視手段を接続する。そして、クロック出力手段からモニタ用配線へ出力されるクロックを伝播を監視手段に監視させ、クロックの伝播が途絶えたことを検出した場合に、監視対象の半導体素子の破壊が生じた旨を通知する破壊通知信号を出力させる。

(もっと読む)

半導体集積回路および電源供給方法

【課題】チップ内でデバイス特性にバラツキがあっても、消費電力を低減させることのできる半導体集積回路および電源供給方法を提供する。

【解決手段】実施形態の半導体集積回路1は、それぞれの領域に半導体デバイスが配置された領域1および領域2を有し、電源供給手段である電源端子T1、T2が、領域1、領域2それぞれに個別に電源を供給する。領域1にはデバイス特性測定回路ROSC1が配置され、領域2にはデバイス特性測定回路ROSC2が配置されている。

(もっと読む)

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】コンタクトとゲート電極との間隔を効率よく測定できるようにする。

【解決手段】第1ゲート電極310と第1コンタクト320の距離と、リーク電流量の大きさの相関を示す変換用データを予め準備しておく。そして、第1ゲート電極310と第1コンタクト320の間のリーク電流量を測定し、測定したリーク電流量を、上記した変換用データを用いて第1ゲート電極310と第1コンタクト320の距離に変換する。そして、第1ゲート電極310と第1コンタクト320の距離の測定値と、この距離の設計値との差から、第1ゲート電極310を形成するための露光処理と、第1コンタクト320を形成するための露光処理と、の間の重ねあわせ誤差を測定することができる。

(もっと読む)

電源状態判定回路を有する集積回路

【課題】電源オープン検出回路の動作マージンを大きくする。

【解決手段】電源端子とグランド端子と入力端子と内部回路とが形成された集積回路において,入力端子と電源端子との間に設けられ,入力端子から前記電源端子への方向の一方向性回路と,電源端子が外部電源と接続しているか否かを検出して電源オープン検出信号を出力する電源状態判定回路とを有する。一方向性回路は,電源端子の電圧がゲートに印加される第1のトランジスタと,第1のトランジスタに直列に接続された第2のトランジスタとを有し,入力端子には外部電源の電圧が入力される。

(もっと読む)

集積回路およびウェーハを試験する無線周波数技術構造および方法

【課題】集積回路を有するウェーハの無線試験を行うためのウェーハ上に形成された試験回路を含む装置および方法を提供する。

【解決手段】ウェーハ16の外部にある試験ユニット12、および集積回路を含むウェーハ上に製造された少なくとも1つの試験回路14を含む。試験ユニット12は、RF信号を送信し、試験回路14に電力を供給する。試験回路14は、可変リング発振器を含み、集積回路の公称動作周波数での一連のパラメータ試験を実行し、試験結果を分析のために試験ユニット12に送信する。

(もっと読む)

半導体集積回路

【課題】一部の回路領域の電源を遮断した時にその回路領域からの出力を固定化するアイソレータセルの回路規模の低減、動作の高速化および誤設定が発生の低減および修正可能なLSIの実現。

【解決手段】複数の回路領域12A,12B,12Cと、1つの回路領域へ電源供給するか否かを切り替える電源スイッチTrBと、電源スイッチの制御を行う電源制御回路13と、1つの回路領域から他の領域への出力が入力される複数のフリップフロップを有するクランプスキャンチェーンSFF21と、クランプスキャンチェーンのフリップフロップを所定の出力状態に設定するクランプデータ制御回路30,18,21,23と、を備える半導体集積回路。

(もっと読む)

半導体集積回路装置

【課題】レギュレータ内蔵の半導体集積回路(チップ)に対して、スキャン試験を行う場合、チップの活性化率が非常に高くなるため、IRドロップにより、正しいテスト結果を得ることが出来ない。

【解決手段】チップの有するスキャンチェイン群を複数の回路ブロックに分割する。スキャン試験を行う前に、該回路ブロックへ電圧を供給し、各回路ブロックの入力電圧と予め定められる基準電圧を比較し、入力電圧が低い回路ブロックが存在する場合、いずれかの回路ブロックへのテストクロックの供給を遮断する。これにより、レギュレータの電力駆動力に応じた分だけの回路ブロックをスキャン試験することが可能となる。

(もっと読む)

半導体集積回路および電子機器

【課題】不揮発性記憶素子にフューズ素子を用いた半導体集積回路において、目的とするデータと、検査データとしての目的とするデータの論理否定データとを記憶し、フューズ素子の不可逆性を利用することで、記憶回路と検証回路の回路規模をあまり大きくすることなく、またデータ検証の処理時間の増大を招くことなく、記憶データの信頼性と正真性を保証する。

【解決手段】記憶すべき情報を示す特定データを不可逆的に記憶する不揮発性記憶回路100aを有する半導体集積回路100において、該不揮発性記憶回路100aを、該特定データの非反転データを記憶する第1の記憶回路101と、該特定データの反転データを記憶する第2の記憶回路102とを有する構成とした。

(もっと読む)

半導体装置および半導体装置の検査方法

【課題】検査用回路を備えた半導体装置において、所望のタイミングで検査対象回路部の動作を確認することができない

【解決手段】本発明の半導体装置は、検査対象回路部と、検査回路部を有し、検査回路部は、信号入力部と、比較部と、制御回路部を備え、制御回路部は、信号入力部と比較部と検査対象回路部に接続され、信号入力部は、検査用信号または検査期待値を取得し、検査用信号を制御回路部に送出し、制御回路部は、検査用信号を検査対象回路部に送出し、検査用信号に基づいて検査対象回路部が出力する動作信号を取得して比較部に送出し、比較部は、同期信号に基づいて検査期待値と動作信号を比較した比較結果を出力する。

(もっと読む)

半導体装置の製造方法、半導体装置の検査方法、及び半導体装置

【課題】半導体装置の検査において、電極パッドの配列、スクライブ領域の幅に影響されることなくプローブカードを共有化し、プローブカードの製作費用を低減する。

【解決手段】基板20はチップ領域100、スクライブ領域200および電極パッド300を備えている。チップ領域100は基板20上の第1の方向に沿って、スクライブ領域200により互いに分離されるように並んでいる。電極パッド300は第1の方向に沿って周期性をもって配列している。接続用電極パッド320はチップ領域100に形成され、ダミー電極パッド340は少なくともスクライブ領域200に形成されている。電極パッド300の間隔はスクライブ領域200の幅よりも狭い。電極パッド300の配列と平行な方向における、チップ領域100とスクライブ領域200を合わせた幅は、電極パッド300間隔の整数倍である。

(もっと読む)

半導体装置

【課題】 多相クロック方式を採用している半導体装置の故障位置及び原因解析を容易化する。

【解決手段】 集積回路の動作の不具合の発生を検知するエラー検出部ERDと、2相以上のクロックの所定期間の位相状態の情報を保持するクロック状態保持部CLKSTと、エラー検出部が集積回路の動作の不具合の発生を検出するのに応じて、2相以上のクロックの所定期間の位相状態の情報を出力する出力部SCOUTとを有する。

(もっと読む)

劣化検出回路

【課題】半導体集積回路の素子(特にトランジスタ)の劣化を正確に測定する。

【解決手段】リングオシレータ(1)の周波数情報を出力する周波数測定器(2)と、リングオシレータ(1)を良否判定する判定回路(7)とを具備する劣化検出回路(8)を構成する。判定回路(7)は、周波数情報と、リングオシレータ(1)の動作環境と発振周波数との関連性を示す環境依存特性情報(15)(16)(17)と、リングオシレータ(1)の発振周波数として許容される許容範囲情報(6)と、リングオシレータ(1)の動作時の環境特定情報(13)(14)とを受けとる。そして、環境特定情報(13)(14)と環境依存特性情報(15)(16)(17)とに基づいてリングオシレータ(1)の理想的な発振周波数である理想周波数を算出し、周波数情報が、許容範囲情報(6)に対応する条件に含まれているか否かを判定する。

(もっと読む)

半導体集積回路及び電子機器

【課題】システマテックばらつきとランダムばらつきの両方を考慮した適応型電圧スケーリング技術を実現することにある。

【解決手段】適応型電圧スケーリングを実施するシステム構成において、プロセスばらつきの種類毎に最適な検出回路を設置する。すなわち、システマテックばらつき検出用にゲートディレイの平均値に対する相対値を生成する第1測定回路(100)、及び、ランダムばらつき検出用にゲートディレイの標準偏差に対する相対値を生成する第2測定回路(200)を別々に設置する。夫々の測定回路で生成された相対値に基づいて電源電圧を決定するための制御情報(VCNT)を生成する。これを生成するときは例えばテーブルデータを参照する。

(もっと読む)

1 - 20 / 115

[ Back to top ]