Fターム[5F038EZ06]の内容

Fターム[5F038EZ06]に分類される特許

141 - 160 / 754

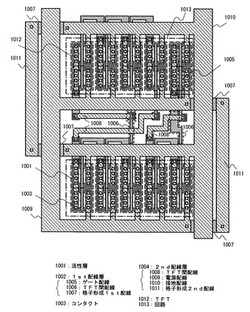

半導体装置

【課題】機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置を提供する。

【解決手段】機能回路に電源電圧を供給する電源配線1009及び接地電圧を供給する接地配線1010が格子状に配置されている半導体装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

薄膜トランジスタ、表示装置及び薄膜トランジスタの作製方法

【課題】チャネル形成領域に結晶化率の高い領域を配し、ソースとドレインの間に高抵抗な領域を配し、電界効果移動度が高くオン電流が大きい薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタの下地層に「結晶核の生成を抑制する不純物」を含ませ、または下地層の表面に「結晶核の生成を抑制する不純物」を存在させ、下地層上に設けられた第1の配線層と、第1の配線層に少なくとも一部が接する不純物半導体層と、少なくとも一部が不純物半導体層を介して第1の配線層と電気的に接続される半導体層と、半導体層上に設けられた第1の絶縁層と、少なくとも半導体層と第1の絶縁層を覆って設けられた第2の絶縁層と、第2の絶縁層上であって、不純物半導体層の少なくとも一部、及び不純物半導体層によって形成されるソース領域とドレイン領域の間に重畳して設けられた第2の配線層と、を有する薄膜トランジスタとする。

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】スタンバイ時における半導体装置の消費電力を低減する。

【解決手段】電源線VDDTL,VSSTL間に接続された回路ブロック10Aと、電源線VDDTL,VSSL間又は電源線VDDL,VSSTL間に接続された回路ブロック10Aの出力信号を受ける論理回路10B−1と、電源線VDDL,VSSL間に接続された論理回路10B−1の出力信号を受ける回路ブロック20と、を備える。電源線VDDTL,VSSTL間には、アクティブ状態においては第1の電圧、スタンバイ状態においては第1の電圧よりも低い第2の電圧が供給され、電源線VDDL,VSSL間には、アクティブ状態及びスタンバイ状態のいずれにおいても第1の電圧が供給される。これにより、サブシュレッショルド電流低減を維持しつつ、クリティカルパスの高速化を実現することが可能となる。

(もっと読む)

ESD保護素子、半導体装置およびプラズマディスプレイ装置

【課題】 製造コストを上昇させることなくSOI構造の高耐圧半導体集積回路装置に組み込むことができるとともに、チップ面積の増大を抑制できるESD保護素子を提供する。

【解決手段】

ESD保護素子は、埋め込み絶縁膜2上に形成され、素子分離領域17で囲まれた第1導電型半導体層3、半導体層3に形成された第1導電型第1半導体領域8、第1導電型第1半導体領域8から離間して半導体層3に形成された第2導電型第1半導体領域16、第2導電型第1半導体領域16に形成され、それより高不純物濃度の第2導電型第2半導体領域10、第2導電型第2半導体領域10に形成された高不純物濃度の第1導電型第2半導体領域9からなる構造を有している。また、第1電極12および第2電極13は高耐圧半導体回路に電気的に接続され、第2導電型第1および第2半導体領域16、10は電気的にフローティング状態となっている。

(もっと読む)

半導体装置

【課題】待機電力を十分に低減した新たな半導体装置を提供することを目的の一とする。

【解決手段】第1の電源端子と、第2の電源端子と、酸化物半導体材料を用いたスイッチングトランジスタと、集積回路と、を有し、前記第1の電源端子と、前記スイッチングトランジスタのソース端子またはドレイン端子の一方は電気的に接続し、前記スイッチングトランジスタのソース端子またはドレイン端子の他方と、前記集積回路の端子の一は電気的に接続し、前記集積回路の端子の他の一と、前記第2の電源端子は電気的に接続した半導体装置である。

(もっと読む)

半導体集積回路装置

【課題】半導体プロセスを用いて、雰囲気温度から駆動電圧を得る半導体集積回路装置を提供する。

【解決手段】ダイオード接続された整流素子(トランジスタ3)と、一端が前記整流素子の一端に接続され、他端が接地電位に接続された電圧発生源としての抵抗素子(抵抗1)と、から構成される駆動電圧発生回路(単位セル31)から成り、前記抵抗素子(抵抗1)が発生する電圧を駆動電圧として前記整流素子(トランジスタ3)の他端に出力することを特徴とする半導体集積回路装置。

(もっと読む)

横型半導体装置

【課題】SOI基板のシリコン半導体層を薄膜化することによって横型の半導体装置の耐圧を高め、しかも大電流の通電時にシリコン半導体層が熱破壊されるまでの時間が短くなることを防止する。

【解決手段】IGBT1では、支持基板11と埋め込み酸化シリコン層12とシリコン半導体層13と絶縁層23とが順に形成されている。シリコン半導体層13は、エミッタ電極20に接しているエミッタ領域14と、コレクタ電極21に接しているコレクタ領域15と、ボディ領域17及びバッファ領域19の一部とドリフト領域16とからなる中央半導体領域とを備えている。絶縁層23の一部は、酸化シリコンよりも熱伝導性が高い材料で形成されているとともにドリフト領域16の真上に広がっている高熱伝導層27である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】SiGe等の半導体膜が形成された領域と、酸化シリコン膜から成るゲート絶縁膜が形成された領域とが同一基板上に形成される際に、ゲート絶縁膜を精度良く形成する。

【解決手段】基板10を熱酸化することにより、第1素子領域101及び第2素子領域201に、第1ゲート絶縁膜110及び第2ゲート絶縁膜210を形成し、かつ第3素子領域301及び第4素子領域401それぞれに位置する基板10に熱酸化膜を形成する。次いで、第4素子領域401に位置する熱酸化膜を除去する。次いで、第4素子領域401に位置する基板10上に半導体膜414を成膜する。次いで、第3素子領域301に位置する熱酸化膜を除去する。次いで、第4素子領域401に位置する半導体膜414上、及び第3素子領域301に位置する基板10上に第3ゲート絶縁膜310及び第4ゲート絶縁膜410を形成する。

(もっと読む)

不揮発性のラッチ回路及び論理回路並びにそれを用いた半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力が第2の素子の入力に電気的に接続され、第2の素子の出力が第1の素子の入力に電気的に接続されるループ構造を有するラッチ部と、ラッチ部のデータを保持するデータ保持部とを有し、このラッチ部とデータ保持部とにより不揮発性のラッチ回路が構成される。データ保持部は、チャネル形成領域を構成する半導体材料として酸化物半導体を用いたトランジスタをスイッチング素子として用いている。またこのトランジスタのソース電極又はドレイン電極に電気的に接続されたインバータを有している。上記トランジスタを用いて、ラッチ部に保持されているデータをインバータのゲート容量あるいは別に用意した容量に書き込むことができる。

(もっと読む)

表示装置及びその製造方法

【課題】絶縁層による光透過率の低下を防止することができる表示装置及びその製造方法を提供する。

【解決手段】表示装置は、第1基板110上に位置する第1絶縁層116と、第1絶縁層116上に位置する下部電極118bと、下部電極118bの上面及び側面を囲むように形成された誘電体層120aと、誘電体層120a上に位置する上部電極122aと、を備える。第1絶縁層116は、誘電体層120aに対してエッチング選択比を有してもよい。第1絶縁層116は、シリコン酸化物を含み、誘電体層120aは、シリコン窒化物を含んでもよい。

(もっと読む)

平板表示装置及びその製造方法

【課題】薄膜トランジスタ及びMOS(Metal−Oxide−Semiconductor)構造のキャパシタを備える平板表示装置及びその製造方法を提供する。

【解決手段】第1領域の基板上に半導体で形成された活性層と、第2領域の基板上に半導体で形成された下部電極と、活性層及び下部電極を含む上部に形成された第1絶縁層と、活性層上の第1絶縁層上に第1導電層及び第2導電層で形成されたゲート電極と、下部電極上の第1絶縁層上に第1導電層で形成された上部電極と、ゲート電極及び上部電極を含む上部に形成され、活性層及び上部電極が露出するようにパターニングされた第2絶縁層と、露出した活性層に接続されるソース電極及びドレイン電極とを備える。

(もっと読む)

半導体装置

【課題】プロセスの複雑化を招くことなく、サイリスタとしての機能を実現することの出来る半導体装置を提供することを課題の一とする。

【解決手段】リセット動作及び初期化動作により所定の電位が記憶されたメモリ回路を有する半導体装置において、トリガー信号の供給に応じて、メモリ回路の書き換えが行われる回路を設ける構成とする。そして、メモリ回路の書き換えにより、半導体装置に流れる電流を負荷に流す構成とすることで、サイリスタとしての機能を実現しうる半導体装置とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 アバランシェ耐量が高く、保護する高耐圧トランジスタと同製造工程を用いて形成できる高耐圧ESD保護ダイオードを提供する。

【解決手段】 カソード領域8を構成するN型低濃度半導体基板1とアノード領域7を構成するP型低濃度拡散領域14から形成されるPN接合部の基板表面上に、ゲート酸化膜12を形成し、ゲート酸化膜12とフィールド酸化膜4にまたがって設けられたゲート電極13をゲートプラグ28を介してアノード電極20と電気的に接続することを特徴とする構造により、アバランシェ降伏時にPN接合における電界が緩和し、高アバランシェ耐量を得る。またフィールド酸化膜4の長さを変化させることで、耐圧を調整できる。

(もっと読む)

非線形素子、該非線形素子を有する表示装置および該表示装置を有する電子機器

【課題】酸化物半導体を用いた整流特性の良い非線形素子(例えば、ダイオード)を提供する。

【解決手段】水素濃度が5×1019/cm3以下である酸化物半導体を有するトランジスタにおいて、酸化物半導体に接するソース電極の仕事関数φmsと、酸化物半導体に接するドレイン電極の仕事関数φmdと、酸化物半導体の電子親和力χが、φms>χ≧φmdの関係になるように構成し、トランジスタのゲートとドレインを電気的に接続することで、整流特性の良い非線形素子を実現することができる。

(もっと読む)

酸化物半導体の評価方法、半導体装置の作製方法

【課題】シリコン半導体の原理は解明されていることが多いが、酸化物半導体の原理は不明な部分が未だに多いため、酸化物半導体の評価方法も確立されていなかった。そこで、新たなたな酸化物半導体の評価方法を提供することを課題とする。

【解決手段】キャリア密度の量を評価するとともに水素濃度の量も評価する。具体的にはMOSキャパシタ(ダイオード又はトライオード)を作製し、当該MOSキャパシタのCV特性を取得する。そして、取得したCV特性からキャリア密度を見積もる。

(もっと読む)

トランス素子とその製造方法

【課題】マイクロトランス素子を小型化することと、マイクロトランス素子の特性を確保することとを両立する。

【解決手段】 トランス素子は、第1導電型の半導体層を備えた半導体基板と、第1導電型の半導体層の表面側に設けられた第2導電型の半導体層からなる半導体層コイルと、半導体層コイルと並列に接続されており、半導体層コイルのコイル配線間の第1導電型の半導体層に形成されたトレンチと、トレンチ内面に設けられたトレンチ絶縁膜と、そのトレンチ絶縁膜によって被覆されている導電層有するトレンチコイルと、第1導電型の半導体層の表面側に設けられ、半導体層コイルおよびトレンチコイルを被覆するコイル絶縁層と、コイル絶縁層の表面に設けられており、半導体層コイルおよびトレンチコイルと対向している金属層コイルとを備えている。並列接続された半導体層コイルとトレンチコイルによって、第1コイルの抵抗が低減し、トランス素子の小型化と特性確保を両立できる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板のクラックを検知することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1導電型の半導体基板10と、外部に露出した第1露出部26及び第2露出部26とを具備する。半導体基板10は、第1導電型の第1半導体領域12と、第1導電型の逆の第2導電型の第2半導体領域13Aとを含む。第1半導体領域12と第2半導体領域13Aとの間にPNジャンクションが形成される。第1露出部26及び第2露出部26を介してPNジャンクションのダイオード特性が計測可能なように、第1半導体領域12及び第2半導体領域13Aがそれぞれ第1露出部26及び第2露出部26に接続される。第2半導体領域13Aは、半導体基板10の外周11に沿って延びる帯状に形成される。第2半導体領域13Aの外側端は、半導体基板10の外周端より内側に位置する。

(もっと読む)

半導体装置

【課題】絶縁層上の半導体層に形成された部分空乏型のトランジスターにおいて、高いON/OFF比と、安定動作を同時に実現できるようにした半導体装置を提供する。

【解決手段】絶縁層上の半導体層に形成された部分空乏型の第1トランジスターと、前記半導体層に形成された第2トランジスターと、前記半導体層に形成された第3トランジスターと、を備え、前記第1トランジスターは、第1導電型の第1ソース又は第1ドレインを有し、前記第2トランジスターは、第1導電型の第2ソース又は第2ドレインを有し、前記第3トランジスターは、第2導電型の第3ソース又は第3ドレインを有し、前記第1ソース又は第1ドレインの一方と、前記第2ソース又は第2ドレインの一方とが電気的に接続され、前記第2ソース又は第2ドレインの他方と、前記第1トランジスターのボディ領域と、前記第3ソース又は第3ドレインの一方とが互いに電気的に接続されている。

(もっと読む)

半導体装置の製造方法及び半導体装置並びにその半導体装置を内蔵する多層基板

【課題】dv/dtサージにより、寄生容量を充放電する変位電流の発生を抑制できる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】低電位基準回路部LV、高電位基準回路部HV、レベルシフト回路部LSを形成したSOI基板の半導体層の主面上にサポート部材を貼り付け、支持基板を除去する。次いで、回路部と対向するように絶縁部材を半導体層の裏面上に固定した後、サポート部材を剥がす工程と、チップ内にLV,HV,LSが含まれるように絶縁部材の固定された半導体層をダイシングする工程を経る。そして、サポート部材を剥がし、チップ化した半導体層を、絶縁部材を挟んで、第1のリードがLVと、第2のリードがHVと対向するように、第1リード及び第2リード上に固定するとともに、第1のリードとLVにおける第1の電位が印加される部位を電気的に接続し、第2のリードとHVにおける第2の電位が印加される部位を電気的に接続する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を用いた、表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

141 - 160 / 754

[ Back to top ]