Fターム[5F038EZ06]の内容

Fターム[5F038EZ06]に分類される特許

201 - 220 / 754

半導体装置

【課題】信側インダクタ及び受信側インダクタを設けても半導体装置が大型化することを抑制する。

【解決手段】第1半導体チップ10は、第1基板102、第1回路100、多層配線層400、第1インダクタ310及び第2インダクタ320を備える。第1回路100は、第1基板102に形成されている。多層配線層400は、第1基板102上に形成されている。第1インダクタ310は、多層配線層400に形成され、第1基板102と平行な面内で巻かれている。第2インダクタ320は、多層配線層400に形成され、第1基板102と平行な面内で巻かれており、平面視において第1インダクタ310と重なっている。第1回路100は、第1インダクタ310及び第2インダクタ320の一方に接続されている。そして平面視において、第1回路100の少なくとも一部は、第1インダクタ310及び第2インダクタ320の内側に位置している。

(もっと読む)

半導体装置およびその製造方法

【課題】ESDサージ耐量を向上できるようにする。

【解決手段】LDMOSにおいて、n+型ドレイン領域5を囲むように、n型基板1よりも高濃度に形成され、n+型ドレイン領域5に近づくほど高濃度となるn型領域6を配置する。さらに、n+型ソース領域8に隣接配置されるp+型コンタクト領域9がn+型ソース領域8の下部まで入り込むようにし、n+型ソース領域8、p型ベース領域7及びn型基板1によって形成される寄生トランジスタがオンし難くなるようにする。

(もっと読む)

半導体素子、半導体装置および半導体素子の製造方法

【課題】ESD保護素子が集積された回路全体の製造コストを低減する。

【解決手段】ESD保護素子100は、nチャネルGGFET構造を有している。ESD保護素子100において、第1p+低抵抗領域41は、第1pウエル領域4の一部に、第1p++コンタクト領域5とその下の領域、n++ソース領域8とその下の領域、第1LDD領域6とその下の領域、第1ゲート絶縁膜12の下の領域、第2LDD領域7とその下の領域、およびn++ドレイン領域9の一部とその下の領域に設けられている。第1p+低抵抗領域41のn++ドレイン領域9側の端部から、第1ゲート電極13のn++ドレイン領域9側の端部までの第1エクステンション距離(LBP1)は、0〜0.3μmの範囲内にある。ESD保護素子100の第1p+低抵抗領域41は、高耐圧デバイスの低抵抗領域と同時に形成される。

(もっと読む)

保護回路、半導体装置、光電変換装置および電子機器

【課題】ESD対策をした保護回路および半導体装置を提供する。

【解決手段】集積回路と電気的に接続された信号線と、信号線と第1の電源線との間に設けられた第1のダイオード、及び第1のダイオードと並列に設けられた第2のダイオードと、第1の電源線と第2の電源線との間に設けられた第3のダイオードとを有し、第1のダイオードは、トランジスタをダイオード接続することによって形成されたダイオードであり、第2のダイオードはPIN接合又はPN接合を有するダイオードである保護回路。上記保護回路は、特に薄膜トランジスタを用いて作製される半導体装置に用いられることで効果を発揮する。

(もっと読む)

有機電界発光表示装置及びその製造方法

【課題】キャパシタの表面積を増大させて容量が増加した有機電界発光表示装置及びその製造方法。

【解決手段】薄膜トランジスタ及びキャパシタ領域を含む基板と;バッファー層と;トランジスタ領域に位置する金属触媒を利用して結晶化した半導体層パターンと;ゲート絶縁膜と;前記パターンの一定領域に対応されるゲート電極及びキャパシタ領域のキャパシタ下部電極と;層間絶縁膜と;前記パターンと一部が連結されるソース/ドレイン電極及びキャパシタ下部電極に対応される上部電極と;同じく層間絶縁膜上のソース/ドレイン電極と電気的に連結される第1電極と;発光層を含む有機膜層;及び第2電極をこの順で含み、キャパシタ領域に対応されるバッファー層、ゲート絶縁膜、及び層間絶縁膜の一定領域、キャパシタ下部電極、及びキャパシタ上部電極の表面には半導体層パターンを形成する結晶粒の結晶粒界及びシードの形状と一致する形状の突出部を形成する。

(もっと読む)

半導体装置、およびそれを用いたプラズマディスプレイ駆動用半導体装置

【課題】高耐圧IC向けの従来のESD保護回路では、出力段回路等の保護対象回路のESD耐量を向上するために、ESD向けの素子設計が必要となるといった課題があった。

【解決手段】本発明では、出力段回路には、通常のラッチアップ動作対策のあるIGBTを用い、ESDクランプ回路には、ラッチアップ防止層の不純物濃度を低濃度または削除した出力段回路素子よりラッチアップのしやすいIGBTを使用する。ラッチアップ防止層以外の構造は従来技術と同一でよい。

【効果】本発明のESD保護回路ではIGBTのラッチアップ動作を用いることによりESD耐量が向上する。更に、従来と比較してESD保護回路のサイズの低減が実現できる。また、ESD向けデバイスの設計を省略することが可能となる。

(もっと読む)

半導体装置とその製造方法

【課題】高サージ耐量を維持しつつ、電気容量と降伏電圧のトレードオフ関係を解消できる半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板1の一方の面上に形成された絶縁膜2上に、互いに異なる導電型の第1の低濃度半導体層(p−型の半導体層3)と第2の低濃度半導体層(n−型の半導体層4)が積層されている。また、第2の低濃度半導体層の表面から深さ方向へ、同じ導電型の第1の高濃度半導体層(n+型の半導体層5)と第3の高濃度半導体層(n+型の半導体層7)が互いに対向して延在しており、それらとは異なる導電型の第2の高濃度半導体層(p+型の半導体層6)が第3の高濃度半導体層の層内に埋設されている。さらに、第1と第2の低濃度半導体層それぞれの不純物濃度と厚みが、印加電圧のない状態で、第1と第2の低濃度半導体層が空乏層で覆われるように設定されている。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】TDDB寿命が改善された容量素子を有する半導体集積回路装置を提供すること。

【解決手段】半導体集積回路装置1は、基板平面に対して突起する第1半導体層を有する第1電極4と、第1電極4の少なくとも一部の側面に形成された側面絶縁膜5と、第1電極4上及び側面絶縁膜5上に形成された上面絶縁膜6と、側面絶縁膜5及び上面絶縁膜6を覆う第2電極7と、を備える。第1電極4、側面絶縁膜5及び第2電極7は容量素子を形成する。上面絶縁膜6の第1電極4と第2電極7間の厚さは、側面絶縁膜5の第1電極4と第2電極7間の厚さよりも厚い。

(もっと読む)

集積回路のためのオンチップ電圧変換装置およびシステム

【課題】 多数の電圧ドメインを有する集積回路デバイスおよびシステムのための改良された電圧変換システムを提供する。

【解決手段】 集積回路のためのオンチップ電圧変換装置は、第1のキャパシタと、この第1のキャパシタの第1の電極を第1の電圧ドメインの低側電圧レールに選択的に結合するように構成された第1のNFETデバイスと、第1のキャパシタの第1の電極を第1の電圧ドメインの高側電圧レールに選択的に結合するように構成された第1のPFETデバイスと、第1のキャパシタの第2の電極を第2の電圧ドメインの低側電圧レールに選択的に結合するように構成された第2のNFETデバイスであって、第2の電圧ドメインの低側電圧レールが第1の電圧ドメインの高側電圧レールに対応する、第2のNFETデバイスと、第1のキャパシタの第2の電極を第2の電圧ドメインの高側電圧レールに選択的に結合するように構成された第2のPFETデバイスと、を含む。

(もっと読む)

表示装置

【課題】 絶縁破壊をより効果的に防ぐことができる保護回路を用いた、半導体表示装置

の提供を課題とする。

【解決手段】 本発明では、保護ダイオードとして用いるTFTを覆って第1の層間絶縁

膜が形成されており、更に該第1の層間絶縁膜上に形成された配線を覆って、絶縁性の塗

布膜である第2の層間絶縁膜が形成されている場合に、第2の層間絶縁膜の表面に蓄積し

た電荷を放電させる経路を確保するために、該TFTと他の半導体素子とを接続するため

の配線を、第2の層間絶縁膜上に接するように形成する。なお保護ダイオードとして用い

るTFTは、その第1の端子または第2の端子のいずれか一方がゲート電極と接続された

、所謂ダイオード接続のTFTである。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率でありかつリーク電流を低減することが可能なゲート絶縁膜を備えた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板11上に設けられ、かつランタンアルミシリコン酸化物若しくは酸窒化物を含む第1の誘電体膜23と、第1の誘電体膜23上に設けられ、かつハフニウム(Hf)、ジルコニウム(Zr)、チタン(Ti)、及び希土類金属のうち少なくとも1つを含む酸化物若しくは酸窒化物を含む第2の誘電体膜24と、第2の誘電体膜24上に設けられた電極14とを含む。

(もっと読む)

半導体回路

【課題】耐放射線特性の優れた半導体回路を提供することを目的とする。

【解決手段】複数のpMOSトランジスタ11を直列又は一のpMOSトランジスタ12を備えた並列回路に接続した第1の回路ブロック1と、複数のnMOSトランジスタ21を直列又は一のnMOSトランジスタ22を備えた並列回路に接続した第2の回路ブロック2とを備え、前記第1の回路ブロック1と前記第2の回路ブロック2との接続点Sを出力端子Voutに接続するとともに、全ての前記pMOSトランジスタ11,12のゲート及び全ての前記nMOSトランジスタ21,22のゲートを共通の入力端子Vinに接続する半導体回路。

(もっと読む)

平板表示装置及びその製造方法

【課題】平板表示装置及びその製造方法を提供する。

【解決手段】基板と、TFT活性層と、キャパシタの第1下部電極及び第1下部電極上に形成されたキャパシタの第1上部電極と、第1絶縁層と、チャンネル領域に対応する領域に順次に形成されたゲート下部電極及びゲート上部電極と、キャパシタの第1上部電極に対応する領域に順次に形成されたキャパシタの第2下部電極及び上部電極と、画素下部電極及び画素下部電極を露出させるように画素下部電極エッジの上部に配された画素上部電極と、活性層のソース及びドレイン領域を露出させるコンタクトホール、及び画素上部電極エッジの一部を露出させるビアホールによって貫通される第2絶縁層と、第2絶縁層上に形成され、コンタクトホール及びビアホールを通じて、ソース、ドレイン領域及び画素上部電極と接続するソース及びドレイン電極と、を備える平板表示装置。

(もっと読む)

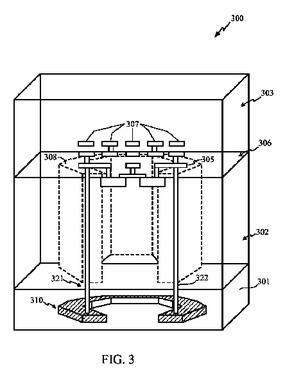

能動および受動デバイスをチップ内に配置する方法

半導体ダイ(300)は、第1および第2の面をもつ半導体基板層(302)と、半導体基板層の第2の面に隣接する金属層と、半導体基板層の第1の面上の活性層(306)内の1つまたは複数の能動デバイス(305)と、活性層と電気的に接続される金属層内の受動デバイス(310)とを含む。受動デバイスは、シリコン貫通ビア(TSV)(321、322)によって、活性層に電気的に結合することができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】低い電源電圧で駆動でき、かつ、電源電圧の変動に対して安定な基準電圧を生成するとともに、基準電圧の温度係数が製造工程におけるパラメータの変動に影響されにくい半導体装置を提供することである。

【解決手段】第1のトランジスタのコレクタ端子と第2のトランジスタのエミッタ端子とを接続して出力端子とし、第1のトランジスタのベース端子と第2のトランジスタのベース端子とを接続して第1のベース端子とし、第1のトランジスタと第2のトランジスタとは同一構造であり、第1のベース端子には、第1のトランジスタのエミッタ側pn接合がわずかに順方向バイアスされる動作領域から逆方向バイアスされる動作領域となる範囲の電圧を印加され、供給電圧には、第1及び第2のトランジスタがnpn、又はpnpかによって、正の電圧又は負の電圧を印加される半導体装置。

(もっと読む)

論理回路及び半導体装置

【課題】電気特性の制御された酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

集積回路用保護装置

【課題】 EMC耐量を高めることのできる集積回路用保護装置を実現する。

【解決手段】 アイソレーション層4により区画された第1および第2の島状領域は、それぞれプレーナ型のバイポーラトランジスタ構造である。第1の島状領域においてベース層6およびエミッタ層7により形成される第1のツェナーダイオードZD1が入出力端子SGに順方向接続されている。また、第1の島状領域を形成するコレクタ層3は電気的に浮遊な状態になっているため、コレクタ層3およびアイソレーション層4が寄生ダイオードとして動作しない。このため、装置の降伏電位を高めることができ、入出力端子SGから侵入した高周波ノイズの負電圧部分がクランプされ難くなるので、フィルタ回路を通過した高周波ノイズの直流成分にズレが発生し難い。

(もっと読む)

キャパシタレスメモリセルを論理素子と集積化するための方法および構造

基板(基材)上で論理デバイスを製造すること、論理デバイスの表面上に中間半導体基板を形成すること、およびその中間半導体基板上にキャパシタレスメモリセルを製造することを含む集積回路を製造するための方法である。論理デバイスの表面上に形成されるキャパシタレスメモリセルを備える集積回路もまた開示される。それらは、そのような集積回路を含むマルチコアマイクロプロセッサとして使用される。  (もっと読む)

(もっと読む)

ゲート・スタック、ゲート・スペーサ及びコンタクト・ビアを用いる垂直型金属−絶縁体−金属(MIM)キャパシタ

【課題】 向上した製造可能性を有する金属−絶縁体−金属キャパシタ、及びその製造方法を提供する。

【解決手段】 垂直型金属−絶縁体−金属キャパシタを含む半導体構造体、及び垂直型金属−絶縁体−金属キャパシタを含む半導体構造体の製造方法がそれぞれ、半導体基板の上に配置された分離領域の上に配置され形成されたダミー金属酸化物半導体電界効果トランジスタからの構造コンポーネントを用いる。ダミー金属酸化物電界効果トランジスタは、分離領域を含む半導体基板の上に配置された金属酸化物半導体電界効果トランジスタと同時に形成することができる。金属−絶縁体−金属キャパシタは、キャパシタ・プレートとしてゲートを用い、ゲート誘電体として均一な厚さのゲート・スペーサを用い、別のキャパシタ・プレートとしてコンタクト・ビアを用いる。容量の増大のために、均一な厚さのゲート・スペーサは、導体層を含むことができる。容量の増大のために、単一のコンタクト・ビアを用いる鏡像となる金属−絶縁体−金属キャパシタ構造体を用いることもできる。

(もっと読む)

半導体構造、半導体構造の形成方法、半導体装置の動作方法(高周波の高調波を減少するためのSOIRFスイッチ)

【課題】SOI基板における容量結合を減少した集積回路を提供する。

【解決手段】底部半導体層と同じ導電型のドーパントを含む第1のドープされた半導体領域18及び反対導電型のドーパントを含む第2のドープされた半導体領域28がSOI基板の埋め込み絶縁層20の直下に形成される。第1のドープされた半導体領域18及び第2のドープされた半導体領域28は、共にグランド電位に接続されるか、又は底部半導体層への少数キャリアの順方向バイアス注入に基づく過剰な電流を生じるには不十分は電圧、即ち、0.6V乃至0.8Vを越えない電位差を保って底部半導体層に対して順方向バイアスされる。上部半導体の半導体装置内の電気信号により誘起される電荷層内の電荷は第1及び第2のドープされた半導体領域に接続されている電気的コンタクトを介して引き出され、これにより半導体装置内の高調波信号を減少させる。

(もっと読む)

201 - 220 / 754

[ Back to top ]