Fターム[5F038EZ06]の内容

Fターム[5F038EZ06]に分類される特許

101 - 120 / 754

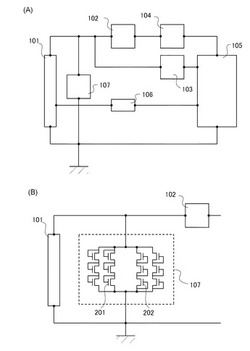

半導体装置

【課題】通信距離が極端に短い場合においても正常に動作し、且つ通信距離が長い場合においては、保護回路での消費電力を抑え、信頼性の高い半導体装置(RFID)を提供する。

【解決手段】無線によりデータの交信が可能な半導体装置(RFID)を構成する素子を保護するための保護回路107を設けることに特徴を有する。そして、整流回路102において生成された直流電源電位が所定の値(基準値)以上となるときに保護回路107が動作するようにし、生成される直流電源電位の値を小さくする。一方、整流回路102において生成された直流電源電位が所定の値(基準値)以下となるときは、保護回路107が動作しないようにし、生成された直流電源電位の値をそのまま用いる。また、保護回路107のトランジスタ201,202は、酸化物半導体層により構成されており、トランジスタ201,202のオフ電流を下げ、保護回路107での消費電力を抑える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

キャパシタ装置及びその製造方法

【課題】キャパシタ装置及びその製造方法を提供する。

【解決手段】本発明に係るキャパシタ装置10は、第1導電型を有して第1電圧が印加される第1ウェル105及び第2導電型を有して第2電圧が印加される第2ウェル110を有する基板100、及び第1または第2ウェル105,110と絶縁されるように第1または第2ウェル105,110の上部に配されたゲート電極126を含み、キャパシタ装置10のキャパシタンスは、第1ウェル105と第2ウェル110との間の第1キャパシタンス及び第1または第2ウェル105,110とゲート電極126との間の第2キャパシタンスを含む。

(もっと読む)

半導体集積回路装置

【課題】SOI基板に形成されたMOSトランジスタを含む半導体集積回路装置において、半導体集積回路装置に入力される電源電圧が高い場合であっても、SOI基板のBOX酸化膜やシリコン層を厚くすることなく、回路動作を安定させる。

【解決手段】MOSトランジスタM1〜M9は、シリコン基板、BOX酸化膜及びシリコン活性層を有するSOI基板に形成され、かつ、ソース拡散層の底部及びドレイン拡散層の底部がBOX酸化膜に到達して形成されている。エンハンスメント型PchMOSトランジスタM3,M4、M5,M7は、デプリーション型NchMOSトランジスタM10を介して、電源電圧が入力される電源端子VDDに接続されている。MOSトランジスタM10は、ソース、ゲート及びボディが結線されて定電流源として機能し、ソース電位がシリコン基板電位よりも高くなることで飽和電流が減少する電気的特性をもっている。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

半導体装置

【課題】低電位領域と高電位の配線が交差することの無い優れた耐圧性能を示す半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、ロジック回路(501)と、ロジック回路からの制御信号に従い低電位側パワー素子を駆動する低電位側駆動回路(502)と、ロジック回路からの制御信号がレベルシフト回路を介して入力され、高電位側パワー素子(506)を駆動する高電位側駆動回路(505)と、複数に重なったトレンチ分離領域により、前記高電位側パワー素子を含む高電位島を分離する多重トレンチ分離領域(508)と、を有する。

(もっと読む)

容量素子の製造方法

【課題】基板上に耐圧が異なる容量素子を共通の工程で形成する際に、基板上に残渣を残さないようにする。

【解決手段】基板10の上に半導体不純物がドープされた第1ポリシリコン層40を形成し、第1ポリシリコン層40の上にCVD法により第1酸化膜41を層状に堆積する(図2(a))。これにより、1回目の酸化で第1酸化膜41を第1ポリシリコン層40の粒界部に入り込ませないようにする。そして、第1酸化膜41を第1ボトム膜24にパターニングした後(図2(b))、第1ポリシリコン層40の上に第2酸化膜42を形成する(図2(c))。2回目の酸化は短時間で終わるので、第1ポリシリコン層40の増速酸化が進行する前に第2酸化膜42の形成が完了する。このため、第1ポリシリコン層40をエッチングする際に第2酸化膜42の一部がマスクとならないようにすることができる。

(もっと読む)

半導体装置

【課題】デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としない半導体集積回路装置を提供する。

【解決手段】P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層3とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

半導体装置

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】直列に複数個接続されたそれぞれのMISFETQN1〜QN5のソース領域とドレイン領域の間に、ソース領域の電位を基準としてドレイン領域に正電圧を印加する場合と、ソース領域の電位を基準としてドレイン領域に負電圧を印加する場合のいずれの状態においても、ソース領域の電位とドレイン電極の電位が同電位の状態よりも容量が減少する電圧依存性を持つ歪補償用容量回路CAPC2が接続されている。

(もっと読む)

半導体装置

【課題】支持基板に接地電極を備えることなく、第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供する。

【解決手段】支持基板10を、第1導電型領域10aと第2導電型領域10bとを有し、第1素子形成領域20にノイズが印加されてノイズが伝播されたときの当該ノイズの伝播経路中に、第1、第2導電型領域10a、10bで構成されるPNP接合またはNPN接合を有するものとする。このような半導体装置では、PNP接合またはNPN接合の間に構成される空乏層により、第1、第2素子形成領域20、30の間でノイズが伝播することを抑制することができる。

(もっと読む)

高周波スイッチ回路

【課題】通過損失が少なく出力特性が良いSOI基板上の高周波スイッチ回路を提供する。

【解決手段】本発明の実施形態の高周波スイッチ回路は、シリコン基板20上に形成された酸化膜21上に、第1の端子1と、入出力端子2と、第1の電極4bが前記第1の端子1に電気的に接続され、第2の電極4cが前記入出力端子2に接続されたFET4とを備える。第1の層間絶縁膜22が前記FETを周囲から離間分離し前記酸化膜21に達する溝に埋め込まれて配置され、前記酸化膜21と接続され、前記FET4を周囲から絶縁する。導電体層10が、前記溝内の前記第1の層間絶縁膜22上に形成され、接地端子GNDに接続される。第2の層間絶縁膜23が、前記導電体層10上及び前記FET4上に形成される。直流電圧を供給する配線層7が、前記溝内の第1の層間絶縁膜22上且つ前記導電体層10上に前記第2の層間絶縁膜23を介して形成されている。

(もっと読む)

内部回路と静電保護回路を具備する半導体集積回路

【課題】電源電圧の分離数や接地電圧の分離数の増大により静電保護回路の回路数もしくは静電保護素子数の増大を軽減する。

【解決手段】半導体集積回路1は、第1と第2と第3の動作電圧供給端子21、22、23と、第1と第2と第3の内部回路11、12、13と、第1と第2と第3の静電保護回路41、42、43と、接続中Cdとを具備する。第1と第2と第3の内部回路11、12、13は、第1と第2と第3の動作電圧供給端子21、22、23の第1と第2と第3の動作電圧でそれぞれ動作する。第1と第2と第3の静電保護回路41、42、43は、第1と第2と第3の動作電圧供給端子21、22、23と接続中点Cdの間にそれぞれ接続される。すなわち、第1と第2と第3の静電保護回路41、42、43は、従来のΔ(デルタ)接続ではなく、接続中点Cdに関してY(スター)接続される。

(もっと読む)

半導体集積回路装置の検査方法及び半導体集積回路装置

【課題】複数の集積回路層が厚さ方向に積層されて成る半導体集積回路装置の層間接続不良の有無を、一層積層する毎に短時間で検査することが可能な検査方法及び半導体集積回路装置を提供する。

【解決手段】互いに積層される集積回路層10及び20に、複数の検査用整流素子部15及び25をそれぞれ形成する。複数の検査用整流素子部15(25)は、複数の接続用端子14(24)のそれぞれと正電源配線13a(23a)及び接地配線13b(23b)との間に接続され、整流素子15a,15b(25a,25b)を含み電流により発光する。複数の接続用端子14及び24を互いに電気的に接続したのち、正電源配線13a(又は接地配線13b)と接地配線23b(又は正電源配線23a)との間にバイアス電圧を印加し、検査用整流素子部25の発光に基づいて、接続用端子14及び24の接続状態を検査する。

(もっと読む)

電界効果トランジスタの高電圧動作方法とそのバイアス回路

【課題】 ICないしLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該ICないしLSI中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートを分割してドレインにより近い分割ゲートへドレイン電位により近い電位でかつドレイン電位に応じて変化する電位を供給する手段をとる。

(もっと読む)

電流検出回路およびそれを有するインバータ回路が備えられる半導体装置

【課題】電流値だけでなく電流の流れる向きまで検出できる電流検出回路およびそれを有するインバータ回路が備えられる半導体装置を提供する。

【解決手段】下アーム10b、10d、10fのIGBT11b、11d、11fおよびFWD12b、12d、12fに対してセンス素子を備えると共に、各センス素子に対して電流検出抵抗18a〜18fが直列接続させる。これにより、各センス素子および電流検出抵抗18a〜18fに基づいて、具体的には第1電位および第2電位を検出することにより、各相の電流経路に流れる電流の電流値の絶対値および向きを検出することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】界面キャリア層SCLを構成する電子の移動抑制手段として、MISFETQN1とMISFETQN2の間に電極層ELを設けて電極層ELと界面キャリア層SCLとの間に容量素子Cを形成する手段をとっている。そして、この容量素子Cの上部電極となる電極層ELに正電位を印加することにより、電極層ELに相対する界面キャリア層SCLの電子を固定している。

(もっと読む)

インバータ回路

【課題】1チップ化しつつ、高温化による誤動作を抑制し、かつ、半導体パワー素子に流れる電流を低減し、チップサイズの増大を抑制することができるインバータ回路を提供する。

【解決手段】コンバータ電源回路部2の電源供給ライン8中、例えば、IPD20におけるパワーMOSFET220のハイサイド側に電流制限抵抗240を備える。この電流制限抵抗240によって電源供給ライン8に流れる電流の電流値を制限することができるため、パワーMOSFET220での発熱を抑制することが可能となる。したがって、インバータ回路1内の素子の定格温度を超えることを防止することが可能となり、誤動作が生じることを抑制できる。これにより、インバータ回路1の信頼性の向上を図ることが可能となる。また、パワーMOSFET220として必要な能力を軽減することが可能となり、大面積な素子としなくても済む。

(もっと読む)

薄膜トランジスタ回路基板の製造方法及び薄膜トランジスタ回路基板

【課題】静電気による薄膜トランジスタの閾値電圧変動や絶縁破壊短絡を抑制できる薄膜トランジスタ回路基板の製造方法及び薄膜トランジスタ回路基板を提供する。

【解決手段】薄膜トランジスタと、静電気誘導素子と、を基板上に有する薄膜トランジスタ回路基板の製造方法であって、基板に設けられた半導体層の上に、薄膜トランジスタの半導体層のパターンを形成する第1のフォトリソ工程と、静電気誘導素子の半導体層のパターンを形成する第2のフォトリソ工程と、基板に設けられた半導体層をエッチングする工程と、を実施することにより薄膜トランジスタの半導体層及び静電気誘導素子の半導体層を形成し、第1のフォトリソ工程におけるフォトレジストの硬化温度は、第2のフォトリソ工程におけるフォトレジストの硬化温度よりも高いことを特徴とする薄膜トランジスタ回路基板の製造方法。

(もっと読む)

半導体装置

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】TXシャントトランジスタSH(TX)を構成するMISFETQN1〜MISFETQN5において、GND端子に近い側に接続されたMISFETQN5から送信端子TXに近い側に接続されたMISFETQN1になるに連れて、ゲート幅Wgが大きくなるように構成されている。

(もっと読む)

半導体装置

【課題】第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供することを目的とする。

【解決手段】第1、第2素子形成領域20、30に形成された半導体素子のうち、第1素子形成領域20に形成された半導体素子を外部機器と接続し、第1素子形成領域20と第2素子形成領域30との間に、第1導電型層60と、当該第1導電型層60に挟まれる第2導電型層61とを配置し、第1、第2導電型層60、61の間に、オフ時に半導体層12の表面から埋込絶縁膜11に達し、第1、第2素子形成領域20、30との間を仕切る空乏層63、64を構成する。

(もっと読む)

101 - 120 / 754

[ Back to top ]