Fターム[5F038EZ06]の内容

Fターム[5F038EZ06]に分類される特許

61 - 80 / 754

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】基板を貫通するトレンチによって複数の部分領域に分割されてなる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法であって、部分領域の側壁に導電層を形成するメリットだけを享受して、該導電層の形成に伴う悪影響を排除することのできる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ce,Cea〜Ced,Cek,Celに分割され、前記複数の部分領域のうち、一部の部分領域Cea〜Cedの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、トレンチ31aに絶縁体31bが埋め込まれてなる領域分割基板A20とする。

(もっと読む)

ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法

【課題】ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法を提供する。

【解決手段】特に分子の特性評価に適用される本発明によると、以下を備える素子が作られる:ナノ物体(2)に接続される上部接触パッド(8)を備えた上部層(16);外部電気システム(4)に接続される下部接触パッド(12)を備えた下部層(18);前記下部層上にあり、前記下部パッドと接触する電気的貫通ビア(22)を備えた接着層(20);前記接着層と前記上部層の間にあり、前記上部パッドを前記下部パッドに接続するための導電ライン(25)及び電気的ビア(26)を備えた少なくとも2つの層(22、24)。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

半導体装置およびそれを用いた発光装置

【課題】 層間絶縁膜を挟んでゲート電極と容量電極が対向してできる容量の占有面積を小さくする。

【解決手段】 チャネル領域上の層間絶縁膜が周囲よりも膜厚が薄く、その部分で容量電極がゲート電極と対向して容量を形成している半導体装置。

(もっと読む)

半導体装置

【課題】消費電力を極力抑制することで電源の安定化を実現する半導体装置を提供する。

【解決手段】ロジック部11、メモリ部12、ロジック部とメモリ部の一方又は両方の動作頻度を検出する検出部13、検出部の検出結果に基づきロジック部及びメモリ部の一方又は両方にしきい値制御信号を供給するしきい値制御部14を有する半導体装置である。ロジック部とメモリ部の各々は複数のトランジスタを有しており、複数のトランジスタの各々は、論理信号が入力される第1のゲート電極と、しきい値制御信号が入力される第2のゲート電極と、半導体膜とを有する。

(もっと読む)

半導体装置及びその製造方法並びに抵抗器及び半導体素子

【課題】pn接合におけるリーク電流を抑制する。

【解決手段】N−型半導体層10と、シリサイド層20sがその表面に形成されたP−型半導体層20とが、絶縁体9上に形成される。半導体層10にはPMOSトランジスタを、半導体層20にはNMOSトランジスタを、それぞれ形成することができる。半導体層10,20がpn接合J50aを形成する場合、これはシリサイド層20sの端部から近く、結晶欠陥が小さい位置に存在するので、ここにおけるリーク電流は非常に小さい。半導体層10,20が形成するpn接合は、シリサイド層20sの端部から2μm以下の距離にあることが望ましい。

(もっと読む)

半導体装置

【課題】正確にメインセルに流れる電流を検出することができると共に、電流検出の直線性を向上させられ、高い電圧が用いられる場合でもその影響を受け難い半導体装置を提供する。

【解決手段】センスセルの両側にメインセルを配置し、センスセルのエミッタがメインセルのエミッタに挟まれた構造にする。これにより、センスセルのエミッタに流れる電流密度とセンスセルのエミッタに流れる電流密度とを近づけることができ、ミラー比がメインセルとセンスセルそれぞれのエミッタの長手方向における長さの比に近くなる。また、センスセルのエミッタに流れる電流密度とセンスセルのエミッタに流れる電流密度とを近づけられるため、スイッチング時や大電流が流れる時に流れる単位面積当たりの電流量がメインセル側と比較してセンスセル側において大きくなることを抑制できる。このため、電流の偏りを抑制することができ、破壊耐量を向上させることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供すること。

【解決手段】トランジスタと、容量素子と、を有し、トランジスタは、第1の酸化物半導体層と、第1の酸化物半導体層と接するソース電極およびドレイン電極と、第1の酸化物半導体層と重なるゲート電極と、第1の酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、容量素子は、ソース電極またはドレイン電極と、ソース電極またはドレイン電極と接する第2の酸化物半導体層と、第2の酸化物半導体層と接する容量素子電極と、を有する半導体装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

グラフェン素材の製造方法

【課題】所望形状のグラフェン素材を容易に作製する。

【解決手段】まず、基板本体12を用意し、その基板本体12の全面にNiの結晶層14を成膜する。続いて、リソグラフィ法により結晶層14をジグザグ状にパターニングし、触媒金属層16とする。さらに、触媒金属層16の側面にTiを形成してこれをマスク材17とする。次に、触媒金属層16に対してアセチレンとアルゴンとの混合ガスによりC原子を供給する。すると、Ni表面は(111)面に再配列されると共に、供給されたC原子は六角格子を形成してグラフェンが成長していく。グラフェンは触媒金属層16上に形成されるため、触媒金属層16と同じ形状つまりジグザグ状となる。次に、ジグザグ状のグラフェンの両末端に四角形の電極18,20を取り付ける。その後、触媒金属層16を酸性溶液で溶かし、グラフェンをグラフェン素材10として取り出す。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

半導体装置

【課題】複数のフローティング領域の間の電位差の不均一を軽減することができる半導体装置を提供する。

【解決手段】半導体装置は、領域3(k)と領域3(k+1)間に、外部容量6(k)を備えている。複数の外部容量6(k)は、その容量がkの増加とともに(即ち、図1の紙面右側から紙面左側に向かうほど)大きくなるように選定されている。この構造により、領域3(k)と領域3(k+1)間の電位差の不均一を軽減することができる。

(もっと読む)

DC−DCコンバータ及びその作製方法

【課題】単一な高電圧の入力電圧で駆動し、電圧変換回路及び制御回路を有するDC−DCコンバータを得ること、及び、DC−DCコンバータの占有面積の増大を抑制する。

【解決手段】入力電圧が印加される入力端子と、入力端子と接続され第1のトランジスタを有する電圧変換回路と、電圧変換回路を制御し珪素材料をチャネル形成領域に有する第2のトランジスタを有する制御回路と、入力端子と制御回路との間に設けられ入力電圧を入力電圧より低い電圧である電源電圧に変換する第3のトランジスタとを有し、第1のトランジスタ及び第3のトランジスタは酸化物半導体材料をチャネル形成領域に有するトランジスタであり、第2のトランジスタ、並びに、第1のトランジスタ及び第3のトランジスタは、絶縁膜を介して積層されているDC−DCコンバータ及びその作製に関する。

(もっと読む)

半導体装置

【課題】本発明の実施形態は、高パワーの高周波信号に対する耐圧を維持しながら小型化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、絶縁膜の上の半導体層に設けられたFETを含むスイッチ回路を有する半導体装置であって、前記FETのソース領域とドレイン領域との間に、前記ソース領域から前記ドレイン領域に向かう方向に並んで設けられた第1のゲート電極および第2のゲート電極と、前記第1のゲート電極と前記第2のゲート電極との間の中間領域に電気的に接続された制御端子と、を備える。前記FETは、前記第1のゲート電極および前記第2のゲート電極に供給されるゲート電圧によりON/OFF制御され、前記FETがON状態にある時、前記制御端子をアース電位とし、前記FETがOFF状態にある時、前記制御端子を正電位または負電位とする。

(もっと読む)

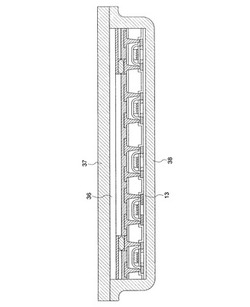

高周波半導体スイッチ

【課題】ゲート配線に良好な電圧分布を形成し、挿入損失特性およびハーモニック特性を向上した高周波半導体スイッチを提供する。

【解決手段】無線通信を切り替えるための高周波半導体スイッチに含まれる電界効果型トランジスタ50であって、基板に形成されたソース領域100と電気的に接続され、一の方向に延びるソース配線60と、基板に形成されたドレイン領域110と電気的に接続され、ソース配線と略平行に延びるドレイン配線70と、ソース配線60およびドレイン配線70の間において、ソース配線60およびドレイン配線70と略平行に延びる平行部分122を有するゲート120と、ゲート120に電圧を印加するためゲート配線80と、ゲート120およびゲート配線80を電気的に接続するゲートビア82と、を有し、平行部分122は、2つの端部126を有し、ゲートビア82から2つの端部126にそれぞれ電圧の印加の経路が形成される電界効果型トランジスタ。

(もっと読む)

61 - 80 / 754

[ Back to top ]