DC−DCコンバータ及びその作製方法

【課題】単一な高電圧の入力電圧で駆動し、電圧変換回路及び制御回路を有するDC−DCコンバータを得ること、及び、DC−DCコンバータの占有面積の増大を抑制する。

【解決手段】入力電圧が印加される入力端子と、入力端子と接続され第1のトランジスタを有する電圧変換回路と、電圧変換回路を制御し珪素材料をチャネル形成領域に有する第2のトランジスタを有する制御回路と、入力端子と制御回路との間に設けられ入力電圧を入力電圧より低い電圧である電源電圧に変換する第3のトランジスタとを有し、第1のトランジスタ及び第3のトランジスタは酸化物半導体材料をチャネル形成領域に有するトランジスタであり、第2のトランジスタ、並びに、第1のトランジスタ及び第3のトランジスタは、絶縁膜を介して積層されているDC−DCコンバータ及びその作製に関する。

【解決手段】入力電圧が印加される入力端子と、入力端子と接続され第1のトランジスタを有する電圧変換回路と、電圧変換回路を制御し珪素材料をチャネル形成領域に有する第2のトランジスタを有する制御回路と、入力端子と制御回路との間に設けられ入力電圧を入力電圧より低い電圧である電源電圧に変換する第3のトランジスタとを有し、第1のトランジスタ及び第3のトランジスタは酸化物半導体材料をチャネル形成領域に有するトランジスタであり、第2のトランジスタ、並びに、第1のトランジスタ及び第3のトランジスタは、絶縁膜を介して積層されているDC−DCコンバータ及びその作製に関する。

【発明の詳細な説明】

【技術分野】

【0001】

開示される発明の一態様は、DC−DCコンバータ及びその作製方法に関する。

【背景技術】

【0002】

近年、直流電源を必要とする機器の多様化により、入力電圧とは異なる直流電圧で駆動する回路を駆動するためにDC−DCコンバータが多用されている(特許文献1、特許文献2、及び特許文献3参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−148129号公報

【特許文献2】特開2003−235251号公報

【特許文献3】特開2009−254110号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

DC−DCコンバータには、電圧変換回路と当該電圧変換回路を制御する制御回路が含まれる。電圧変換回路の素子には、高い電圧が印加されるため高耐圧なパワーデバイスを用いる。このようなパワーデバイスを用いた電圧変換回路は、高い入力電圧のみで駆動させることが可能である。このようなパワーデバイスとして、例えば酸化物半導体材料を用いた素子(さらに例えば、酸化物半導体膜をチャネル形成領域に用いたトランジスタ)が挙げられる。

【0005】

一方、電圧変換回路を制御する制御回路の素子では、高い駆動速度が求められる。このような高い駆動速度を得ることができる素子としては、例えば珪素材料を用いた素子(例えば珪素膜をチャネル形成領域に用いるトランジスタや、単結晶シリコン基板を用いて形成されたトランジスタ)が挙げられる。しかしながら珪素材料を用いた素子は、高耐圧ではないので高電圧を印加できない。

【0006】

珪素はバンドギャップが狭いため、高電圧を印加すると、電子が雪崩的に発生するアバランシェ降伏が起こる恐れがある。アバランシェ降伏が起こると、その素子は破壊されてしまう。一方、酸化物半導体は、バンドギャップが広いため、アバランシェ降伏が生じにくく、素子が破壊される恐れが小さい。

【0007】

ここで、単一の高い入力電圧のみで、電圧変換回路及び制御回路を有するDC−DCコンバータを動作させる場合を考える。入力電圧が単一であることは、DC−DCコンバータの占有面積を縮小する上で好ましい。しかしながら、当該高い入力電圧は、電圧変換回路は駆動できるものの、制御回路の電圧として高すぎるため制御回路を破壊する恐れがある。よって、当該単一の高い入力電圧のみで電圧変換回路及び制御回路を有するDC−DCコンバータを動作させることは難しい。

【0008】

そのため、高い入力電圧が印加される入力端子と制御回路との間に当該高い入力電圧の電圧を降下させる素子を設ける。降下させた電圧を制御回路に供給すれば、制御回路を破壊する恐れがなくなる。

【0009】

このような高い入力電圧の電圧を降下させる素子として、上述のパワーデバイスを用いればよい。しかし制御回路と当該高い入力電圧の電圧値を降下させるパワーデバイスを設けるということは、DC−DCコンバータの占有面積を増大させる恐れがある。

【0010】

以上を鑑みて、開示される発明の一態様では、単一な高電圧の入力電圧で駆動し、電圧変換回路及び制御回路を有するDC−DCコンバータを得ることを課題の一とする。

【0011】

また開示される発明の一態様では、DC−DCコンバータの占有面積の増大を抑制することを課題の一とする。

【0012】

また開示される発明の一態様では、電圧変換回路のパワーデバイスと入力電圧の電圧を降下させるパワーデバイスを同工程で作製することによって、作製工程及び作製コストを低減させることを課題の一とする。

【課題を解決するための手段】

【0013】

当該単一の高い入力電圧の電圧値を降下させるパワーデバイス及び電圧変換回路のパワーデバイスとして、高耐圧の半導体素子である酸化物半導体材料を用いた素子を用い、また制御回路の素子として低耐圧の半導体素子、例えば珪素材料を用いた素子、を用いる。また当該パワーデバイス及び制御回路の素子を重畳させる。

【0014】

制御回路の素子として低耐圧の半導体素子、例えば珪素材料を用いた素子を用いても、当該パワーデバイスが高電圧の入力電圧の電圧値を降下させるので、制御回路が破壊される恐れはない。

【0015】

当該パワーデバイス及び制御回路の素子を重畳させるため、DC−DCコンバータの占有面積の増大を抑制することが可能である。

【0016】

また開示される発明の一態様では、電圧変換回路のパワーデバイスである酸化物半導体材料を用いた素子と入力電圧の電圧を降下させるパワーデバイスである酸化物半導体材料を用いた素子を、同じ工程で作製する。これにより、作製工程及び作製コストを低減させることができる。

【0017】

開示される発明の一態様は、入力電圧が印加される入力端子と、当該入力端子と接続され、第1のトランジスタを有する電圧変換回路と、当該電圧変換回路を制御し、珪素材料をチャネル形成領域に有する第2のトランジスタを有する制御回路と、当該入力端子と当該制御回路との間に設けられ、当該入力電圧を当該入力電圧より低い電圧である電源電圧に変換する第3のトランジスタとを有し、当該第1のトランジスタ及び当該第3のトランジスタは、酸化物半導体材料をチャネル形成領域に有するトランジスタであり、当該第2のトランジスタ、並びに、当該第1のトランジスタ及び当該第3のトランジスタは、絶縁膜を介して積層されていることを特徴とするDC−DCコンバータに関する。

【0018】

開示される発明の一態様は、絶縁表面上に、珪素材料を第1のチャネル形成領域に用いた第1のトランジスタを形成し、当該第1のトランジスタを覆って、絶縁膜を形成し、当該絶縁膜上に、酸化物半導体材料を第2のチャネル形成領域として用いた第2のトランジスタ、及び当該酸化物半導体材料を第3のチャネル形成領域として用いた第3のトランジスタを形成し、当該第2のトランジスタは電圧変換回路を構成し、当該第1のトランジスタは、当該電圧変換回路を制御する制御回路を構成し、当該第3のトランジスタは、入力端子と当該制御回路との間に設けられ、当該入力端子に印加される入力電圧を当該入力電圧より低い電圧である電源電圧に変換することを特徴とするDC−DCコンバータの作製方法に関する。

【0019】

開示される発明の一態様において、当該酸化物半導体材料は、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系酸化物半導体、二元系金属の酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体、一元系金属の酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体のいずれかであることを特徴とする。

【0020】

開示される発明の一態様において、当該電圧変換回路は、降圧型の電圧変換回路であることを特徴とする。

【0021】

開示される発明の一態様において、当該電圧変換回路は、フライバック型の電圧変換回路であることを特徴とする。

【0022】

開示される発明の一態様において、当該電圧変換回路は、フォワード型の電圧変換回路であることを特徴とする。

【0023】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【発明の効果】

【0024】

開示される発明により、単一な高電圧の入力電圧で駆動し、電圧変換回路及び制御回路を有するDC−DCコンバータを得ることができる。

【0025】

開示される発明の一態様により、DC−DCコンバータの占有面積の増大を抑制することができる。

【0026】

開示される発明の一態様では、電圧変換回路のパワーデバイスと入力電圧の電圧を降下させるパワーデバイスを同工程で作製するので、作製工程及び作製コストを低減させることができる。

【図面の簡単な説明】

【0027】

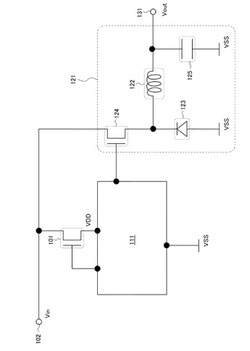

【図1】DC−DCコンバータの回路図。

【図2】DC−DCコンバータの回路図。

【図3】DC−DCコンバータの回路図。

【図4】DC−DCコンバータの回路図。

【図5】トランジスタの積層構造を示す断面図。

【図6】トランジスタの積層構造を示す断面図。

【発明を実施するための形態】

【0028】

以下、本明細書に開示された発明の実施の態様について、図面を参照して説明する。但し、本明細書に開示された発明は多くの異なる態様で実施することが可能であり、本明細書に開示された発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0029】

なお本明細書に開示された発明において、半導体装置とは、半導体を利用することで機能する素子及び装置全般を指し、電子回路、表示装置、発光装置等を含む電気装置およびその電気装置を搭載した電子機器をその範疇とする。

【0030】

<回路構成>

図1に示すDC−DCコンバータは、制御回路111、電圧変換回路121、入力電圧Vinが印加される入力端子102、酸化物半導体材料をチャネル形成領域に用いたトランジスタ、例えば、酸化物半導体膜をチャネル形成領域に有するトランジスタ(以下、酸化物半導体トランジスタと呼ぶ)であるトランジスタ101、電圧変換回路121から出力される出力電圧Voutを出力する出力端子131を有する。

【0031】

トランジスタ101のソース又はドレインの一方は、入力電圧Vinが印加される入力端子102、及び、電圧変換回路121のトランジスタ124のソース又はドレインの一方に接続されている。トランジスタ101のソース又はドレインの他方、及びゲートは、制御回路111に接続されている。

【0032】

酸化物半導体トランジスタであるトランジスタ101は、高電圧を扱うことのできるパワーデバイスである。トランジスタ101のソース又はドレインの一方に印加された入力電圧Vinは、ゲートに印加されたゲート電圧に基づいて、入力電圧Vinよりも小さい値を有する電源電圧VDDに変換される。

【0033】

入力電圧Vinとして、例えば家庭用電源からの電圧を交流−直流変換(AC−DC変換)した電圧を用いる。入力電圧Vinとして、家庭用電源からの電圧を交流−直流変換した電圧を用いるとすると、入力電圧Vinの実効値は141Vである。そのため、このような高電圧である入力電圧Vinは、制御回路111を破壊する恐れがある。よって入力電圧Vinが印加される入力端子102と制御回路111との間に、高耐圧のパワーデバイスである酸化物半導体トランジスタを配置することは、制御回路111が破壊されることを抑制できる。

【0034】

トランジスタ101は、上述のように酸化物半導体膜をチャネル形成領域に有するトランジスタである。

【0035】

このような酸化物半導体膜の材料として、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体や、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系酸化物半導体や、二元系金属の酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体や、一元系金属の酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体などを用いることができる。なお、酸化物半導体膜をチャネル形成領域に有するトランジスタ(酸化物半導体トランジスタ)の構造及び作製工程については後述する。

【0036】

制御回路111は、トランジスタ101のソース又はドレインの他方、トランジスタ101のゲート、及び、電圧変換回路121に電気的に接続されている。さらに制御回路111は、電源電圧VDDよりも小さい値を有する電源電圧VSSが印加される。電源電圧VSSとして、例えば接地電圧GNDを用いればよい。

【0037】

図2に、図1に示す制御回路111の詳細な回路構成の例を示す。

【0038】

図2の制御回路111は、内部電圧生成回路(「レギュレータ」ともいう)110及び内部制御回路130を有している。内部電圧生成回路110は、電源電圧VDDを生成する回路であり、オペアンプ112、抵抗113、及び抵抗114を有している。

【0039】

オペアンプ112の反転入力端子は、抵抗113の一方の端子、及び、抵抗114の一方の端子に電気的に接続されている。オペアンプ112の非反転入力端子は、参照電圧Vrefが印加される端子115に電気的に接続されている。オペアンプ112の出力端子は、トランジスタ101のゲートに接続されている。

【0040】

オペアンプ112を構成するトランジスタは、高速駆動可能なトランジスタ、例えば珪素材料をチャネル形成領域に用いたトランジスタを用いればよい。なお珪素材料をチャネル形成領域に用いたトランジスタの構造及び作製工程については後述する。

【0041】

珪素材料をチャネル形成領域に用いた場合、nチャネル型トランジスタ及びpチャネル型トランジスタを得ることができる。オペアンプ112を構成するトランジスタとして、珪素をチャネル形成領域に有するトランジスタを用いると、高速駆動可能なだけでなく、nチャネル型トランジスタ及びpチャネル型トランジスタの両方を得ることができる。

【0042】

抵抗113の一方の端子は、オペアンプ112の反転入力端子、及び、抵抗114の一方の端子に電気的に接続されている。抵抗113の他方の端子は、トランジスタ101のソース又はドレインの他方、及び、内部制御回路130の第1の端子に電気的に接続されている。

【0043】

抵抗114の一方の端子は、抵抗113の一方の端子、及び、オペアンプ112の反転入力端子に電気的に接続されている。抵抗114の他方の端子は、電源電圧VSSが印加されている。

【0044】

内部制御回路130は、電圧制御或いは電流制御を行う回路である。電圧制御或いは電流制御の例としては、例えば、パルス幅変調(Pulse Width Modulation(PWM))制御やヒステリシス制御が挙げられる。本実施の形態では、内部制御回路130によって、電源電圧VDDが、トランジスタ124のゲートに印加されるゲート電圧に変換される。当該ゲート電圧に応じ、入力電圧Vinが出力電圧Voutに変換される。

【0045】

内部制御回路130の第1の端子は、トランジスタ101のソース又はドレインの他方、及び抵抗113の他方の端子に電気的に接続されている。内部制御回路130の第2の端子には、電源電圧VSSが印加される。また内部制御回路130の第3の端子は、トランジスタ124のゲートに電気的に接続されている。また図示しないが、内部制御回路130には出力電圧Voutの一部が帰還する。このような出力電圧Voutの一部は、出力電圧Voutを出力する出力端子131に電気的に接続して分圧回路を設け、当該分圧回路によって出力電圧Voutを分圧して生成すればよい。

【0046】

図2の電圧変換回路121は、降圧型の電圧変換回路である。図2の電圧変換回路121は、トランジスタ124、ダイオード123、コイル122、コンデンサ125を有している。

【0047】

トランジスタ124のソース又はドレインの一方は、トランジスタ101のソース又はドレインの一方、及び、入力電圧Vinが印加される入力端子102に接続されている。トランジスタ124のソース又はドレインの他方は、ダイオード123の出力端子、及び、コイル122の一方の端子に電気的に接続されている。トランジスタ124のゲートは、内部制御回路130の第3の端子に電気的に接続されている。

【0048】

トランジスタ124として、トランジスタ101と同様に、パワーデバイスである酸化物半導体トランジスタを用いる。トランジスタ124として酸化物半導体トランジスタを用いることで、高電圧である入力電圧Vinの印加によるトランジスタ124の破壊を抑制することができる。

【0049】

ダイオード123の出力端子は、トランジスタ124のソース又はドレインの他方、及び、コイル122の一方の端子に電気的に接続されている。ダイオード123の入力端子には、電源電圧VSSが印加される。

【0050】

コイル122の一方の端子は、ダイオード123の出力端子、及び、トランジスタ124のソース又はドレインの他方に電気的に接続されている。コイル122の他方の端子は、コンデンサ125の一方の端子、及び、出力電圧Voutを出力する出力端子131に電気的に接続されている。

【0051】

コンデンサ125の一方の端子は、コイル122の他方の端子、及び、出力電圧Voutを出力する出力端子131に電気的に接続されている。コンデンサ125の他方の端子には、電源電圧VSSが印加される。

【0052】

図2では降圧型の電圧変換回路121について説明したが、電圧変換回路121は降圧型に限定されず、必要であれば、降圧型の電圧変換回路に代えて昇圧型の電圧変換回路、又は昇降圧型の電圧変換回路を形成してもよい。

【0053】

図3では、フライバック型の電圧変換回路を用いたDC−DCコンバータについて説明する。

【0054】

図3のDC−DCコンバータは、制御回路111、電圧変換回路141、入力電圧Vinが印加される入力端子102、トランジスタ101、電圧変換回路141から出力される出力電圧Voutを出力する出力端子131を有する。

【0055】

図3の電圧変換回路141は、コイル142及びコイル146を有するトランス149、トランジスタ144、ダイオード143、コンデンサ145を有している。

【0056】

コイル142の一方の端子は、トランジスタ101のソース又はドレインの一方、及び、入力電圧Vinが印加される入力端子102に電気的に接続されている。コイル142の他方の端子は、トランジスタ144のソース又はドレインの一方に電気的に接続されている。

【0057】

トランジスタ144のソース又はドレインの一方は、コイル142の他方の端子に電気的に接続されている。トランジスタ144のソース又はドレインの他方は、電源電圧VSSが印加される。トランジスタ144のゲートは、内部制御回路130の第3の端子に電気的に接続されている。

【0058】

コイル146の一方の端子は、ダイオード143の入力端子に電気的に接続されている。コイル146の他方の端子には、電源電圧VSSが印加される。

【0059】

ダイオード143の入力端子は、コイル146の一方の端子に電気的に接続されている。ダイオード143の出力端子は、コンデンサ145の一方の端子、及び、出力端子131と電気的に接続されている。

【0060】

コンデンサ145の一方の端子は、ダイオード143の出力端子、及び、出力端子131と電気的に接続されている。コンデンサ145の他方の端子には、電源電圧VSSが印加される。

【0061】

以上により、単一な高電圧の入力電圧Vinで駆動し、電圧変換回路141及び制御回路111を有するDC−DCコンバータを得ることができる。

【0062】

図4では、フォワード型の電圧変換回路を用いたDC−DCコンバータについて説明する。

【0063】

図4のDC−DCコンバータは、制御回路111、電圧変換回路151、入力電圧Vinが印加される入力端子102、トランジスタ101、電圧変換回路151から出力される出力電圧Voutを出力する出力端子131を有する。

【0064】

図4の電圧変換回路151は、コイル152及びコイル156を有するトランス159、トランジスタ154、ダイオード153、ダイオード157、コイル158、コンデンサ155を有している。

【0065】

コイル152の一方の端子は、トランジスタ101のソース又はドレインの一方、及び、入力電圧Vinが印加される入力端子102に電気的に接続されている。コイル152の他方の端子は、トランジスタ154のソース又はドレインの一方に電気的に接続されている。

【0066】

トランジスタ154のソース又はドレインの一方は、コイル152の他方の端子に電気的に接続されている。トランジスタ154のソース又はドレインの他方は、電源電圧VSSが印加される。トランジスタ154のゲートは、内部制御回路130の第3の端子に電気的に接続されている。

【0067】

コイル156の一方の端子は、ダイオード153の入力端子に電気的に接続されている。コイル156の他方の端子には、電源電圧VSSが印加される。

【0068】

ダイオード153の入力端子は、コイル156の一方の端子に電気的に接続されている。ダイオード153の出力端子は、ダイオード157の出力端子、及び、コイル158の一方の端子と電気的に接続されている。

【0069】

ダイオード157の出力端子は、ダイオード153の出力端子、及び、コイル158の一方の端子と電気的に接続されている。ダイオード157の入力端子には、電源電圧VSSが印加される。

【0070】

コイル158の一方の端子は、ダイオード153の出力端子、及び、ダイオード157の出力端子と電気的に接続されている。コイル158の他方の端子は、コンデンサ155の一方の端子、及び、出力端子131と電気的に接続されている。

【0071】

コンデンサ155の一方の端子は、コイル158の他方の端子、及び、出力端子131と電気的に接続されている。コンデンサ155の他方の端子には、電源電圧VSSが印加される。

【0072】

以上により、単一な高電圧の入力電圧Vinで駆動し、電圧変換回路151及び制御回路111を有するDC−DCコンバータを得ることができる。

【0073】

<積層構造及びその作製工程>

ここで、オペアンプ112を構成するトランジスタ、及び、酸化物半導体トランジスタであるトランジスタ101を積層した積層構造、並びに、当該積層構造の作製工程を、以下に説明する。なお本実施の形態では、オペアンプ112を構成するトランジスタとして、珪素材料をチャネル形成領域に用いたトランジスタを用いる。

【0074】

まず、図5(A)に示すように、基板700の絶縁表面上に、公知のCMOSの作製方法を用いて、nチャネル型トランジスタ704、pチャネル型トランジスタ705を形成する。本実施の形態では、単結晶の半導体基板から分離された単結晶半導体膜を用いて、nチャネル型トランジスタ704、pチャネル型トランジスタ705を形成する場合を例に挙げている。

【0075】

具体的な単結晶半導体膜の作製方法の一例について、簡単に説明する。まず、単結晶の半導体基板に、加速されたイオンでなるイオンビームを注入する。イオンビームを注入することで、半導体基板の表面から一定の深さの領域の結晶構造が乱される。結晶構造が乱されることにより、局所的に脆弱化された脆化層が形成される。脆化層が形成される領域の深さは、イオンビームの加速エネルギーとイオンビームの入射角によって調節することができる。そして、半導体基板と、絶縁膜701が形成された基板700とを、間に当該絶縁膜701が挟まるように貼り合わせる。貼り合わせは、半導体基板と基板700とを重ね合わせた後、半導体基板と基板700の一部に、1N/cm2以上500N/cm2以下、好ましくは11N/cm2以上20N/cm2以下程度の圧力を加える。圧力を加えると、その部分から半導体基板と絶縁膜701とが接合を開始し、最終的には密着した面全体に接合がおよぶ。次いで、加熱処理を行うことで、脆化層に存在する微小ボイドどうしが結合して、微小ボイドの体積が増大する。その結果、脆化層において半導体基板の一部である単結晶半導体膜が、半導体基板から分離する。上記加熱処理の温度は、基板700の歪み点を越えない温度とする。そして、上記単結晶半導体膜をエッチング等により所望の形状に加工することで、島状の半導体膜702、島状の半導体膜703を形成することができる。

【0076】

nチャネル型トランジスタ704は、絶縁膜701上の島状の半導体膜702を用いて形成されており、pチャネル型トランジスタ705は、絶縁膜701上の島状の半導体膜703を用いて形成されている。また、nチャネル型トランジスタ704はゲート電極706を有しており、pチャネル型トランジスタ705はゲート電極707を有している。そして、nチャネル型トランジスタ704は、島状の半導体膜702とゲート電極706の間に、絶縁膜708を有する。pチャネル型トランジスタ705は、島状の半導体膜703とゲート電極707の間に、絶縁膜708を有する。

【0077】

基板700として使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、基板700には、フュージョン法やフロート法で作製されるガラス基板、石英基板、セラミック基板等を用いることができる。ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いると良い。また、ステンレス基板を含む金属基板またはシリコン基板の表面に絶縁膜を形成したものを用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板は、一般的に上記基板と比較して耐熱温度が低い傾向にあるが、作製工程における処理温度に耐え得るのであれば用いることが可能である。

【0078】

なお、本実施の形態では、単結晶の半導体膜を用いてnチャネル型トランジスタ704とpチャネル型トランジスタ705を形成する例について説明しているが、本発明はこの構成に限定されない。例えば、絶縁膜701上に気相成長法を用いて形成された多結晶の半導体膜を用いても良いし、上記半導体膜を公知の技術により結晶化しても良い。公知の結晶化方法としては、レーザ光を用いたレーザ結晶化法、触媒元素を用いる結晶化法がある。或いは、触媒元素を用いる結晶化法とレーザ結晶化法とを組み合わせて用いることもできる。また、石英のような耐熱性に優れている基板を用いる場合、電熱炉を使用した熱結晶化方法、赤外光を用いたランプアニール結晶化法、触媒元素を用いる結晶化法、950℃程度の高温アニール法を組み合わせた結晶化法を用いても良い。またnチャネル型トランジスタ704とpチャネル型トランジスタ705として、単結晶シリコン基板に、チャネル形成領域、ソース領域、及びドレイン領域を形成したトランジスタを用いても良い。

【0079】

また、図5(A)では、絶縁膜708上に導電膜を形成した後、上記導電膜をエッチング等により所望の形状に加工することで、ゲート電極706及びゲート電極707と共に、配線711を形成する。

【0080】

次いで、図5(A)に示すように、nチャネル型トランジスタ704、pチャネル型トランジスタ705、配線711を覆うように、絶縁膜712を形成する。なお、本実施の形態では、単層の絶縁膜712を用いる場合を例示しているが、上記絶縁膜712は単層である必要はなく、2層以上の絶縁膜を積層させて絶縁膜712として用いても良い。

【0081】

絶縁膜712は、後の作製工程における加熱処理の温度に耐えうる材料を用いる。具体的に、絶縁膜712として、酸化珪素、窒化珪素、窒化酸化珪素、酸化窒化珪素、窒化アルミニウム、酸化アルミニウムなどを用いるのが望ましい。

【0082】

絶縁膜712は、その表面をCMP法などにより平坦化させても良い。

【0083】

次いで、図5(A)に示すように、絶縁膜712上に、酸化物半導体トランジスタ724のゲート電極713、並びに酸化物半導体トランジスタ781のゲート電極773を形成する。酸化物半導体トランジスタ724は、図1乃至図4のトランジスタ101に相当する。酸化物半導体トランジスタ781は、図1及び図2のトランジスタ124、図3のトランジスタ144、図4のトランジスタ154に相当する。

【0084】

ゲート電極713及びゲート電極773それぞれの材料として、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム等の金属材料、これら金属材料を主成分とする合金材料を用いた導電膜、或いはこれら金属の窒化物を、単層で又は積層で用いることができる。なお、後の工程において行われる加熱処理の温度に耐えうるのであれば、上記金属材料としてアルミニウム、銅を用いることもできる。アルミニウムまたは銅は、耐熱性や腐食性の問題を回避するために、高融点金属材料と組み合わせて用いると良い。高融点金属材料としては、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム等を用いることができる。

【0085】

例えば、二層の積層構造を有するゲート電極713及びゲート電極773として、アルミニウム膜上にモリブデン膜が積層された二層の積層構造、銅膜上にモリブデン膜を積層した二層構造、銅膜上に窒化チタン膜若しくは窒化タンタル膜を積層した二層構造、または、窒化チタン膜とモリブデン膜とを積層した二層構造とすることが好ましい。3層の積層構造を有するゲート電極713及びゲート電極773としては、アルミニウム膜、アルミニウムとシリコンの合金膜、アルミニウムとチタンの合金膜またはアルミニウムとネオジムの合金膜を中間層とし、タングステン膜、窒化タングステン膜、窒化チタン膜またはチタン膜を上下層として積層した構造とすることが好ましい。

【0086】

また、ゲート電極713及びゲート電極773としてそれぞれ、酸化インジウム、酸化インジウム酸化スズ、酸化インジウム酸化亜鉛、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、または酸化亜鉛ガリウム等の透光性を有する酸化物導電膜を用いることもできる。

【0087】

ゲート電極713及びゲート電極773それぞれの膜厚は、10nm〜400nm、好ましくは100nm〜200nmとする。本実施の形態では、タングステンターゲットを用いたスパッタ法により150nmのゲート電極用の導電膜を形成した後、該導電膜をエッチングにより所望の形状に加工(パターニング)することで、ゲート電極713及びゲート電極773を形成する。なお、形成されたゲート電極の端部がテーパー形状であると、上に積層するゲート絶縁膜の被覆性が向上するため好ましい。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0088】

次いで、図5(B)に示すように、ゲート電極713及びゲート電極773上に、ゲート絶縁膜714を形成する。ゲート絶縁膜714は、プラズマCVD法又はスパッタリング法等を用いて、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜、酸化ハフニウム膜または酸化タンタル膜を単層で又は積層させて形成することができる。ゲート絶縁膜714は、水分や、水素、酸素などの不純物を極力含まないことが望ましい。スパッタリング法により酸化珪素膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。

【0089】

不純物を除去することによりi型化された酸化物半導体(高純度化された酸化物半導体)は界面準位、界面電荷に対して極めて敏感であるため、高純度化された酸化物半導体とゲート絶縁膜714との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁膜は、高品質化が要求される。

【0090】

例えば、μ波(周波数2.45GHz)を用いた高密度プラズマCVDは、緻密で絶縁耐圧の高い高品質な絶縁膜を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁膜とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

【0091】

もちろん、ゲート絶縁膜714として良質な絶縁膜を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によって膜質や、酸化物半導体との界面特性が改善される絶縁膜であっても良い。いずれにしても、ゲート絶縁膜としての膜質が良好であることは勿論のこと、ゲート絶縁膜と酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

【0092】

バリア性の高い材料を用いた絶縁膜と、窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜とを積層させた構造を有するゲート絶縁膜714を形成しても良い。この場合、酸化珪素膜、酸化窒化珪素膜などの絶縁膜は、バリア性の高い絶縁膜と酸化物半導体膜の間に形成する。バリア性の高い絶縁膜として、例えば窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などが挙げられる。バリア性の高い絶縁膜を用いることで、水分または水素などの雰囲気中の不純物、或いは基板内に含まれるアルカリ金属、重金属などの不純物が、酸化物半導体膜内、ゲート絶縁膜714内、或いは、酸化物半導体膜と他の絶縁膜の界面とその近傍に入り込むのを防ぐことができる。また、酸化物半導体膜に接するように窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を形成することで、バリア性の高い絶縁膜が直接酸化物半導体膜に接するのを防ぐことができる。

【0093】

例えば、第1のゲート絶縁膜としてスパッタリング法により膜厚50nm以上200nm以下の窒化珪素膜(SiNy(y>0))を形成し、第1のゲート絶縁膜上に第2のゲート絶縁膜として膜厚5nm以上300nm以下の酸化珪素膜(SiOx(x>0))を積層して、膜厚100nmのゲート絶縁膜714としても良い。ゲート絶縁膜714の膜厚は、トランジスタに要求される特性によって適宜設定すればよく350nm乃至400nm程度でもよい。

【0094】

本実施の形態では、スパッタ法で形成された膜厚50nmの窒化珪素膜上に、スパッタ法で形成された膜厚100nmの酸化珪素膜を積層させた構造を有する、ゲート絶縁膜714を形成する。

【0095】

なお、ゲート絶縁膜714は後に形成される酸化物半導体膜と接する。酸化物半導体膜は、水素が含有されると特性に悪影響を及ぼすので、ゲート絶縁膜714は水素、水酸基および水分が含まれないことが望ましい。ゲート絶縁膜714に水素、水酸基及び水分がなるべく含まれないようにするためには、成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極713及びゲート電極773が形成された基板700を予備加熱し、基板700に吸着した水分または水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100℃以上400℃以下、好ましくは150℃以上300℃以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。

【0096】

次いで、ゲート絶縁膜714上に、膜厚2nm以上200nm以下、好ましくは膜厚3nm以上50nm以下、さらに好ましくは膜厚3nm以上20nm以下の酸化物半導体膜を形成する。当該酸化物半導体膜から、酸化物半導体トランジスタ724及び酸化物半導体トランジスタ781それぞれのチャネル形成領域が形成される。酸化物半導体膜は、酸化物半導体をターゲットとして用い、スパッタ法により成膜する。また、酸化物半導体膜は、希ガス(例えばアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(例えばアルゴン)及び酸素混合雰囲気下においてスパッタ法により形成することができる。

【0097】

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁膜714の表面に付着している塵埃を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、四フッ化炭素などを加えた雰囲気で行ってもよい。

【0098】

酸化物半導体膜の材料には、上述したように、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体や、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系酸化物半導体や、二元系金属の酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体や、一元系金属の酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体などを用いることができる。

【0099】

本実施の形態では、In(インジウム)、Ga(ガリウム)、及びZn(亜鉛)を含むターゲットを用いたスパッタ法により得られる膜厚30nmのIn−Ga−Zn−O系酸化物半導体の薄膜を、酸化物半導体膜として用いる。上記ターゲットとして、例えば、In2O3:Ga2O3:ZnO=1:1:0.5(mol数比)、In2O3:Ga2O3:ZnO=1:1:1(mol数比)、またはIn2O3:Ga2O3:ZnO=1:1:2(mol数比)であるターゲットを用いることができる。また、In、Ga、及びZnを含むターゲットの充填率は90%以上100%以下、好ましくは95%以上100%未満である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

【0100】

また、ターゲットの純度を、99.99%以上とすることで、酸化物半導体膜に混入するアルカリ金属、水素原子、水素分子、水、水酸基、または水素化物等を低減することができる。また、当該ターゲットを用いることで、酸化物半導体膜において、リチウム、ナトリウム、カリウム等のアルカリ金属の濃度を低減することができる。

【0101】

本実施の形態では、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板700上に酸化物半導体膜を成膜する。成膜時に、基板温度を100℃以上600℃以下、好ましくは200℃以上400℃以下としても良い。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて成膜室を排気すると、例えば、水素原子、水(H2O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

【0102】

また、スパッタリング装置の処理室のリークレートを1×10−10Pa・m3/秒以下とすることで、スパッタリング法による成膜途中における酸化物半導体膜への、アルカリ金属、水素化物等の不純物の混入を低減することができる。また、排気系として吸着型の真空ポンプを用いることで、排気系からアルカリ金属、水素原子、水素分子、水、水酸基、または水素化物等の不純物の逆流を低減することができる。

【0103】

なお、スパッタリングガスは、希ガス(代表的にはアルゴン)、酸素、希ガス及び酸素の混合ガスを適宜用いる。また、スパッタリングガスには、水素、水、水酸基または水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0104】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する塵埃が軽減でき、膜厚分布も均一となるために好ましい。

【0105】

なお、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室でゲート絶縁膜714までが形成された基板700を予備加熱し、基板700に吸着した水分または水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100℃以上400℃以下、好ましくは150℃以上300℃以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、後に行われる絶縁膜723の成膜前に、電極716乃至電極720、電極779及び電極780まで形成した基板700にも同様に行ってもよい。

【0106】

次いで、図5(B)に示すように、酸化物半導体膜をエッチングなどにより所望の形状に加工(パターニング)し、ゲート絶縁膜714上のゲート電極713と重なる位置に島状の酸化物半導体膜715、ゲート絶縁膜714上のゲート電極773と重なる位置に島状の酸化物半導体膜775を形成する。

【0107】

島状の酸化物半導体膜715及び酸化物半導体膜775を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0108】

なお、島状の酸化物半導体膜715及び酸化物半導体膜775を形成するためのエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl2)、三塩化硼素(BCl3)、四塩化珪素(SiCl4)、四塩化炭素(CCl4)など)が好ましい。また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素(CF4)、六弗化硫黄(SF6)、三弗化窒素(NF3)、トリフルオロメタン(CHF3)など)、臭化水素(HBr)、酸素(O2)、これらのガスにヘリウム(He)やアルゴン(Ar)などの希ガスを添加したガス、などを用いることができる。

【0109】

ドライエッチング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。所望の加工形状にエッチングできるように、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節する。

【0110】

ウェットエッチングに用いるエッチング液として、ITO−07N(関東化学社製)を用いてもよい。また、ウェットエッチング後のエッチング液はエッチングされた材料とともに洗浄によって除去される。その除去された材料を含むエッチング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッチング後の廃液から酸化物半導体膜に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化を図ることができる。

【0111】

なお、次工程の導電膜を形成する前に逆スパッタを行い、酸化物半導体膜715、酸化物半導体膜775、及びゲート絶縁膜714の表面に付着しているレジスト残渣などを除去することが好ましい。

【0112】

なお、スパッタ等で成膜された酸化物半導体膜中には、不純物としての水分または水素が多量に含まれていることがある。水分または水素はドナー準位を形成しやすいため、酸化物半導体にとっては不純物である。そこで、本発明の一態様では、酸化物半導体膜中の水分または水素などの不純物を低減するために、窒素、酸素、超乾燥空気、または希ガス(アルゴン、ヘリウムなど)の雰囲気下において、酸化物半導体膜715及び酸化物半導体膜775に加熱処理を施す。上記ガスは、水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下であることが望ましい。

【0113】

酸化物半導体膜715及び酸化物半導体膜775に加熱処理を施すことで、酸化物半導体膜715及び酸化物半導体膜775中の水分または水素を脱離させることができる。具体的には、300℃以上700℃以下、好ましくは300℃以上500℃以下で加熱処理を行えば良い。例えば、500℃、3分間以上6分間以下程度で行えばよい。加熱処理にRTA法を用いれば、短時間に脱水化または脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。

【0114】

本実施の形態では、加熱処理装置の一つである電気炉を用いる。

【0115】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

【0116】

なお、加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水分または水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0117】

以上の工程により、酸化物半導体膜715及び酸化物半導体膜775中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体膜の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、キャリア密度が極端に少なく、バンドギャップの広い酸化物半導体膜を形成することができる。このため、大面積基板を用いてトランジスタを作製することができ、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体膜を用いることで、耐圧性が高く、オンオフ比の高いトランジスタを作製することができる。

【0118】

なお、酸化物半導体膜を加熱する場合、酸化物半導体膜の材料や加熱条件にもよるが、層内全体が非晶質でなく、またその表面に結晶が形成されることがある。酸化物半導体膜は、酸化物半導体膜の表面に対して略垂直にc軸配向した結晶を含む非単結晶であることが好ましい。

【0119】

次に、絶縁膜708、絶縁膜712、ゲート絶縁膜714を部分的にエッチングすることで、島状の半導体膜702、島状の半導体膜703、配線711に達するコンタクトホールを形成する。

【0120】

そして、酸化物半導体膜715及び酸化物半導体膜775を覆うように、スパッタ法や真空蒸着法で導電膜を形成したあと、エッチング等により該導電膜を加工することで、図5(C)に示すように、ソース電極、ドレイン電極、または配線として機能する電極716乃至電極720、電極779、及び電極780を形成する。

【0121】

なお、電極716及び電極717は、島状の半導体膜702に接している。電極717及び電極718は、島状の半導体膜703に接している。電極719は、配線711及び酸化物半導体膜715に接している。電極720は、酸化物半導体膜715に接している。電極779及び電極780は、酸化物半導体膜775に接している。

【0122】

電極716乃至電極720、電極779、及び電極780となる導電膜の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンからから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、アルミニウム、銅などの金属膜の下側もしくは上側にクロム、タンタル、チタン、モリブデン、タングステンなどの高融点金属膜を積層させた構成としても良い。また、アルミニウムまたは銅は、耐熱性や腐食性の問題を回避するために、高融点金属材料と組み合わせて用いると良い。高融点金属材料としては、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム、イットリウム等を用いることができる。

【0123】

また、導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、さらにその上にチタン膜を成膜する3層構造などが挙げられる。

【0124】

また、電極716乃至電極720、電極779、及び電極780となる導電膜としては、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム、酸化スズ、酸化亜鉛、酸化インジウム酸化スズ、酸化インジウム酸化亜鉛または当該金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

【0125】

導電膜形成後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

【0126】

なお、導電膜のエッチングの際に、酸化物半導体膜715及び酸化物半導体膜775がなるべく除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。エッチング条件によっては、島状の酸化物半導体膜715及び酸化物半導体膜775の露出した部分が一部エッチングされることで、溝部(凹部)が形成されることもある。

【0127】

本実施の形態では、導電膜にチタン膜を用いる。そのため、アンモニアと過酸化水素水を含む溶液(過水アンモニウム)を用いて、選択的に導電膜をウェットエッチングすることができる。或いは、塩素(Cl2)、塩化硼素(BCl3)などを含むガスを用いて、導電膜をドライエッチングしても良い。

【0128】

なお、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光に多段階の強度をもたせる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

【0129】

次いで、N2O、N2、またはArなどのガスを用いたプラズマ処理を行う。このプラズマ処理によって露出している酸化物半導体膜の表面に付着した吸着水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

【0130】

なお、プラズマ処理を行った後、図6(A)に示すように、電極716乃至電極720、電極779、及び電極780と、酸化物半導体膜715及び酸化物半導体膜775とを覆うように、絶縁膜723を形成する。絶縁膜723は、水分や、水素、酸素などの不純物を極力含まないことが望ましく、単層の絶縁膜であっても良いし、積層された複数の絶縁膜で構成されていても良い。絶縁膜723に水素が含まれると、その水素が酸化物半導体膜へ侵入し、又は水素が酸化物半導体膜中の酸素を引き抜き、酸化物半導体膜のバックチャネル部が低抵抗化(n型化)してしまい、寄生チャネルが形成されるおそれがある。よって、絶縁膜723はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。上記絶縁膜723には、バリア性の高い材料を用いるのが望ましい。例えば、バリア性の高い絶縁膜として、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などを用いることができる。

【0131】

また絶縁膜723として複数の積層された絶縁膜を用いる場合は、窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を、上記バリア性の高い絶縁膜よりも、酸化物半導体膜715及び酸化物半導体膜775に近い側に形成する。そして、窒素の含有比率が低い絶縁膜を間に挟んで、電極716乃至電極720、電極779、及び電極780、並びに酸化物半導体膜715及び酸化物半導体膜775と重なるように、バリア性の高い絶縁膜を形成する。バリア性の高い絶縁膜を用いることで、酸化物半導体膜715内、酸化物半導体膜775内、ゲート絶縁膜714内、酸化物半導体膜715と他の絶縁膜の界面とその近傍、或いは、酸化物半導体膜775と他の絶縁膜の界面とその近傍に、水分または水素などの不純物が入り込むのを防ぐことができる。また、酸化物半導体膜715及び酸化物半導体膜775に接するように窒素の比率が低い酸化窒化珪素膜などの絶縁膜を形成することで、バリア性の高い材料を用いた絶縁膜が、直接、酸化物半導体膜715及び酸化物半導体膜775に接するのを防ぐことができる。

【0132】

本実施の形態では、スパッタ法で形成された膜厚200nmの酸化珪素膜上に、スパッタ法で形成された膜厚100nmの窒化珪素膜を積層させた構造を有する、絶縁膜723を形成する。成膜時の基板温度は、室温以上300℃以下とすればよく、本実施の形態では100℃とする。

【0133】

なお、絶縁膜723を形成した後に、加熱処理を施しても良い。加熱処理は、窒素、超乾燥空気、または希ガス(アルゴン、ヘリウムなど)の雰囲気下において、好ましくは200℃以上400℃以下、例えば250℃以上350℃以下で行う。上記ガスは、水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下であることが望ましい。本実施の形態では、例えば、窒素雰囲気下で250℃、1時間の加熱処理を行う。或いは、電極716乃至電極720、電極779、及び電極780を形成する前に、水分または水素を低減させるための酸化物半導体膜に対して行った先の加熱処理と同様に、高温短時間のRTA処理を行っても良い。酸素を含む絶縁膜723が設けられた後に、加熱処理が施されることによって、酸化物半導体膜に対して行った先の加熱処理により、酸化物半導体膜715及び酸化物半導体膜775に酸素欠損が発生していたとしても、絶縁膜723から酸化物半導体膜715及び酸化物半導体膜775に酸素が供与される。そして、酸化物半導体膜715及び酸化物半導体膜775に酸素が供与されることで、酸化物半導体膜715及び酸化物半導体膜775において、ドナーとなる酸素欠損を低減し、化学量論比を満たす構成とすること、またそれ以上に酸素が含まれる構成とすることが可能である。酸化物半導体膜715及び酸化物半導体膜775には化学量論比を超える量の酸素が含まれていることが好ましい。その結果、酸化物半導体膜715及び酸化物半導体膜775をi型に近づけることができ、酸素欠損によるトランジスタの電気特性のばらつきを軽減し、電気特性の向上を実現することができる。この加熱処理を行うタイミングは、絶縁膜723の形成後であれば特に限定されず、他の工程、例えば樹脂膜形成時の加熱処理や、透明導電膜を低抵抗化させるための加熱処理と兼ねることで、工程数を増やすことなく、酸化物半導体膜715及び酸化物半導体膜775をi型に近づけることができる。

【0134】

また、酸素雰囲気下で酸化物半導体膜715及び酸化物半導体膜775に加熱処理を施すことで、酸化物半導体に酸素を添加し、酸化物半導体膜715中及び酸化物半導体膜775中それぞれにおいてドナーとなる酸素欠損を低減させても良い。加熱処理の温度は、例えば100℃以上350℃未満、好ましくは150℃以上250℃未満で行う。上記酸素雰囲気下の加熱処理に用いられる酸素ガスには、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち酸素中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0135】

或いは、イオン注入法またはイオンドーピング法などを用いて、酸化物半導体膜715及び酸化物半導体膜775に酸素を添加することで、ドナーとなる酸素欠損を低減させても良い。例えば、2.45GHzのマイクロ波でプラズマ化した酸素を酸化物半導体膜715及び酸化物半導体膜775に添加すれば良い。

【0136】

以上の工程により、酸化物半導体トランジスタ724及び酸化物半導体トランジスタ781が形成される。

【0137】

酸化物半導体トランジスタ724は、ゲート電極713と、ゲート電極713上のゲート絶縁膜714と、ゲート絶縁膜714上においてゲート電極713と重なっている酸化物半導体膜715と、酸化物半導体膜715上に形成された一対の電極719及び電極720と、酸化物半導体膜715上に形成された絶縁膜723とを有する。

【0138】

同様に、酸化物半導体トランジスタ781は、ゲート電極773と、ゲート電極773上のゲート絶縁膜714と、ゲート絶縁膜714上においてゲート電極773と重なっている酸化物半導体膜775と、酸化物半導体膜775上に形成された一対の電極779及び電極780と、酸化物半導体膜775上に形成された絶縁膜723とを有する。

【0139】

なお図6(A)に示す酸化物半導体トランジスタ724は、電極719と電極720の間において、酸化物半導体膜715の一部がエッチングされたチャネルエッチ構造である。同様に、図6(A)に示す酸化物半導体トランジスタ781は、電極779と電極780の間において、酸化物半導体膜775の一部がエッチングされたチャネルエッチ構造である。

【0140】

なお、酸化物半導体トランジスタ724及び酸化物半導体トランジスタ781はそれぞれ、シングルゲート構造のトランジスタを用いて説明したが、必要に応じて、電気的に接続された複数のゲート電極を有することで、チャネル形成領域を複数有する、マルチゲート構造のトランジスタも形成することができる。

【0141】

図6(A)に示すnチャネル型トランジスタ704及びpチャネル型トランジスタ705は、図2乃至図4に示すオペアンプ112を構成するトランジスタ、図6(A)に示す酸化物半導体トランジスタ724は、図1乃至図4に示すトランジスタ101、並びに、図6(A)に示す酸化物半導体トランジスタ781は、図1及び図2のトランジスタ124、図3のトランジスタ144、図4のトランジスタ154として用いることができる。

【0142】

これにより、オペアンプ112を構成するトランジスタ、並びに、酸化物半導体トランジスタであるトランジスタ101、及び電圧変換回路のトランジスタ(トランジスタ124、トランジスタ144、及びトランジスタ154)を、絶縁膜712を介して同一基板700上に積層することができる。これにより、DC−DCコンバータの占有面積の増大を抑制することができる。

【0143】

また、酸化物半導体トランジスタであるトランジスタ101、及び電圧変換回路のトランジスタ(トランジスタ124、トランジスタ144、及びトランジスタ154)を同じ作製工程で作製することができるので、作製工程及び作製コストを低減させることができる。

【0144】

図6(B)に図6(A)とは異なる構成を有する積層構造を示す。

【0145】

図6(B)には、nチャネル型トランジスタ704、pチャネル型トランジスタ705が示されている。さらに図6(B)には、nチャネル型トランジスタ704及びpチャネル型トランジスタ705上に、酸化物半導体膜を用いたチャネル保護構造の、ボトムゲート型の酸化物半導体トランジスタ725及び酸化物半導体トランジスタ751が形成されている。

【0146】

酸化物半導体トランジスタ725は、絶縁膜712上に形成されたゲート電極730と、ゲート電極730上のゲート絶縁膜731と、ゲート絶縁膜731上においてゲート電極730と重なっている島状の酸化物半導体膜732と、ゲート電極730と重なる位置において島状の酸化物半導体膜732上に形成されたチャネル保護膜733と、酸化物半導体膜732上に形成された電極734及び電極735と、電極734、電極735及びチャネル保護膜733上に形成された絶縁膜736を有する。

【0147】

酸化物半導体トランジスタ751は、絶縁膜712上に形成されたゲート電極750と、ゲート電極750上のゲート絶縁膜731と、ゲート絶縁膜731上においてゲート電極750と重なっている島状の酸化物半導体膜752と、ゲート電極750と重なる位置において島状の酸化物半導体膜752上に形成されたチャネル保護膜753と、酸化物半導体膜752上に形成された電極754及び電極755と、電極754、電極755及びチャネル保護膜753上に形成された絶縁膜736を有する。

【0148】

チャネル保護膜733及びチャネル保護膜753を設けることによって、酸化物半導体膜732及び酸化物半導体膜752それぞれのチャネル形成領域となる部分に対する、後の工程における、エッチング時のプラズマやエッチング剤による膜減りなどのダメージを防ぐことができる。従ってトランジスタの信頼性を向上させることができる。

【0149】

チャネル保護膜733及びチャネル保護膜753には、酸素を含む無機材料(酸化珪素、窒化酸化珪素、酸化窒化珪素、酸化アルミニウム、または酸化窒化アルミニウムなど)を用いることができる。チャネル保護膜733及びチャネル保護膜753は、プラズマCVD法や熱CVD法などの気相成長法やスパッタリング法を用いて形成することができる。チャネル保護膜733及びチャネル保護膜753は成膜後にエッチングにより形状を加工する。ここでは、スパッタ法により酸化珪素膜を形成し、フォトリソグラフィによるマスクを用いてエッチング加工することでチャネル保護膜733及びチャネル保護膜753を形成する。

【0150】

酸素を含む無機材料をチャネル保護膜733及びチャネル保護膜753に用いることで、水分または水素を低減させるための加熱処理により、酸化物半導体膜732及び酸化物半導体膜752中に酸素欠損が発生していたとしても、酸化物半導体膜732にチャネル保護膜733から酸素を供給し、並びに、酸化物半導体膜752にチャネル保護膜753から酸素を供給し、ドナーとなる酸素欠損を低減して化学量論比を満たす構成、またはそれ以上に酸素が含まれる構成とすることが可能である。酸化物半導体膜732及び酸化物半導体膜752には、化学量論比を超える量の酸素が含まれていることが好ましい。よって、チャネル形成領域を、i型に近づけることができる。チャネル形成領域をi型に近づけることにより、酸素欠損による酸化物半導体トランジスタ725及び酸化物半導体トランジスタ751の電気特性のばらつきを軽減し、電気特性の向上を実現することができる。

【0151】

図6(B)に示すnチャネル型トランジスタ704及びpチャネル型トランジスタ705は、図2乃至図4に示すオペアンプ112を構成するトランジスタ、図6(B)に示す酸化物半導体トランジスタ725は、図1乃至図4に示すトランジスタ101、並びに、図6(B)に示す酸化物半導体トランジスタ751は、図1及び図2のトランジスタ124、図3のトランジスタ144、図4のトランジスタ154として用いることができる。

【0152】

これにより、オペアンプ112を構成するトランジスタ、並びに、酸化物半導体トランジスタであるトランジスタ101、及び電圧変換回路のトランジスタ(トランジスタ124、トランジスタ144、及びトランジスタ154)を、絶縁膜712を介して同一基板700上に積層することができるので、DC−DCコンバータの占有面積の増大を抑制することができる。

【0153】

また、酸化物半導体トランジスタであるトランジスタ101、及び電圧変換回路のトランジスタ(トランジスタ124、トランジスタ144、及びトランジスタ154)を同じ作製工程で作製することができるので、作製工程及び作製コストを低減させることができる。

【0154】

図6(C)には、nチャネル型トランジスタ704及びpチャネル型トランジスタ705が示されている。さらに図6(C)では、nチャネル型トランジスタ704及びpチャネル型トランジスタ705上に、酸化物半導体膜を用いたボトムコンタクト型の酸化物半導体トランジスタ726及び酸化物半導体トランジスタ760が形成されている。

【0155】

酸化物半導体トランジスタ726は、絶縁膜712上に形成されたゲート電極741と、ゲート電極741上のゲート絶縁膜742と、ゲート絶縁膜742上の電極743及び電極744と、ゲート絶縁膜742を間に挟んでゲート電極741と重なっている酸化物半導体膜745と、酸化物半導体膜745上に形成された絶縁膜746を有する。

【0156】

酸化物半導体トランジスタ760は、絶縁膜712上に形成されたゲート電極761と、ゲート電極761上のゲート絶縁膜742と、ゲート絶縁膜742上の電極763及び電極764と、ゲート絶縁膜742を間に挟んでゲート電極761と重なっている酸化物半導体膜765と、酸化物半導体膜765上に形成された絶縁膜746を有する。

【0157】

図6(C)に示すnチャネル型トランジスタ704及びpチャネル型トランジスタ705は、図2乃至図4に示すオペアンプ112を構成するトランジスタ、図6(C)に示す酸化物半導体トランジスタ726は、図1乃至図4に示すトランジスタ101、並びに、図6(C)に示す酸化物半導体トランジスタ760は、図1及び図2のトランジスタ124、図3のトランジスタ144、図4のトランジスタ154として用いることができる。

【0158】

これにより、オペアンプ112を構成するトランジスタ、並びに、酸化物半導体トランジスタであるトランジスタ101、及び電圧変換回路のトランジスタ(トランジスタ124、トランジスタ144、及びトランジスタ154)を、絶縁膜712を介して同一基板700上に積層することができるので、DC−DCコンバータの占有面積の増大を抑制することができる。

【0159】

また、酸化物半導体トランジスタであるトランジスタ101、及び電圧変換回路のトランジスタ(トランジスタ124、トランジスタ144、及びトランジスタ154)を同じ作製工程で作製することができるので、作製工程及び作製コストを低減させることができる。

【符号の説明】

【0160】

101 トランジスタ

102 入力端子

110 内部電圧生成回路

111 制御回路

112 オペアンプ

113 抵抗

114 抵抗

115 端子

121 電圧変換回路

122 コイル

123 ダイオード

124 トランジスタ

125 コンデンサ

130 内部制御回路

131 出力端子

141 電圧変換回路

142 コイル

143 ダイオード

144 トランジスタ

145 コンデンサ

146 コイル

149 トランス

151 電圧変換回路

152 コイル

153 ダイオード

154 トランジスタ

155 コンデンサ

156 コイル

157 ダイオード

158 コイル

159 トランス

700 基板

701 絶縁膜

702 半導体膜

703 半導体膜

704 nチャネル型トランジスタ

705 pチャネル型トランジスタ

706 ゲート電極

707 ゲート電極

708 絶縁膜

711 配線

712 絶縁膜

713 ゲート電極

714 ゲート絶縁膜

715 酸化物半導体膜

716 電極

717 電極

718 電極

719 電極

720 電極

723 絶縁膜

724 酸化物半導体トランジスタ

725 酸化物半導体トランジスタ

726 酸化物半導体トランジスタ

730 ゲート電極

731 ゲート絶縁膜

732 酸化物半導体膜

733 チャネル保護膜

734 電極

735 電極

736 絶縁膜

741 ゲート電極

742 ゲート絶縁膜

743 電極

744 電極

745 酸化物半導体膜

746 絶縁膜

750 ゲート電極

751 酸化物半導体トランジスタ

752 酸化物半導体膜

753 チャネル保護膜

754 電極

755 電極

760 酸化物半導体トランジスタ

761 ゲート電極

763 電極

764 電極

765 酸化物半導体膜

773 ゲート電極

775 酸化物半導体膜

779 電極

780 電極

781 酸化物半導体トランジスタ

【技術分野】

【0001】

開示される発明の一態様は、DC−DCコンバータ及びその作製方法に関する。

【背景技術】

【0002】

近年、直流電源を必要とする機器の多様化により、入力電圧とは異なる直流電圧で駆動する回路を駆動するためにDC−DCコンバータが多用されている(特許文献1、特許文献2、及び特許文献3参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−148129号公報

【特許文献2】特開2003−235251号公報

【特許文献3】特開2009−254110号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

DC−DCコンバータには、電圧変換回路と当該電圧変換回路を制御する制御回路が含まれる。電圧変換回路の素子には、高い電圧が印加されるため高耐圧なパワーデバイスを用いる。このようなパワーデバイスを用いた電圧変換回路は、高い入力電圧のみで駆動させることが可能である。このようなパワーデバイスとして、例えば酸化物半導体材料を用いた素子(さらに例えば、酸化物半導体膜をチャネル形成領域に用いたトランジスタ)が挙げられる。

【0005】

一方、電圧変換回路を制御する制御回路の素子では、高い駆動速度が求められる。このような高い駆動速度を得ることができる素子としては、例えば珪素材料を用いた素子(例えば珪素膜をチャネル形成領域に用いるトランジスタや、単結晶シリコン基板を用いて形成されたトランジスタ)が挙げられる。しかしながら珪素材料を用いた素子は、高耐圧ではないので高電圧を印加できない。

【0006】

珪素はバンドギャップが狭いため、高電圧を印加すると、電子が雪崩的に発生するアバランシェ降伏が起こる恐れがある。アバランシェ降伏が起こると、その素子は破壊されてしまう。一方、酸化物半導体は、バンドギャップが広いため、アバランシェ降伏が生じにくく、素子が破壊される恐れが小さい。

【0007】

ここで、単一の高い入力電圧のみで、電圧変換回路及び制御回路を有するDC−DCコンバータを動作させる場合を考える。入力電圧が単一であることは、DC−DCコンバータの占有面積を縮小する上で好ましい。しかしながら、当該高い入力電圧は、電圧変換回路は駆動できるものの、制御回路の電圧として高すぎるため制御回路を破壊する恐れがある。よって、当該単一の高い入力電圧のみで電圧変換回路及び制御回路を有するDC−DCコンバータを動作させることは難しい。

【0008】

そのため、高い入力電圧が印加される入力端子と制御回路との間に当該高い入力電圧の電圧を降下させる素子を設ける。降下させた電圧を制御回路に供給すれば、制御回路を破壊する恐れがなくなる。

【0009】

このような高い入力電圧の電圧を降下させる素子として、上述のパワーデバイスを用いればよい。しかし制御回路と当該高い入力電圧の電圧値を降下させるパワーデバイスを設けるということは、DC−DCコンバータの占有面積を増大させる恐れがある。

【0010】

以上を鑑みて、開示される発明の一態様では、単一な高電圧の入力電圧で駆動し、電圧変換回路及び制御回路を有するDC−DCコンバータを得ることを課題の一とする。

【0011】

また開示される発明の一態様では、DC−DCコンバータの占有面積の増大を抑制することを課題の一とする。

【0012】

また開示される発明の一態様では、電圧変換回路のパワーデバイスと入力電圧の電圧を降下させるパワーデバイスを同工程で作製することによって、作製工程及び作製コストを低減させることを課題の一とする。

【課題を解決するための手段】

【0013】

当該単一の高い入力電圧の電圧値を降下させるパワーデバイス及び電圧変換回路のパワーデバイスとして、高耐圧の半導体素子である酸化物半導体材料を用いた素子を用い、また制御回路の素子として低耐圧の半導体素子、例えば珪素材料を用いた素子、を用いる。また当該パワーデバイス及び制御回路の素子を重畳させる。

【0014】

制御回路の素子として低耐圧の半導体素子、例えば珪素材料を用いた素子を用いても、当該パワーデバイスが高電圧の入力電圧の電圧値を降下させるので、制御回路が破壊される恐れはない。

【0015】

当該パワーデバイス及び制御回路の素子を重畳させるため、DC−DCコンバータの占有面積の増大を抑制することが可能である。

【0016】

また開示される発明の一態様では、電圧変換回路のパワーデバイスである酸化物半導体材料を用いた素子と入力電圧の電圧を降下させるパワーデバイスである酸化物半導体材料を用いた素子を、同じ工程で作製する。これにより、作製工程及び作製コストを低減させることができる。

【0017】

開示される発明の一態様は、入力電圧が印加される入力端子と、当該入力端子と接続され、第1のトランジスタを有する電圧変換回路と、当該電圧変換回路を制御し、珪素材料をチャネル形成領域に有する第2のトランジスタを有する制御回路と、当該入力端子と当該制御回路との間に設けられ、当該入力電圧を当該入力電圧より低い電圧である電源電圧に変換する第3のトランジスタとを有し、当該第1のトランジスタ及び当該第3のトランジスタは、酸化物半導体材料をチャネル形成領域に有するトランジスタであり、当該第2のトランジスタ、並びに、当該第1のトランジスタ及び当該第3のトランジスタは、絶縁膜を介して積層されていることを特徴とするDC−DCコンバータに関する。

【0018】

開示される発明の一態様は、絶縁表面上に、珪素材料を第1のチャネル形成領域に用いた第1のトランジスタを形成し、当該第1のトランジスタを覆って、絶縁膜を形成し、当該絶縁膜上に、酸化物半導体材料を第2のチャネル形成領域として用いた第2のトランジスタ、及び当該酸化物半導体材料を第3のチャネル形成領域として用いた第3のトランジスタを形成し、当該第2のトランジスタは電圧変換回路を構成し、当該第1のトランジスタは、当該電圧変換回路を制御する制御回路を構成し、当該第3のトランジスタは、入力端子と当該制御回路との間に設けられ、当該入力端子に印加される入力電圧を当該入力電圧より低い電圧である電源電圧に変換することを特徴とするDC−DCコンバータの作製方法に関する。

【0019】

開示される発明の一態様において、当該酸化物半導体材料は、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系酸化物半導体、二元系金属の酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体、一元系金属の酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体のいずれかであることを特徴とする。

【0020】

開示される発明の一態様において、当該電圧変換回路は、降圧型の電圧変換回路であることを特徴とする。

【0021】

開示される発明の一態様において、当該電圧変換回路は、フライバック型の電圧変換回路であることを特徴とする。

【0022】

開示される発明の一態様において、当該電圧変換回路は、フォワード型の電圧変換回路であることを特徴とする。

【0023】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【発明の効果】

【0024】

開示される発明により、単一な高電圧の入力電圧で駆動し、電圧変換回路及び制御回路を有するDC−DCコンバータを得ることができる。

【0025】

開示される発明の一態様により、DC−DCコンバータの占有面積の増大を抑制することができる。

【0026】

開示される発明の一態様では、電圧変換回路のパワーデバイスと入力電圧の電圧を降下させるパワーデバイスを同工程で作製するので、作製工程及び作製コストを低減させることができる。

【図面の簡単な説明】

【0027】

【図1】DC−DCコンバータの回路図。

【図2】DC−DCコンバータの回路図。

【図3】DC−DCコンバータの回路図。

【図4】DC−DCコンバータの回路図。

【図5】トランジスタの積層構造を示す断面図。

【図6】トランジスタの積層構造を示す断面図。

【発明を実施するための形態】

【0028】

以下、本明細書に開示された発明の実施の態様について、図面を参照して説明する。但し、本明細書に開示された発明は多くの異なる態様で実施することが可能であり、本明細書に開示された発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0029】

なお本明細書に開示された発明において、半導体装置とは、半導体を利用することで機能する素子及び装置全般を指し、電子回路、表示装置、発光装置等を含む電気装置およびその電気装置を搭載した電子機器をその範疇とする。

【0030】

<回路構成>

図1に示すDC−DCコンバータは、制御回路111、電圧変換回路121、入力電圧Vinが印加される入力端子102、酸化物半導体材料をチャネル形成領域に用いたトランジスタ、例えば、酸化物半導体膜をチャネル形成領域に有するトランジスタ(以下、酸化物半導体トランジスタと呼ぶ)であるトランジスタ101、電圧変換回路121から出力される出力電圧Voutを出力する出力端子131を有する。

【0031】

トランジスタ101のソース又はドレインの一方は、入力電圧Vinが印加される入力端子102、及び、電圧変換回路121のトランジスタ124のソース又はドレインの一方に接続されている。トランジスタ101のソース又はドレインの他方、及びゲートは、制御回路111に接続されている。

【0032】

酸化物半導体トランジスタであるトランジスタ101は、高電圧を扱うことのできるパワーデバイスである。トランジスタ101のソース又はドレインの一方に印加された入力電圧Vinは、ゲートに印加されたゲート電圧に基づいて、入力電圧Vinよりも小さい値を有する電源電圧VDDに変換される。

【0033】

入力電圧Vinとして、例えば家庭用電源からの電圧を交流−直流変換(AC−DC変換)した電圧を用いる。入力電圧Vinとして、家庭用電源からの電圧を交流−直流変換した電圧を用いるとすると、入力電圧Vinの実効値は141Vである。そのため、このような高電圧である入力電圧Vinは、制御回路111を破壊する恐れがある。よって入力電圧Vinが印加される入力端子102と制御回路111との間に、高耐圧のパワーデバイスである酸化物半導体トランジスタを配置することは、制御回路111が破壊されることを抑制できる。

【0034】

トランジスタ101は、上述のように酸化物半導体膜をチャネル形成領域に有するトランジスタである。

【0035】

このような酸化物半導体膜の材料として、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体や、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系酸化物半導体や、二元系金属の酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体や、一元系金属の酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体などを用いることができる。なお、酸化物半導体膜をチャネル形成領域に有するトランジスタ(酸化物半導体トランジスタ)の構造及び作製工程については後述する。

【0036】

制御回路111は、トランジスタ101のソース又はドレインの他方、トランジスタ101のゲート、及び、電圧変換回路121に電気的に接続されている。さらに制御回路111は、電源電圧VDDよりも小さい値を有する電源電圧VSSが印加される。電源電圧VSSとして、例えば接地電圧GNDを用いればよい。

【0037】

図2に、図1に示す制御回路111の詳細な回路構成の例を示す。

【0038】

図2の制御回路111は、内部電圧生成回路(「レギュレータ」ともいう)110及び内部制御回路130を有している。内部電圧生成回路110は、電源電圧VDDを生成する回路であり、オペアンプ112、抵抗113、及び抵抗114を有している。

【0039】

オペアンプ112の反転入力端子は、抵抗113の一方の端子、及び、抵抗114の一方の端子に電気的に接続されている。オペアンプ112の非反転入力端子は、参照電圧Vrefが印加される端子115に電気的に接続されている。オペアンプ112の出力端子は、トランジスタ101のゲートに接続されている。

【0040】

オペアンプ112を構成するトランジスタは、高速駆動可能なトランジスタ、例えば珪素材料をチャネル形成領域に用いたトランジスタを用いればよい。なお珪素材料をチャネル形成領域に用いたトランジスタの構造及び作製工程については後述する。

【0041】

珪素材料をチャネル形成領域に用いた場合、nチャネル型トランジスタ及びpチャネル型トランジスタを得ることができる。オペアンプ112を構成するトランジスタとして、珪素をチャネル形成領域に有するトランジスタを用いると、高速駆動可能なだけでなく、nチャネル型トランジスタ及びpチャネル型トランジスタの両方を得ることができる。

【0042】

抵抗113の一方の端子は、オペアンプ112の反転入力端子、及び、抵抗114の一方の端子に電気的に接続されている。抵抗113の他方の端子は、トランジスタ101のソース又はドレインの他方、及び、内部制御回路130の第1の端子に電気的に接続されている。

【0043】

抵抗114の一方の端子は、抵抗113の一方の端子、及び、オペアンプ112の反転入力端子に電気的に接続されている。抵抗114の他方の端子は、電源電圧VSSが印加されている。

【0044】

内部制御回路130は、電圧制御或いは電流制御を行う回路である。電圧制御或いは電流制御の例としては、例えば、パルス幅変調(Pulse Width Modulation(PWM))制御やヒステリシス制御が挙げられる。本実施の形態では、内部制御回路130によって、電源電圧VDDが、トランジスタ124のゲートに印加されるゲート電圧に変換される。当該ゲート電圧に応じ、入力電圧Vinが出力電圧Voutに変換される。

【0045】

内部制御回路130の第1の端子は、トランジスタ101のソース又はドレインの他方、及び抵抗113の他方の端子に電気的に接続されている。内部制御回路130の第2の端子には、電源電圧VSSが印加される。また内部制御回路130の第3の端子は、トランジスタ124のゲートに電気的に接続されている。また図示しないが、内部制御回路130には出力電圧Voutの一部が帰還する。このような出力電圧Voutの一部は、出力電圧Voutを出力する出力端子131に電気的に接続して分圧回路を設け、当該分圧回路によって出力電圧Voutを分圧して生成すればよい。

【0046】

図2の電圧変換回路121は、降圧型の電圧変換回路である。図2の電圧変換回路121は、トランジスタ124、ダイオード123、コイル122、コンデンサ125を有している。

【0047】

トランジスタ124のソース又はドレインの一方は、トランジスタ101のソース又はドレインの一方、及び、入力電圧Vinが印加される入力端子102に接続されている。トランジスタ124のソース又はドレインの他方は、ダイオード123の出力端子、及び、コイル122の一方の端子に電気的に接続されている。トランジスタ124のゲートは、内部制御回路130の第3の端子に電気的に接続されている。

【0048】

トランジスタ124として、トランジスタ101と同様に、パワーデバイスである酸化物半導体トランジスタを用いる。トランジスタ124として酸化物半導体トランジスタを用いることで、高電圧である入力電圧Vinの印加によるトランジスタ124の破壊を抑制することができる。

【0049】

ダイオード123の出力端子は、トランジスタ124のソース又はドレインの他方、及び、コイル122の一方の端子に電気的に接続されている。ダイオード123の入力端子には、電源電圧VSSが印加される。

【0050】

コイル122の一方の端子は、ダイオード123の出力端子、及び、トランジスタ124のソース又はドレインの他方に電気的に接続されている。コイル122の他方の端子は、コンデンサ125の一方の端子、及び、出力電圧Voutを出力する出力端子131に電気的に接続されている。

【0051】

コンデンサ125の一方の端子は、コイル122の他方の端子、及び、出力電圧Voutを出力する出力端子131に電気的に接続されている。コンデンサ125の他方の端子には、電源電圧VSSが印加される。

【0052】

図2では降圧型の電圧変換回路121について説明したが、電圧変換回路121は降圧型に限定されず、必要であれば、降圧型の電圧変換回路に代えて昇圧型の電圧変換回路、又は昇降圧型の電圧変換回路を形成してもよい。

【0053】

図3では、フライバック型の電圧変換回路を用いたDC−DCコンバータについて説明する。

【0054】

図3のDC−DCコンバータは、制御回路111、電圧変換回路141、入力電圧Vinが印加される入力端子102、トランジスタ101、電圧変換回路141から出力される出力電圧Voutを出力する出力端子131を有する。

【0055】

図3の電圧変換回路141は、コイル142及びコイル146を有するトランス149、トランジスタ144、ダイオード143、コンデンサ145を有している。

【0056】

コイル142の一方の端子は、トランジスタ101のソース又はドレインの一方、及び、入力電圧Vinが印加される入力端子102に電気的に接続されている。コイル142の他方の端子は、トランジスタ144のソース又はドレインの一方に電気的に接続されている。

【0057】

トランジスタ144のソース又はドレインの一方は、コイル142の他方の端子に電気的に接続されている。トランジスタ144のソース又はドレインの他方は、電源電圧VSSが印加される。トランジスタ144のゲートは、内部制御回路130の第3の端子に電気的に接続されている。

【0058】

コイル146の一方の端子は、ダイオード143の入力端子に電気的に接続されている。コイル146の他方の端子には、電源電圧VSSが印加される。

【0059】

ダイオード143の入力端子は、コイル146の一方の端子に電気的に接続されている。ダイオード143の出力端子は、コンデンサ145の一方の端子、及び、出力端子131と電気的に接続されている。

【0060】

コンデンサ145の一方の端子は、ダイオード143の出力端子、及び、出力端子131と電気的に接続されている。コンデンサ145の他方の端子には、電源電圧VSSが印加される。

【0061】

以上により、単一な高電圧の入力電圧Vinで駆動し、電圧変換回路141及び制御回路111を有するDC−DCコンバータを得ることができる。

【0062】

図4では、フォワード型の電圧変換回路を用いたDC−DCコンバータについて説明する。

【0063】

図4のDC−DCコンバータは、制御回路111、電圧変換回路151、入力電圧Vinが印加される入力端子102、トランジスタ101、電圧変換回路151から出力される出力電圧Voutを出力する出力端子131を有する。

【0064】

図4の電圧変換回路151は、コイル152及びコイル156を有するトランス159、トランジスタ154、ダイオード153、ダイオード157、コイル158、コンデンサ155を有している。

【0065】

コイル152の一方の端子は、トランジスタ101のソース又はドレインの一方、及び、入力電圧Vinが印加される入力端子102に電気的に接続されている。コイル152の他方の端子は、トランジスタ154のソース又はドレインの一方に電気的に接続されている。

【0066】

トランジスタ154のソース又はドレインの一方は、コイル152の他方の端子に電気的に接続されている。トランジスタ154のソース又はドレインの他方は、電源電圧VSSが印加される。トランジスタ154のゲートは、内部制御回路130の第3の端子に電気的に接続されている。

【0067】

コイル156の一方の端子は、ダイオード153の入力端子に電気的に接続されている。コイル156の他方の端子には、電源電圧VSSが印加される。

【0068】

ダイオード153の入力端子は、コイル156の一方の端子に電気的に接続されている。ダイオード153の出力端子は、ダイオード157の出力端子、及び、コイル158の一方の端子と電気的に接続されている。

【0069】

ダイオード157の出力端子は、ダイオード153の出力端子、及び、コイル158の一方の端子と電気的に接続されている。ダイオード157の入力端子には、電源電圧VSSが印加される。

【0070】

コイル158の一方の端子は、ダイオード153の出力端子、及び、ダイオード157の出力端子と電気的に接続されている。コイル158の他方の端子は、コンデンサ155の一方の端子、及び、出力端子131と電気的に接続されている。

【0071】

コンデンサ155の一方の端子は、コイル158の他方の端子、及び、出力端子131と電気的に接続されている。コンデンサ155の他方の端子には、電源電圧VSSが印加される。

【0072】

以上により、単一な高電圧の入力電圧Vinで駆動し、電圧変換回路151及び制御回路111を有するDC−DCコンバータを得ることができる。

【0073】

<積層構造及びその作製工程>

ここで、オペアンプ112を構成するトランジスタ、及び、酸化物半導体トランジスタであるトランジスタ101を積層した積層構造、並びに、当該積層構造の作製工程を、以下に説明する。なお本実施の形態では、オペアンプ112を構成するトランジスタとして、珪素材料をチャネル形成領域に用いたトランジスタを用いる。

【0074】

まず、図5(A)に示すように、基板700の絶縁表面上に、公知のCMOSの作製方法を用いて、nチャネル型トランジスタ704、pチャネル型トランジスタ705を形成する。本実施の形態では、単結晶の半導体基板から分離された単結晶半導体膜を用いて、nチャネル型トランジスタ704、pチャネル型トランジスタ705を形成する場合を例に挙げている。

【0075】

具体的な単結晶半導体膜の作製方法の一例について、簡単に説明する。まず、単結晶の半導体基板に、加速されたイオンでなるイオンビームを注入する。イオンビームを注入することで、半導体基板の表面から一定の深さの領域の結晶構造が乱される。結晶構造が乱されることにより、局所的に脆弱化された脆化層が形成される。脆化層が形成される領域の深さは、イオンビームの加速エネルギーとイオンビームの入射角によって調節することができる。そして、半導体基板と、絶縁膜701が形成された基板700とを、間に当該絶縁膜701が挟まるように貼り合わせる。貼り合わせは、半導体基板と基板700とを重ね合わせた後、半導体基板と基板700の一部に、1N/cm2以上500N/cm2以下、好ましくは11N/cm2以上20N/cm2以下程度の圧力を加える。圧力を加えると、その部分から半導体基板と絶縁膜701とが接合を開始し、最終的には密着した面全体に接合がおよぶ。次いで、加熱処理を行うことで、脆化層に存在する微小ボイドどうしが結合して、微小ボイドの体積が増大する。その結果、脆化層において半導体基板の一部である単結晶半導体膜が、半導体基板から分離する。上記加熱処理の温度は、基板700の歪み点を越えない温度とする。そして、上記単結晶半導体膜をエッチング等により所望の形状に加工することで、島状の半導体膜702、島状の半導体膜703を形成することができる。

【0076】

nチャネル型トランジスタ704は、絶縁膜701上の島状の半導体膜702を用いて形成されており、pチャネル型トランジスタ705は、絶縁膜701上の島状の半導体膜703を用いて形成されている。また、nチャネル型トランジスタ704はゲート電極706を有しており、pチャネル型トランジスタ705はゲート電極707を有している。そして、nチャネル型トランジスタ704は、島状の半導体膜702とゲート電極706の間に、絶縁膜708を有する。pチャネル型トランジスタ705は、島状の半導体膜703とゲート電極707の間に、絶縁膜708を有する。

【0077】

基板700として使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、基板700には、フュージョン法やフロート法で作製されるガラス基板、石英基板、セラミック基板等を用いることができる。ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いると良い。また、ステンレス基板を含む金属基板またはシリコン基板の表面に絶縁膜を形成したものを用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板は、一般的に上記基板と比較して耐熱温度が低い傾向にあるが、作製工程における処理温度に耐え得るのであれば用いることが可能である。

【0078】

なお、本実施の形態では、単結晶の半導体膜を用いてnチャネル型トランジスタ704とpチャネル型トランジスタ705を形成する例について説明しているが、本発明はこの構成に限定されない。例えば、絶縁膜701上に気相成長法を用いて形成された多結晶の半導体膜を用いても良いし、上記半導体膜を公知の技術により結晶化しても良い。公知の結晶化方法としては、レーザ光を用いたレーザ結晶化法、触媒元素を用いる結晶化法がある。或いは、触媒元素を用いる結晶化法とレーザ結晶化法とを組み合わせて用いることもできる。また、石英のような耐熱性に優れている基板を用いる場合、電熱炉を使用した熱結晶化方法、赤外光を用いたランプアニール結晶化法、触媒元素を用いる結晶化法、950℃程度の高温アニール法を組み合わせた結晶化法を用いても良い。またnチャネル型トランジスタ704とpチャネル型トランジスタ705として、単結晶シリコン基板に、チャネル形成領域、ソース領域、及びドレイン領域を形成したトランジスタを用いても良い。

【0079】

また、図5(A)では、絶縁膜708上に導電膜を形成した後、上記導電膜をエッチング等により所望の形状に加工することで、ゲート電極706及びゲート電極707と共に、配線711を形成する。

【0080】

次いで、図5(A)に示すように、nチャネル型トランジスタ704、pチャネル型トランジスタ705、配線711を覆うように、絶縁膜712を形成する。なお、本実施の形態では、単層の絶縁膜712を用いる場合を例示しているが、上記絶縁膜712は単層である必要はなく、2層以上の絶縁膜を積層させて絶縁膜712として用いても良い。

【0081】

絶縁膜712は、後の作製工程における加熱処理の温度に耐えうる材料を用いる。具体的に、絶縁膜712として、酸化珪素、窒化珪素、窒化酸化珪素、酸化窒化珪素、窒化アルミニウム、酸化アルミニウムなどを用いるのが望ましい。

【0082】

絶縁膜712は、その表面をCMP法などにより平坦化させても良い。

【0083】

次いで、図5(A)に示すように、絶縁膜712上に、酸化物半導体トランジスタ724のゲート電極713、並びに酸化物半導体トランジスタ781のゲート電極773を形成する。酸化物半導体トランジスタ724は、図1乃至図4のトランジスタ101に相当する。酸化物半導体トランジスタ781は、図1及び図2のトランジスタ124、図3のトランジスタ144、図4のトランジスタ154に相当する。

【0084】

ゲート電極713及びゲート電極773それぞれの材料として、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム等の金属材料、これら金属材料を主成分とする合金材料を用いた導電膜、或いはこれら金属の窒化物を、単層で又は積層で用いることができる。なお、後の工程において行われる加熱処理の温度に耐えうるのであれば、上記金属材料としてアルミニウム、銅を用いることもできる。アルミニウムまたは銅は、耐熱性や腐食性の問題を回避するために、高融点金属材料と組み合わせて用いると良い。高融点金属材料としては、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム等を用いることができる。

【0085】

例えば、二層の積層構造を有するゲート電極713及びゲート電極773として、アルミニウム膜上にモリブデン膜が積層された二層の積層構造、銅膜上にモリブデン膜を積層した二層構造、銅膜上に窒化チタン膜若しくは窒化タンタル膜を積層した二層構造、または、窒化チタン膜とモリブデン膜とを積層した二層構造とすることが好ましい。3層の積層構造を有するゲート電極713及びゲート電極773としては、アルミニウム膜、アルミニウムとシリコンの合金膜、アルミニウムとチタンの合金膜またはアルミニウムとネオジムの合金膜を中間層とし、タングステン膜、窒化タングステン膜、窒化チタン膜またはチタン膜を上下層として積層した構造とすることが好ましい。

【0086】

また、ゲート電極713及びゲート電極773としてそれぞれ、酸化インジウム、酸化インジウム酸化スズ、酸化インジウム酸化亜鉛、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、または酸化亜鉛ガリウム等の透光性を有する酸化物導電膜を用いることもできる。

【0087】

ゲート電極713及びゲート電極773それぞれの膜厚は、10nm〜400nm、好ましくは100nm〜200nmとする。本実施の形態では、タングステンターゲットを用いたスパッタ法により150nmのゲート電極用の導電膜を形成した後、該導電膜をエッチングにより所望の形状に加工(パターニング)することで、ゲート電極713及びゲート電極773を形成する。なお、形成されたゲート電極の端部がテーパー形状であると、上に積層するゲート絶縁膜の被覆性が向上するため好ましい。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0088】

次いで、図5(B)に示すように、ゲート電極713及びゲート電極773上に、ゲート絶縁膜714を形成する。ゲート絶縁膜714は、プラズマCVD法又はスパッタリング法等を用いて、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜、酸化ハフニウム膜または酸化タンタル膜を単層で又は積層させて形成することができる。ゲート絶縁膜714は、水分や、水素、酸素などの不純物を極力含まないことが望ましい。スパッタリング法により酸化珪素膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。

【0089】

不純物を除去することによりi型化された酸化物半導体(高純度化された酸化物半導体)は界面準位、界面電荷に対して極めて敏感であるため、高純度化された酸化物半導体とゲート絶縁膜714との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁膜は、高品質化が要求される。

【0090】

例えば、μ波(周波数2.45GHz)を用いた高密度プラズマCVDは、緻密で絶縁耐圧の高い高品質な絶縁膜を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁膜とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

【0091】

もちろん、ゲート絶縁膜714として良質な絶縁膜を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によって膜質や、酸化物半導体との界面特性が改善される絶縁膜であっても良い。いずれにしても、ゲート絶縁膜としての膜質が良好であることは勿論のこと、ゲート絶縁膜と酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

【0092】

バリア性の高い材料を用いた絶縁膜と、窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜とを積層させた構造を有するゲート絶縁膜714を形成しても良い。この場合、酸化珪素膜、酸化窒化珪素膜などの絶縁膜は、バリア性の高い絶縁膜と酸化物半導体膜の間に形成する。バリア性の高い絶縁膜として、例えば窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などが挙げられる。バリア性の高い絶縁膜を用いることで、水分または水素などの雰囲気中の不純物、或いは基板内に含まれるアルカリ金属、重金属などの不純物が、酸化物半導体膜内、ゲート絶縁膜714内、或いは、酸化物半導体膜と他の絶縁膜の界面とその近傍に入り込むのを防ぐことができる。また、酸化物半導体膜に接するように窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を形成することで、バリア性の高い絶縁膜が直接酸化物半導体膜に接するのを防ぐことができる。

【0093】

例えば、第1のゲート絶縁膜としてスパッタリング法により膜厚50nm以上200nm以下の窒化珪素膜(SiNy(y>0))を形成し、第1のゲート絶縁膜上に第2のゲート絶縁膜として膜厚5nm以上300nm以下の酸化珪素膜(SiOx(x>0))を積層して、膜厚100nmのゲート絶縁膜714としても良い。ゲート絶縁膜714の膜厚は、トランジスタに要求される特性によって適宜設定すればよく350nm乃至400nm程度でもよい。

【0094】

本実施の形態では、スパッタ法で形成された膜厚50nmの窒化珪素膜上に、スパッタ法で形成された膜厚100nmの酸化珪素膜を積層させた構造を有する、ゲート絶縁膜714を形成する。

【0095】

なお、ゲート絶縁膜714は後に形成される酸化物半導体膜と接する。酸化物半導体膜は、水素が含有されると特性に悪影響を及ぼすので、ゲート絶縁膜714は水素、水酸基および水分が含まれないことが望ましい。ゲート絶縁膜714に水素、水酸基及び水分がなるべく含まれないようにするためには、成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極713及びゲート電極773が形成された基板700を予備加熱し、基板700に吸着した水分または水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100℃以上400℃以下、好ましくは150℃以上300℃以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。

【0096】

次いで、ゲート絶縁膜714上に、膜厚2nm以上200nm以下、好ましくは膜厚3nm以上50nm以下、さらに好ましくは膜厚3nm以上20nm以下の酸化物半導体膜を形成する。当該酸化物半導体膜から、酸化物半導体トランジスタ724及び酸化物半導体トランジスタ781それぞれのチャネル形成領域が形成される。酸化物半導体膜は、酸化物半導体をターゲットとして用い、スパッタ法により成膜する。また、酸化物半導体膜は、希ガス(例えばアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(例えばアルゴン)及び酸素混合雰囲気下においてスパッタ法により形成することができる。

【0097】

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁膜714の表面に付着している塵埃を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、四フッ化炭素などを加えた雰囲気で行ってもよい。

【0098】

酸化物半導体膜の材料には、上述したように、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体や、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系酸化物半導体や、二元系金属の酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体や、一元系金属の酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体などを用いることができる。

【0099】

本実施の形態では、In(インジウム)、Ga(ガリウム)、及びZn(亜鉛)を含むターゲットを用いたスパッタ法により得られる膜厚30nmのIn−Ga−Zn−O系酸化物半導体の薄膜を、酸化物半導体膜として用いる。上記ターゲットとして、例えば、In2O3:Ga2O3:ZnO=1:1:0.5(mol数比)、In2O3:Ga2O3:ZnO=1:1:1(mol数比)、またはIn2O3:Ga2O3:ZnO=1:1:2(mol数比)であるターゲットを用いることができる。また、In、Ga、及びZnを含むターゲットの充填率は90%以上100%以下、好ましくは95%以上100%未満である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

【0100】

また、ターゲットの純度を、99.99%以上とすることで、酸化物半導体膜に混入するアルカリ金属、水素原子、水素分子、水、水酸基、または水素化物等を低減することができる。また、当該ターゲットを用いることで、酸化物半導体膜において、リチウム、ナトリウム、カリウム等のアルカリ金属の濃度を低減することができる。

【0101】

本実施の形態では、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板700上に酸化物半導体膜を成膜する。成膜時に、基板温度を100℃以上600℃以下、好ましくは200℃以上400℃以下としても良い。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて成膜室を排気すると、例えば、水素原子、水(H2O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

【0102】

また、スパッタリング装置の処理室のリークレートを1×10−10Pa・m3/秒以下とすることで、スパッタリング法による成膜途中における酸化物半導体膜への、アルカリ金属、水素化物等の不純物の混入を低減することができる。また、排気系として吸着型の真空ポンプを用いることで、排気系からアルカリ金属、水素原子、水素分子、水、水酸基、または水素化物等の不純物の逆流を低減することができる。

【0103】

なお、スパッタリングガスは、希ガス(代表的にはアルゴン)、酸素、希ガス及び酸素の混合ガスを適宜用いる。また、スパッタリングガスには、水素、水、水酸基または水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0104】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する塵埃が軽減でき、膜厚分布も均一となるために好ましい。

【0105】

なお、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室でゲート絶縁膜714までが形成された基板700を予備加熱し、基板700に吸着した水分または水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100℃以上400℃以下、好ましくは150℃以上300℃以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、後に行われる絶縁膜723の成膜前に、電極716乃至電極720、電極779及び電極780まで形成した基板700にも同様に行ってもよい。

【0106】

次いで、図5(B)に示すように、酸化物半導体膜をエッチングなどにより所望の形状に加工(パターニング)し、ゲート絶縁膜714上のゲート電極713と重なる位置に島状の酸化物半導体膜715、ゲート絶縁膜714上のゲート電極773と重なる位置に島状の酸化物半導体膜775を形成する。

【0107】

島状の酸化物半導体膜715及び酸化物半導体膜775を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0108】

なお、島状の酸化物半導体膜715及び酸化物半導体膜775を形成するためのエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl2)、三塩化硼素(BCl3)、四塩化珪素(SiCl4)、四塩化炭素(CCl4)など)が好ましい。また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素(CF4)、六弗化硫黄(SF6)、三弗化窒素(NF3)、トリフルオロメタン(CHF3)など)、臭化水素(HBr)、酸素(O2)、これらのガスにヘリウム(He)やアルゴン(Ar)などの希ガスを添加したガス、などを用いることができる。

【0109】

ドライエッチング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。所望の加工形状にエッチングできるように、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節する。

【0110】

ウェットエッチングに用いるエッチング液として、ITO−07N(関東化学社製)を用いてもよい。また、ウェットエッチング後のエッチング液はエッチングされた材料とともに洗浄によって除去される。その除去された材料を含むエッチング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッチング後の廃液から酸化物半導体膜に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化を図ることができる。

【0111】

なお、次工程の導電膜を形成する前に逆スパッタを行い、酸化物半導体膜715、酸化物半導体膜775、及びゲート絶縁膜714の表面に付着しているレジスト残渣などを除去することが好ましい。

【0112】

なお、スパッタ等で成膜された酸化物半導体膜中には、不純物としての水分または水素が多量に含まれていることがある。水分または水素はドナー準位を形成しやすいため、酸化物半導体にとっては不純物である。そこで、本発明の一態様では、酸化物半導体膜中の水分または水素などの不純物を低減するために、窒素、酸素、超乾燥空気、または希ガス(アルゴン、ヘリウムなど)の雰囲気下において、酸化物半導体膜715及び酸化物半導体膜775に加熱処理を施す。上記ガスは、水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下であることが望ましい。

【0113】

酸化物半導体膜715及び酸化物半導体膜775に加熱処理を施すことで、酸化物半導体膜715及び酸化物半導体膜775中の水分または水素を脱離させることができる。具体的には、300℃以上700℃以下、好ましくは300℃以上500℃以下で加熱処理を行えば良い。例えば、500℃、3分間以上6分間以下程度で行えばよい。加熱処理にRTA法を用いれば、短時間に脱水化または脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。

【0114】

本実施の形態では、加熱処理装置の一つである電気炉を用いる。

【0115】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

【0116】

なお、加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水分または水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0117】

以上の工程により、酸化物半導体膜715及び酸化物半導体膜775中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体膜の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、キャリア密度が極端に少なく、バンドギャップの広い酸化物半導体膜を形成することができる。このため、大面積基板を用いてトランジスタを作製することができ、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体膜を用いることで、耐圧性が高く、オンオフ比の高いトランジスタを作製することができる。

【0118】

なお、酸化物半導体膜を加熱する場合、酸化物半導体膜の材料や加熱条件にもよるが、層内全体が非晶質でなく、またその表面に結晶が形成されることがある。酸化物半導体膜は、酸化物半導体膜の表面に対して略垂直にc軸配向した結晶を含む非単結晶であることが好ましい。

【0119】

次に、絶縁膜708、絶縁膜712、ゲート絶縁膜714を部分的にエッチングすることで、島状の半導体膜702、島状の半導体膜703、配線711に達するコンタクトホールを形成する。

【0120】

そして、酸化物半導体膜715及び酸化物半導体膜775を覆うように、スパッタ法や真空蒸着法で導電膜を形成したあと、エッチング等により該導電膜を加工することで、図5(C)に示すように、ソース電極、ドレイン電極、または配線として機能する電極716乃至電極720、電極779、及び電極780を形成する。

【0121】

なお、電極716及び電極717は、島状の半導体膜702に接している。電極717及び電極718は、島状の半導体膜703に接している。電極719は、配線711及び酸化物半導体膜715に接している。電極720は、酸化物半導体膜715に接している。電極779及び電極780は、酸化物半導体膜775に接している。

【0122】

電極716乃至電極720、電極779、及び電極780となる導電膜の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンからから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、アルミニウム、銅などの金属膜の下側もしくは上側にクロム、タンタル、チタン、モリブデン、タングステンなどの高融点金属膜を積層させた構成としても良い。また、アルミニウムまたは銅は、耐熱性や腐食性の問題を回避するために、高融点金属材料と組み合わせて用いると良い。高融点金属材料としては、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム、イットリウム等を用いることができる。

【0123】

また、導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、さらにその上にチタン膜を成膜する3層構造などが挙げられる。

【0124】

また、電極716乃至電極720、電極779、及び電極780となる導電膜としては、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム、酸化スズ、酸化亜鉛、酸化インジウム酸化スズ、酸化インジウム酸化亜鉛または当該金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

【0125】

導電膜形成後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

【0126】

なお、導電膜のエッチングの際に、酸化物半導体膜715及び酸化物半導体膜775がなるべく除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。エッチング条件によっては、島状の酸化物半導体膜715及び酸化物半導体膜775の露出した部分が一部エッチングされることで、溝部(凹部)が形成されることもある。

【0127】

本実施の形態では、導電膜にチタン膜を用いる。そのため、アンモニアと過酸化水素水を含む溶液(過水アンモニウム)を用いて、選択的に導電膜をウェットエッチングすることができる。或いは、塩素(Cl2)、塩化硼素(BCl3)などを含むガスを用いて、導電膜をドライエッチングしても良い。

【0128】

なお、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光に多段階の強度をもたせる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

【0129】

次いで、N2O、N2、またはArなどのガスを用いたプラズマ処理を行う。このプラズマ処理によって露出している酸化物半導体膜の表面に付着した吸着水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

【0130】

なお、プラズマ処理を行った後、図6(A)に示すように、電極716乃至電極720、電極779、及び電極780と、酸化物半導体膜715及び酸化物半導体膜775とを覆うように、絶縁膜723を形成する。絶縁膜723は、水分や、水素、酸素などの不純物を極力含まないことが望ましく、単層の絶縁膜であっても良いし、積層された複数の絶縁膜で構成されていても良い。絶縁膜723に水素が含まれると、その水素が酸化物半導体膜へ侵入し、又は水素が酸化物半導体膜中の酸素を引き抜き、酸化物半導体膜のバックチャネル部が低抵抗化(n型化)してしまい、寄生チャネルが形成されるおそれがある。よって、絶縁膜723はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。上記絶縁膜723には、バリア性の高い材料を用いるのが望ましい。例えば、バリア性の高い絶縁膜として、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などを用いることができる。

【0131】

また絶縁膜723として複数の積層された絶縁膜を用いる場合は、窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を、上記バリア性の高い絶縁膜よりも、酸化物半導体膜715及び酸化物半導体膜775に近い側に形成する。そして、窒素の含有比率が低い絶縁膜を間に挟んで、電極716乃至電極720、電極779、及び電極780、並びに酸化物半導体膜715及び酸化物半導体膜775と重なるように、バリア性の高い絶縁膜を形成する。バリア性の高い絶縁膜を用いることで、酸化物半導体膜715内、酸化物半導体膜775内、ゲート絶縁膜714内、酸化物半導体膜715と他の絶縁膜の界面とその近傍、或いは、酸化物半導体膜775と他の絶縁膜の界面とその近傍に、水分または水素などの不純物が入り込むのを防ぐことができる。また、酸化物半導体膜715及び酸化物半導体膜775に接するように窒素の比率が低い酸化窒化珪素膜などの絶縁膜を形成することで、バリア性の高い材料を用いた絶縁膜が、直接、酸化物半導体膜715及び酸化物半導体膜775に接するのを防ぐことができる。

【0132】

本実施の形態では、スパッタ法で形成された膜厚200nmの酸化珪素膜上に、スパッタ法で形成された膜厚100nmの窒化珪素膜を積層させた構造を有する、絶縁膜723を形成する。成膜時の基板温度は、室温以上300℃以下とすればよく、本実施の形態では100℃とする。

【0133】

なお、絶縁膜723を形成した後に、加熱処理を施しても良い。加熱処理は、窒素、超乾燥空気、または希ガス(アルゴン、ヘリウムなど)の雰囲気下において、好ましくは200℃以上400℃以下、例えば250℃以上350℃以下で行う。上記ガスは、水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下であることが望ましい。本実施の形態では、例えば、窒素雰囲気下で250℃、1時間の加熱処理を行う。或いは、電極716乃至電極720、電極779、及び電極780を形成する前に、水分または水素を低減させるための酸化物半導体膜に対して行った先の加熱処理と同様に、高温短時間のRTA処理を行っても良い。酸素を含む絶縁膜723が設けられた後に、加熱処理が施されることによって、酸化物半導体膜に対して行った先の加熱処理により、酸化物半導体膜715及び酸化物半導体膜775に酸素欠損が発生していたとしても、絶縁膜723から酸化物半導体膜715及び酸化物半導体膜775に酸素が供与される。そして、酸化物半導体膜715及び酸化物半導体膜775に酸素が供与されることで、酸化物半導体膜715及び酸化物半導体膜775において、ドナーとなる酸素欠損を低減し、化学量論比を満たす構成とすること、またそれ以上に酸素が含まれる構成とすることが可能である。酸化物半導体膜715及び酸化物半導体膜775には化学量論比を超える量の酸素が含まれていることが好ましい。その結果、酸化物半導体膜715及び酸化物半導体膜775をi型に近づけることができ、酸素欠損によるトランジスタの電気特性のばらつきを軽減し、電気特性の向上を実現することができる。この加熱処理を行うタイミングは、絶縁膜723の形成後であれば特に限定されず、他の工程、例えば樹脂膜形成時の加熱処理や、透明導電膜を低抵抗化させるための加熱処理と兼ねることで、工程数を増やすことなく、酸化物半導体膜715及び酸化物半導体膜775をi型に近づけることができる。

【0134】

また、酸素雰囲気下で酸化物半導体膜715及び酸化物半導体膜775に加熱処理を施すことで、酸化物半導体に酸素を添加し、酸化物半導体膜715中及び酸化物半導体膜775中それぞれにおいてドナーとなる酸素欠損を低減させても良い。加熱処理の温度は、例えば100℃以上350℃未満、好ましくは150℃以上250℃未満で行う。上記酸素雰囲気下の加熱処理に用いられる酸素ガスには、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち酸素中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0135】

或いは、イオン注入法またはイオンドーピング法などを用いて、酸化物半導体膜715及び酸化物半導体膜775に酸素を添加することで、ドナーとなる酸素欠損を低減させても良い。例えば、2.45GHzのマイクロ波でプラズマ化した酸素を酸化物半導体膜715及び酸化物半導体膜775に添加すれば良い。

【0136】

以上の工程により、酸化物半導体トランジスタ724及び酸化物半導体トランジスタ781が形成される。

【0137】

酸化物半導体トランジスタ724は、ゲート電極713と、ゲート電極713上のゲート絶縁膜714と、ゲート絶縁膜714上においてゲート電極713と重なっている酸化物半導体膜715と、酸化物半導体膜715上に形成された一対の電極719及び電極720と、酸化物半導体膜715上に形成された絶縁膜723とを有する。

【0138】

同様に、酸化物半導体トランジスタ781は、ゲート電極773と、ゲート電極773上のゲート絶縁膜714と、ゲート絶縁膜714上においてゲート電極773と重なっている酸化物半導体膜775と、酸化物半導体膜775上に形成された一対の電極779及び電極780と、酸化物半導体膜775上に形成された絶縁膜723とを有する。

【0139】

なお図6(A)に示す酸化物半導体トランジスタ724は、電極719と電極720の間において、酸化物半導体膜715の一部がエッチングされたチャネルエッチ構造である。同様に、図6(A)に示す酸化物半導体トランジスタ781は、電極779と電極780の間において、酸化物半導体膜775の一部がエッチングされたチャネルエッチ構造である。

【0140】

なお、酸化物半導体トランジスタ724及び酸化物半導体トランジスタ781はそれぞれ、シングルゲート構造のトランジスタを用いて説明したが、必要に応じて、電気的に接続された複数のゲート電極を有することで、チャネル形成領域を複数有する、マルチゲート構造のトランジスタも形成することができる。

【0141】

図6(A)に示すnチャネル型トランジスタ704及びpチャネル型トランジスタ705は、図2乃至図4に示すオペアンプ112を構成するトランジスタ、図6(A)に示す酸化物半導体トランジスタ724は、図1乃至図4に示すトランジスタ101、並びに、図6(A)に示す酸化物半導体トランジスタ781は、図1及び図2のトランジスタ124、図3のトランジスタ144、図4のトランジスタ154として用いることができる。

【0142】

これにより、オペアンプ112を構成するトランジスタ、並びに、酸化物半導体トランジスタであるトランジスタ101、及び電圧変換回路のトランジスタ(トランジスタ124、トランジスタ144、及びトランジスタ154)を、絶縁膜712を介して同一基板700上に積層することができる。これにより、DC−DCコンバータの占有面積の増大を抑制することができる。

【0143】

また、酸化物半導体トランジスタであるトランジスタ101、及び電圧変換回路のトランジスタ(トランジスタ124、トランジスタ144、及びトランジスタ154)を同じ作製工程で作製することができるので、作製工程及び作製コストを低減させることができる。

【0144】

図6(B)に図6(A)とは異なる構成を有する積層構造を示す。

【0145】

図6(B)には、nチャネル型トランジスタ704、pチャネル型トランジスタ705が示されている。さらに図6(B)には、nチャネル型トランジスタ704及びpチャネル型トランジスタ705上に、酸化物半導体膜を用いたチャネル保護構造の、ボトムゲート型の酸化物半導体トランジスタ725及び酸化物半導体トランジスタ751が形成されている。

【0146】

酸化物半導体トランジスタ725は、絶縁膜712上に形成されたゲート電極730と、ゲート電極730上のゲート絶縁膜731と、ゲート絶縁膜731上においてゲート電極730と重なっている島状の酸化物半導体膜732と、ゲート電極730と重なる位置において島状の酸化物半導体膜732上に形成されたチャネル保護膜733と、酸化物半導体膜732上に形成された電極734及び電極735と、電極734、電極735及びチャネル保護膜733上に形成された絶縁膜736を有する。

【0147】

酸化物半導体トランジスタ751は、絶縁膜712上に形成されたゲート電極750と、ゲート電極750上のゲート絶縁膜731と、ゲート絶縁膜731上においてゲート電極750と重なっている島状の酸化物半導体膜752と、ゲート電極750と重なる位置において島状の酸化物半導体膜752上に形成されたチャネル保護膜753と、酸化物半導体膜752上に形成された電極754及び電極755と、電極754、電極755及びチャネル保護膜753上に形成された絶縁膜736を有する。

【0148】

チャネル保護膜733及びチャネル保護膜753を設けることによって、酸化物半導体膜732及び酸化物半導体膜752それぞれのチャネル形成領域となる部分に対する、後の工程における、エッチング時のプラズマやエッチング剤による膜減りなどのダメージを防ぐことができる。従ってトランジスタの信頼性を向上させることができる。

【0149】

チャネル保護膜733及びチャネル保護膜753には、酸素を含む無機材料(酸化珪素、窒化酸化珪素、酸化窒化珪素、酸化アルミニウム、または酸化窒化アルミニウムなど)を用いることができる。チャネル保護膜733及びチャネル保護膜753は、プラズマCVD法や熱CVD法などの気相成長法やスパッタリング法を用いて形成することができる。チャネル保護膜733及びチャネル保護膜753は成膜後にエッチングにより形状を加工する。ここでは、スパッタ法により酸化珪素膜を形成し、フォトリソグラフィによるマスクを用いてエッチング加工することでチャネル保護膜733及びチャネル保護膜753を形成する。

【0150】

酸素を含む無機材料をチャネル保護膜733及びチャネル保護膜753に用いることで、水分または水素を低減させるための加熱処理により、酸化物半導体膜732及び酸化物半導体膜752中に酸素欠損が発生していたとしても、酸化物半導体膜732にチャネル保護膜733から酸素を供給し、並びに、酸化物半導体膜752にチャネル保護膜753から酸素を供給し、ドナーとなる酸素欠損を低減して化学量論比を満たす構成、またはそれ以上に酸素が含まれる構成とすることが可能である。酸化物半導体膜732及び酸化物半導体膜752には、化学量論比を超える量の酸素が含まれていることが好ましい。よって、チャネル形成領域を、i型に近づけることができる。チャネル形成領域をi型に近づけることにより、酸素欠損による酸化物半導体トランジスタ725及び酸化物半導体トランジスタ751の電気特性のばらつきを軽減し、電気特性の向上を実現することができる。

【0151】

図6(B)に示すnチャネル型トランジスタ704及びpチャネル型トランジスタ705は、図2乃至図4に示すオペアンプ112を構成するトランジスタ、図6(B)に示す酸化物半導体トランジスタ725は、図1乃至図4に示すトランジスタ101、並びに、図6(B)に示す酸化物半導体トランジスタ751は、図1及び図2のトランジスタ124、図3のトランジスタ144、図4のトランジスタ154として用いることができる。

【0152】

これにより、オペアンプ112を構成するトランジスタ、並びに、酸化物半導体トランジスタであるトランジスタ101、及び電圧変換回路のトランジスタ(トランジスタ124、トランジスタ144、及びトランジスタ154)を、絶縁膜712を介して同一基板700上に積層することができるので、DC−DCコンバータの占有面積の増大を抑制することができる。

【0153】

また、酸化物半導体トランジスタであるトランジスタ101、及び電圧変換回路のトランジスタ(トランジスタ124、トランジスタ144、及びトランジスタ154)を同じ作製工程で作製することができるので、作製工程及び作製コストを低減させることができる。

【0154】

図6(C)には、nチャネル型トランジスタ704及びpチャネル型トランジスタ705が示されている。さらに図6(C)では、nチャネル型トランジスタ704及びpチャネル型トランジスタ705上に、酸化物半導体膜を用いたボトムコンタクト型の酸化物半導体トランジスタ726及び酸化物半導体トランジスタ760が形成されている。

【0155】

酸化物半導体トランジスタ726は、絶縁膜712上に形成されたゲート電極741と、ゲート電極741上のゲート絶縁膜742と、ゲート絶縁膜742上の電極743及び電極744と、ゲート絶縁膜742を間に挟んでゲート電極741と重なっている酸化物半導体膜745と、酸化物半導体膜745上に形成された絶縁膜746を有する。

【0156】

酸化物半導体トランジスタ760は、絶縁膜712上に形成されたゲート電極761と、ゲート電極761上のゲート絶縁膜742と、ゲート絶縁膜742上の電極763及び電極764と、ゲート絶縁膜742を間に挟んでゲート電極761と重なっている酸化物半導体膜765と、酸化物半導体膜765上に形成された絶縁膜746を有する。

【0157】

図6(C)に示すnチャネル型トランジスタ704及びpチャネル型トランジスタ705は、図2乃至図4に示すオペアンプ112を構成するトランジスタ、図6(C)に示す酸化物半導体トランジスタ726は、図1乃至図4に示すトランジスタ101、並びに、図6(C)に示す酸化物半導体トランジスタ760は、図1及び図2のトランジスタ124、図3のトランジスタ144、図4のトランジスタ154として用いることができる。

【0158】

これにより、オペアンプ112を構成するトランジスタ、並びに、酸化物半導体トランジスタであるトランジスタ101、及び電圧変換回路のトランジスタ(トランジスタ124、トランジスタ144、及びトランジスタ154)を、絶縁膜712を介して同一基板700上に積層することができるので、DC−DCコンバータの占有面積の増大を抑制することができる。

【0159】

また、酸化物半導体トランジスタであるトランジスタ101、及び電圧変換回路のトランジスタ(トランジスタ124、トランジスタ144、及びトランジスタ154)を同じ作製工程で作製することができるので、作製工程及び作製コストを低減させることができる。

【符号の説明】

【0160】

101 トランジスタ

102 入力端子

110 内部電圧生成回路

111 制御回路

112 オペアンプ

113 抵抗

114 抵抗

115 端子

121 電圧変換回路

122 コイル

123 ダイオード

124 トランジスタ

125 コンデンサ

130 内部制御回路

131 出力端子

141 電圧変換回路

142 コイル

143 ダイオード

144 トランジスタ

145 コンデンサ

146 コイル

149 トランス

151 電圧変換回路

152 コイル

153 ダイオード

154 トランジスタ

155 コンデンサ

156 コイル

157 ダイオード

158 コイル

159 トランス

700 基板

701 絶縁膜

702 半導体膜

703 半導体膜

704 nチャネル型トランジスタ

705 pチャネル型トランジスタ

706 ゲート電極

707 ゲート電極

708 絶縁膜

711 配線

712 絶縁膜

713 ゲート電極

714 ゲート絶縁膜

715 酸化物半導体膜

716 電極

717 電極

718 電極

719 電極

720 電極

723 絶縁膜

724 酸化物半導体トランジスタ

725 酸化物半導体トランジスタ

726 酸化物半導体トランジスタ

730 ゲート電極

731 ゲート絶縁膜

732 酸化物半導体膜

733 チャネル保護膜

734 電極

735 電極

736 絶縁膜

741 ゲート電極

742 ゲート絶縁膜

743 電極

744 電極

745 酸化物半導体膜

746 絶縁膜

750 ゲート電極

751 酸化物半導体トランジスタ

752 酸化物半導体膜

753 チャネル保護膜

754 電極

755 電極

760 酸化物半導体トランジスタ

761 ゲート電極

763 電極

764 電極

765 酸化物半導体膜

773 ゲート電極

775 酸化物半導体膜

779 電極

780 電極

781 酸化物半導体トランジスタ

【特許請求の範囲】

【請求項1】

入力電圧が印加される入力端子と、

前記入力端子と接続され、第1のトランジスタを有する電圧変換回路と、

前記電圧変換回路を制御し、珪素材料をチャネル形成領域に有する第2のトランジスタを有する制御回路と、

前記入力端子と前記制御回路との間に設けられ、前記入力電圧を前記入力電圧より低い電圧である電源電圧に変換する第3のトランジスタと、

を有し、

前記第1のトランジスタ及び前記第3のトランジスタは、酸化物半導体材料をチャネル形成領域に有するトランジスタであり、

前記第2のトランジスタ、並びに、前記第1のトランジスタ及び前記第3のトランジスタは、絶縁膜を介して積層されていることを特徴とするDC−DCコンバータ。

【請求項2】

請求項1において、

前記酸化物半導体材料は、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系酸化物半導体、二元系金属の酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体、一元系金属の酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体のいずれかであることを特徴とするDC−DCコンバータ。

【請求項3】

請求項1又は請求項2において、

前記電圧変換回路は、降圧型の電圧変換回路であることを特徴とするDC−DCコンバータ。

【請求項4】

請求項1又は請求項2において、

前記電圧変換回路は、フライバック型の電圧変換回路であることを特徴とするDC−DCコンバータ。

【請求項5】

請求項1又は請求項2において、

前記電圧変換回路は、フォワード型の電圧変換回路であることを特徴とするDC−DCコンバータ。

【請求項6】

絶縁表面上に、珪素材料を第1のチャネル形成領域に用いた第1のトランジスタを形成し、

前記第1のトランジスタを覆って、絶縁膜を形成し、

前記絶縁膜上に、酸化物半導体材料を第2のチャネル形成領域として用いた第2のトランジスタ、及び前記酸化物半導体材料を第3のチャネル形成領域として用いた第3のトランジスタを形成し、

前記第2のトランジスタは電圧変換回路を構成し、

前記第1のトランジスタは、前記電圧変換回路を制御する制御回路を構成し、

前記第3のトランジスタは、入力端子と前記制御回路との間に設けられ、前記入力端子に印加される入力電圧を前記入力電圧より低い電圧である電源電圧に変換することを特徴とするDC−DCコンバータの作製方法。

【請求項7】

請求項6において、

前記酸化物半導体材料は、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系酸化物半導体、二元系金属の酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体、一元系金属の酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体のいずれかであることを特徴とするDC−DCコンバータの作製方法。

【請求項8】

請求項6又は請求項7において、

前記電圧変換回路は、降圧型の電圧変換回路であることを特徴とするDC−DCコンバータの作製方法。

【請求項9】

請求項6又は請求項7において、

前記電圧変換回路は、フライバック型の電圧変換回路であることを特徴とするDC−DCコンバータの作製方法。

【請求項10】

請求項6又は請求項7において、

前記電圧変換回路は、フォワード型の電圧変換回路であることを特徴とするDC−DCコンバータの作製方法。

【請求項1】

入力電圧が印加される入力端子と、

前記入力端子と接続され、第1のトランジスタを有する電圧変換回路と、

前記電圧変換回路を制御し、珪素材料をチャネル形成領域に有する第2のトランジスタを有する制御回路と、

前記入力端子と前記制御回路との間に設けられ、前記入力電圧を前記入力電圧より低い電圧である電源電圧に変換する第3のトランジスタと、

を有し、

前記第1のトランジスタ及び前記第3のトランジスタは、酸化物半導体材料をチャネル形成領域に有するトランジスタであり、

前記第2のトランジスタ、並びに、前記第1のトランジスタ及び前記第3のトランジスタは、絶縁膜を介して積層されていることを特徴とするDC−DCコンバータ。

【請求項2】

請求項1において、

前記酸化物半導体材料は、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系酸化物半導体、二元系金属の酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体、一元系金属の酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体のいずれかであることを特徴とするDC−DCコンバータ。

【請求項3】

請求項1又は請求項2において、

前記電圧変換回路は、降圧型の電圧変換回路であることを特徴とするDC−DCコンバータ。

【請求項4】

請求項1又は請求項2において、

前記電圧変換回路は、フライバック型の電圧変換回路であることを特徴とするDC−DCコンバータ。

【請求項5】

請求項1又は請求項2において、

前記電圧変換回路は、フォワード型の電圧変換回路であることを特徴とするDC−DCコンバータ。

【請求項6】

絶縁表面上に、珪素材料を第1のチャネル形成領域に用いた第1のトランジスタを形成し、

前記第1のトランジスタを覆って、絶縁膜を形成し、

前記絶縁膜上に、酸化物半導体材料を第2のチャネル形成領域として用いた第2のトランジスタ、及び前記酸化物半導体材料を第3のチャネル形成領域として用いた第3のトランジスタを形成し、

前記第2のトランジスタは電圧変換回路を構成し、

前記第1のトランジスタは、前記電圧変換回路を制御する制御回路を構成し、

前記第3のトランジスタは、入力端子と前記制御回路との間に設けられ、前記入力端子に印加される入力電圧を前記入力電圧より低い電圧である電源電圧に変換することを特徴とするDC−DCコンバータの作製方法。

【請求項7】

請求項6において、

前記酸化物半導体材料は、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系酸化物半導体、二元系金属の酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体、一元系金属の酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体のいずれかであることを特徴とするDC−DCコンバータの作製方法。

【請求項8】

請求項6又は請求項7において、

前記電圧変換回路は、降圧型の電圧変換回路であることを特徴とするDC−DCコンバータの作製方法。

【請求項9】

請求項6又は請求項7において、

前記電圧変換回路は、フライバック型の電圧変換回路であることを特徴とするDC−DCコンバータの作製方法。

【請求項10】

請求項6又は請求項7において、

前記電圧変換回路は、フォワード型の電圧変換回路であることを特徴とするDC−DCコンバータの作製方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−135191(P2012−135191A)

【公開日】平成24年7月12日(2012.7.12)

【国際特許分類】

【出願番号】特願2011−258830(P2011−258830)

【出願日】平成23年11月28日(2011.11.28)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成24年7月12日(2012.7.12)

【国際特許分類】

【出願日】平成23年11月28日(2011.11.28)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]