Fターム[5F038BG06]の内容

Fターム[5F038BG06]に分類される特許

1 - 20 / 317

半導体装置

半導体集積回路

省面積及び省電力のスタンダードセル方法

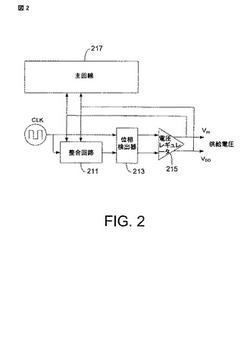

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

(もっと読む)

高速ウェイクアップのための電力スイッチ加速機構

【課題】ウェイクアップ中の電力スイッチ加速方法及び装置を提供する。

【解決手段】一実施形態において、集積回路は、少なくとも1つの電力ゲート回路ブロックを含む。電力ゲート回路ブロックは、該ブロックがアクティブであるときにその回路へ電圧を送るバーチャル電圧ノードを含む。バーチャル電圧ノードと、それに対応するグローバル電圧ノードとの間に電力スイッチが結合される。電力ゲート回路ブロックがパワーオンであるときに、電力スイッチが順次にアクチベートされる。電力スイッチがアクチベートされる割合は、バーチャル電圧ノードの電圧が増加するにつれて高くなる。電力スイッチを順次にアクチベートすることで、過剰な電流が電力ゲート回路ブロックに流入するのを防止する。バーチャル電圧ノードの電圧が少なくともあるレベルにあるときに電力スイッチがアクチベートされる割合を高めることで、より高速のウェイクアップを許すことができる。

(もっと読む)

高速スイッチング動作回路

【課題】より高電圧をより高速にスイッチングできる高速スイッチング動作回路を提供する。

【解決手段】DC/DCコンバータ1は、活性領域がSiC半導体からなるMISFETで構成されたスイッチング素子10を有する。駆動回路11は、スイッチング素子10を1MHz以上の駆動周波数で駆動する。スイッチング素子10のスイッチング時の電圧変化速度は5×109V/秒以上である。前記MISFETは、活性領域に形成されたトレンチと、トレンチの底面および壁面を絶縁膜と、絶縁膜を介して活性領域に対向するゲート電極とを含むトレンチゲート構造を有していてもよい。

(もっと読む)

半導体装置及びアナログスイッチの制御方法

【課題】高い電圧を有する入力信号に対して適切に動作するアナログスイッチを有する半導体装置を提供する。

【解決手段】入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,入力端子に印加される入力電圧に応じて,Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,アナログスイッチを導通または非導通に制御する制御信号を可変電圧回路に供給する制御回路とを有する。可変電圧回路は,導通に制御する制御信号に応答して,可変生成される第1ゲート電圧と第2ゲート電圧とをPチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する。

(もっと読む)

半導体集積回路、電子機器及びマルチチップ半導体パッケージ

【課題】比較的簡単な構成でありながらも動的で高分解能の電圧制御可能な半導体集積回路、電子機器及びマルチチップ半導体パッケージを提供すること。

【解決手段】電子機器100は、電源IC110と、電源IC110から出力される電源電圧Vsrcで動作するSoC#0〜2とを備える。SoC#0〜2は、三次元実装されたマルチチップ半導体パッケージに搭載される。SoC#0〜2は、第3の端子123から入力されるアナログ制御信号の電位と、内部配線124の電位とに基づいて、第2の端子122から出力するアナログ制御信号を生成する電位制御回路125と、電源フィードバック(FB)電圧入力端子である第2の端子122及び第3の端子123と、を備える。SoC#0〜2は、FB出力端子FB_out/FB入力端子FB_inをカスケード接続し、最終段のSoC#0のFB出力を電源IC110に接続している。

(もっと読む)

半導体装置及びこれを備える情報処理装置

【課題】安定したチャージポンプ動作を行う。

【解決手段】ノードA,Bを有するコンデンサC1と、VDDレベルからVSSレベルの間で振幅するポンピング信号PUMP1をコンデンサC1のノードAに供給するポンピング回路110と、コンデンサC1のノードBをVPPextレベルにプリチャージし、ポンピング信号PUMP1がVSSレベルからVDDレベルに変わった時に、コンデンサC1のノードBをVPPextレベルよりも高いレベルに駆動する出力回路120とを備える。本発明によれば、コンデンサC1のノードAをポンピングするための電圧と、コンデンサC1のノードBをプリチャージするための電圧が異なっていることから、昇圧電圧を効率よく生成することできる。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】第1のクロック分配回路は、タイミング信号を複数の第1の分配点に分配する。第2のクロック分配回路は、タイミング信号を複数の第2の分配点に分配する。最小遅延クロック信号出力部は、複数の第1の分配点のいずれかに分配されたタイミング信号と複数の第2の分配点のいずれかに分配されたタイミング信号とのうち遅延が小さい方の信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。

(もっと読む)

昇圧回路

【課題】損失を抑制すると共により迅速に昇圧を行なう。

【解決手段】チャージポンプ20からの出力電圧VCがトリガ電圧を超えると、スイッチ70がオンし、クロック信号供給回路30は出力電圧VCの振幅のクロック信号CKmos,CKBmosをチャージポンプ20に出力し、クロック信号供給回路40は出力電圧VCの振幅のクロック信号CKmosを用いてクロック信号CKcap,CKBcapを生成してチャージポンプ20に出力し、チャージポンプ20では、各トランジスタのゲートへ出力電圧VCの振幅のクロック信号CKmos,CKBmosが供給され、各キャパシタの他端へ立ち上がり時間の小さいクロック信号CKcap,CKBcapが供給される。これにより、昇圧回路10全体の損失を抑制すると共により迅速に出力電圧VCを目標出力電圧に昇圧することができる。

(もっと読む)

チャージポンプ回路およびその制御回路、オーディオ信号処理回路、電子機器

【課題】昇圧率の切りかえの際に、電流の逆流を防止する。

【解決手段】コントローラ10は、第1スイッチSW1から第7スイッチSW7のオン、オフ状態を制御することにより、(1)第1モードにおいて、第3端子P3に入力電圧VDDを、第4端子P4に入力電圧VDDを反転した負電圧−VDDを発生させ、(2)第2モードにおいて、第3端子P3に入力電圧VDDの略1/2倍の電圧を、第4端子P4に、入力電圧VDDの略1/2倍の電圧を反転した負電圧−VDD/2を発生させる。コントローラ10は、第1モードから第2モードへの移行を指示されると、遷移期間にわたり、第3スイッチおよび第5スイッチをオンする第1状態と、第2スイッチおよび第4スイッチをオンする第2状態と、を交互に繰り返す第3モードで動作し、その後、第2モードで動作する。

(もっと読む)

ラッチ回路、トリミング回路、システム、判定プログラム、確認方法、及び判定方法

【課題】入力信号の状態が適正であるかを確認することができる、ラッチ回路、トリミング回路、システム、判定プログラム、確認方法、及び判定方法を提供する。

【解決手段】トリミング回路14の読出回路20から出力されるトリミング素子であるヒューズ素子H1の状態に応じた入力信号I1が入力されるラッチ回路22を、ラッチ回路L1と、ラッチ回路L2と、一致確認回路26と、で構成している。ラッチ回路L1は、入力信号I1の論理値をタイミングT1で保持して、保持した論理値に応じた出力信号O1をトリミング回路14の外部に出力する。ラッチ回路L2は、タイミングT1よりも遅いタイミングT2で保持して、保持した論理値に応じた出力信号O2を出力する。一致確認回路26は、排他的論理和回路30により構成されており、出力信号O1と出力信号O2とが一致しているか否かを示す一致判定信号X1を外部の判定回路18に出力する。

(もっと読む)

半導体装置

【課題】低電圧で動作するとともに高電圧が入力された場合でも破壊することがないチャージポンプ回路を備えているとともに、通常の量産用の半導体製造プロセスが適用可能な半導体装置を提供する。

【解決手段】半導体装置において、チャージポンプ回路30は、薄膜トランジスタで構成され、外部電源電圧を昇圧する。スイッチ制御部11は、外部電源電圧が基準電圧を超えている場合には、チャージポンプ回路30への外部電源電圧の供給が遮断されるようにするとともに外部電源電圧がチャージポンプ回路30を介さずに負荷回路50に直接供給されるようにする。基板電圧制御部14は、外部電源電圧が基準電圧以下の場合に、チャージポンプ回路30を構成するトランジスタの基板領域に順方向となるバイアス電圧を供給する。

(もっと読む)

昇圧回路

【課題】負荷電流に応じて昇圧能力を調整することにより、過剰な昇圧回路出力リップルを抑制する。

【解決手段】昇圧回路1は、昇圧部出力CPOの電圧を変動させて昇圧回路出力VPPを生成し、昇圧回路出力VPPの負荷電流の大きさに応じて制御電圧CON1を生成する制御部2と、制御電圧CON1に応じて電源VDDP1の電圧を変動させることにより昇圧部電源VDDPを生成する電源降圧部3と、昇圧回路出力VPPの電圧と目標電圧との差分に応じて昇圧部電源VDDPの電圧を変動させることにより昇圧部出力CPOを生成する昇圧部4とを備える。

(もっと読む)

半導体装置

【課題】出力端子に接続される内部回路の動作開始を早く行うことができる定電圧発生回路を備えた半導体装置を提供する。

【解決手段】クロック信号VOSCが入力されると、内部の複数のノードにおいてポンピング動作を行い、入力端子に供給される電荷を複数のノードを介して出力端子へと順次転送し、出力端子から出力電圧を発生する昇圧回路20と、出力電圧が予め設定された電圧に達した場合、非活性レベルの検知信号VUPTを出力する電圧検出回路30と、検知信号が活性レベルの場合、クロック信号を昇圧回路へ出力し、検知信号が非活性レベルの場合、クロック信号の昇圧回路への出力を停止するクロック信号制御回路40と、を備え、クロック信号制御回路は、検知信号が非活性レベルであっても、入力される制御信号RESETTのレベルに応じてクロック信号を昇圧回路へ出力する。

(もっと読む)

正負電圧論理出力回路およびこれを用いた高周波スイッチ回路

【課題】負電圧の変化に対して正常な論理回路動作を確保できる範囲である動作ウィンドウの幅の拡張を可能とし、回路動作の確実性、安定性の向上を図った正負電圧論理出力回路を提供する。

【解決手段】論理入力と負電圧との間に、ゲートに論理入力するエンハンスメント型P型電界効果トランジスタEPFET1とブレークダウン保護用素子13,14とが直列に接続され、ブレークダウン保護用素子14に並列に短絡する切替スイッチ8aが接続される。切替スイッチ8aをオン、オフ制御することで、VSSの変動に対して正常な回路動作を確保できる動作ウィンドウの拡張を可能とする。

(もっと読む)

半導体装置

【課題】トリミング回路を備えた半導体装置において、内部電源の電圧レベルを半導体装置の外部から適切に制御できるようにすること。

【解決手段】半導体装置は、複数のレベルの間で遷移する第1のテストモード信号を受信し、第1のテストモード信号の遷移に応じてカウント動作を行うバイナリカウンタ回路と、バイナリカウンタ回路の所定のビットの値を示すビット信号、および、バイナリカウンタ回路のカウント動作を制御する第2のテストモード信号を受信し、ビット信号および第2のテストモード信号に応じて、第1のテストモード信号を遷移させるか否かを制御する制御回路と、バイナリカウンタ回路のカウント値に応じて、複数の基準電位の中からいずれかの基準電位を選択するセレクタと、セレクタにより選択された基準電位に応じて、内部電源を発生する内部電源発生回路と、を備える。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

スタンダードセル回路、半導体集積回路、及び半導体集積回路装置

【課題】スタンダードセル回路のレイアウト面積を削減する。

【解決手段】配線導体Laは電源電圧VDDaを出力する電源に接続される。レギュレータ6aは、配線導体Laからの電源電圧VDDaを電源電圧VDDaより低い電源電圧VDDbに変換し、配線導体Lbを介してレベルシフタ2−1〜2−3,3,及びスタンダードセル4に出力する。レベルシフタ2−1は、入力されるデータの電圧レベルを電源電圧VDDaの電圧レベルから電源電圧VDDbの電圧レベルに電圧シフトしてスタンダードセル4に出力する。レベルシフタ3は、スタンダードセル4からの出力信号の電圧レベルを電源電圧VDDbの電圧レベルから電源電圧VDDaの電圧レベルに電圧シフトし、出力端子Tqを介して出力する。

(もっと読む)

半導体集積回路

【課題】出力トランジスタで発生するラッシュ電流を抑制する。

【解決手段】一つの実施形態によれば、半導体集積回路は、第一及び第二の出力トランジスタ、第一の遅延発生部が設けられる。第一及び第二の出力トランジスタは並列的に配置される。第一の出力トランジスタは、制御端子に第一の制御信号が入力され、第一の制御信号に基づいてオンして低電位側電源側に第一の電流を流し、第一の電流が流れ始めてから一定な電流になるまでに第一の時間を要する。第一の遅延発生部は、第一の制御信号が入力され、第一の制御信号を第一の時間よりも短い第二の時間だけ遅延させた第二の制御信号を出力する。第二の出力トランジスタは、制御端子に第二の制御信号が入力され、第二の制御信号に基づいてオンして低電位側電源側に第二の電流を流す。

(もっと読む)

1 - 20 / 317

[ Back to top ]