Fターム[5F038BH15]の内容

Fターム[5F038BH15]に分類される特許

1 - 20 / 490

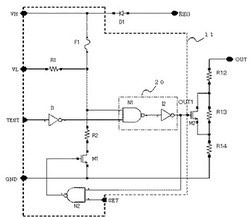

トリミング回路及び調整回路

【課題】ヒューズ素子の仮想切断を可能にすると共に、高電圧又は大電流によるヒューズ溶断の際に、周辺回路を破損する確率も低減できる信頼性の高いトリミング回路を提供する。

【解決手段】ヒューズトリミングを行うための回路であって、トリミングヒューズと、

前記トリミングヒューズに接続されるトリミング用のパッド端子と、仮想切断時に制御信号を入力するテスト端子と、入力端子の一方が前記テスト端子に接続され他方が前記トリミングヒューズに接続され、入力された制御信号に応じた制御信号を出力する制御回路と、を有し、前記トリミングヒューズの切断により、前記制御回路の他方の入力端子がGNDレベルへプルダウンする手段を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

半導体装置

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

半導体装置及びアナログスイッチの制御方法

【課題】高い電圧を有する入力信号に対して適切に動作するアナログスイッチを有する半導体装置を提供する。

【解決手段】入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,入力端子に印加される入力電圧に応じて,Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,アナログスイッチを導通または非導通に制御する制御信号を可変電圧回路に供給する制御回路とを有する。可変電圧回路は,導通に制御する制御信号に応答して,可変生成される第1ゲート電圧と第2ゲート電圧とをPチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置

【課題】低消費電力化及び回路面積の削減を図れるようにした半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、電源端子と接地端子の間に接続されたMOSトランジスタと、MOSトランジスタのドレインとゲートの間に接続された第1のダイオードと、MOSトランジスタのドレインとゲートの間に第1のダイオードと互いの順方向が逆向きに直列に接続された第2のダイオードと、MOSトランジスタのドレインとゲートの間に第1及び第2のダイオードと直列に接続されたキャパシタとを備えている。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の制御された酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体装置

【課題】保護素子の異なるクランプ電圧を容易に設定して形成できる構造の保護素子を含む半導体装置を提供すること。

【解決手段】回路内部のMOS型半導体装置のゲート酸化膜を保護するための保護素子を含む半導体装置であって、該保護素子は、該MOS型半導体装置とその前段回路との間に接続される横型バイポーラトランジスタであり、該横型バイポーラトランジスタのパンチスルー耐圧をクランプ電圧として利用することを特徴とする、半導体装置。

(もっと読む)

半導体装置

【課題】 本実施形態は、面積効率に優れた半導体装置を実現することを目的としている。

【解決手段】 本実施形態の半導体装置は、半導体基板と、半導体基板上に形成された電界効果トランジスタと、前記電界効果トランジスタの形成領域に隣接するダイオード形成領域とを備え、前記ダイオード形成領域は前記トランジスタの形成領域と前記半導体基板上で絶縁され、前記ダイオード形成領域内は櫛状に並んだアノード電極とカソード電極から形成され、前記アノード電極とカソード電極は、電界効果トランジスタを構成する櫛状にならんだゲート電極、ソース電極およびドレイン電極とは電極方向とは異なる方向となるように形成されることを特徴とする。

(もっと読む)

半導体装置

【課題】低電圧で動作するとともに高電圧が入力された場合でも破壊することがないチャージポンプ回路を備えているとともに、通常の量産用の半導体製造プロセスが適用可能な半導体装置を提供する。

【解決手段】半導体装置において、チャージポンプ回路30は、薄膜トランジスタで構成され、外部電源電圧を昇圧する。スイッチ制御部11は、外部電源電圧が基準電圧を超えている場合には、チャージポンプ回路30への外部電源電圧の供給が遮断されるようにするとともに外部電源電圧がチャージポンプ回路30を介さずに負荷回路50に直接供給されるようにする。基板電圧制御部14は、外部電源電圧が基準電圧以下の場合に、チャージポンプ回路30を構成するトランジスタの基板領域に順方向となるバイアス電圧を供給する。

(もっと読む)

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

半導体装置

【課題】パワー半導体素子において、周辺の電界強度を緩和する構造を小さな面積で実現する。

【解決手段】周辺領域Qにおいては、半導体層との間に周辺層間絶縁層(絶縁層)を介して複数の多結晶シリコン層70が、ソース電極30から端部ドレイン電極41の間にかけて設けられる。多結晶シリコン層70には、その長手方向が水平方向から傾斜した(傾斜角θ、0<θ<90°)傾斜部が設けられている。多結晶シリコン層70の傾斜部においては、p型領域71と、n型領域72とが長手方向に交互に多数形成されている。

(もっと読む)

正負電圧論理出力回路およびこれを用いた高周波スイッチ回路

【課題】負電圧の変化に対して正常な論理回路動作を確保できる範囲である動作ウィンドウの幅の拡張を可能とし、回路動作の確実性、安定性の向上を図った正負電圧論理出力回路を提供する。

【解決手段】論理入力と負電圧との間に、ゲートに論理入力するエンハンスメント型P型電界効果トランジスタEPFET1とブレークダウン保護用素子13,14とが直列に接続され、ブレークダウン保護用素子14に並列に短絡する切替スイッチ8aが接続される。切替スイッチ8aをオン、オフ制御することで、VSSの変動に対して正常な回路動作を確保できる動作ウィンドウの拡張を可能とする。

(もっと読む)

ネスト化複合スイッチ

【課題】高いスイッチング速度及び低いオン状態抵抗を有し、電圧降伏耐性を強化したネスト化複合スイッチを提供する。

【解決手段】ネスト化複合スイッチ240は、複合スイッチに結合されたノーマリオン・プライマリ・トランジスタを含む。複合スイッチは、中間型トランジスタ222とカスコード接続された低電圧(LV)トランジスタ224を含み、中間型トランジスタは、LVトランジスタよりは大きく、ノーマリオン・プライマリ・トランジスタよりは小さい降伏電圧を有する。1つの実現では、ノーマリオン・プライマリ・トランジスタはIII-V族トランジスタとすることができ、LVトランジスタはIV族LVトランジスタとすることができる。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

スイッチング素子の制御装置

【課題】実際に発生しているフライバックエネルギーを定量的に評価した上で保護動作を行うことができるスイッチング素子の制御装置を提供する。

【解決手段】NチャネルMOSFET2を介してコイル1に供給される電流をセンスMOSFET6及び検出用抵抗素子21により検出し、NチャネルMOSFET2をターンオフさせた際に発生し、ドレインに印加される逆起電圧をクランプ回路3によってクランプする。電流検出回路24は、クランプ回路3に発生するクランプ電圧によりNチャネルMOSFETがターンオンした際に、検出用抵抗素子21に流れる電流を複数の閾値と比較し、保護動作部26は、電流検出回路24の比較結果により、前記電流がNチャネルMOSFET2をターンオフさせた時点からの時間経過に対応する特定の閾値を超えていると判定されると、逆起電圧に基づくエネルギーを減少させるようにNチャネルMOSFET2の制御状態を変更する。

(もっと読む)

保護ダイオード及びこれを備えた半導体装置

【課題】PN接合容量が小さい保護ダイオード及びこれを備えた半導体装置を提供する。

【解決手段】

第1領域と当該第1領域を囲う第2領域と当該第2領域を囲う第3領域とを備える半導体基板と、当該第2領域と当該第3領域との間に設けられた第1絶縁層と、当該第3領域に設けられた第1導電型半導体と、当該第2領域に設けられた第2導電型半導体と、当該第1領域に設けられた容量緩和層と、を備えている保護ダイオード。当該保護ダイオードと、これに接続された第1のパッドと、当該容量緩和層を有しない構造の保護ダイオードと、これに接続された第2のパッドと、を備えている半導体装置。

(もっと読む)

スイッチング素子の保護回路

【課題】窒化物FETを高速スイッチング動作させることができ、且つ、サージ電圧から窒化物FETを保護することができるスイッチング素子の保護回路。

【解決手段】直列に接続された高圧側素子M1及び低圧側素子M2と、高圧側素子をオンオフさせる信号を出力するハイサイドプリドライバ11と、高圧側素子と逆のオンオフ状態になるように低圧素子をオンオフさせる信号を出力するローサイドプリドライバ12と、高圧側素子と低圧側素子の接続点に制御端子が接続されたスイッチング素子Tr1と、スイッチング素子の一方の端子にカソードが接続されたダイオードD1と、ダイオードのアノードに入力端子が接続され、ダイオードのブレーク時にスイッチング素子の制御端子に電流を供給するとともに、低圧側素子のオフを指示する信号をローサイドプリドライバに供給する制御器21とを備える。

(もっと読む)

1 - 20 / 490

[ Back to top ]