Fターム[5F038EZ11]の内容

Fターム[5F038EZ11]の下位に属するFターム

Fターム[5F038EZ11]に分類される特許

1 - 20 / 334

可変インダクタ

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

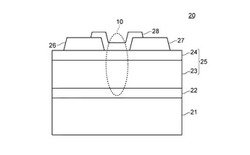

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

型押し構造体の製造方法、薄膜トランジスター、薄膜キャパシター、アクチュエーター、圧電式インクジェットヘッド及び光学デバイス

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより金属酸化物又は金属となる液体材料を準備する第1工程と、基材上に液体材料を塗布することにより金属酸化物又は金属の前駆体組成物からなる前駆体組成物層を形成する第2工程と、前駆体組成物層に対して凹凸型を用いて型押し加工を施すことにより前駆体組成物層に残膜を含む型押し構造を形成する第3工程と、型押し構造が形成された前駆体組成物層に対して大気圧プラズマ又は減圧プラズマによるアッシング処理を施すことにより残膜を処理する第4工程と、前駆体組成物層を熱処理することにより、前駆体組成物層から金属酸化物又は金属からなる型押し構造体を形成する第5工程とをこの順序で含む型押し構造体の製造方法。

(もっと読む)

機能性デバイスの製造方法及び機能性デバイスの製造装置

【課題】機能性デバイスの高性能化、又はそのような機能性デバイスの製造プロセスの簡素化と省エネルギー化を提供する。

【解決手段】機能性デバイスの製造方法は、型押し工程と、機能性固体材料層形成工程を含む。型押し工程では、機能性固体材料前駆体溶液を出発材とする機能性固体材料前駆体層に対して型押し構造を形成する型を押圧している間の少なくとも一部の時間においてその機能性固体材料前駆体層に対して熱を供給する熱源の第1温度がその機能性固体材料前駆体層の第2温度よりも高くなるように、その機能性固体材料前駆体層に対して型押し加工を施す。また、機能性固体材料層形成工程では、型押し工程の後、酸素含有雰囲気中において、機能性固体材料前駆体層を前述の第1温度よりも高い第3温度で熱処理することにより、機能性固体材料前駆体層から機能性固体材料層を形成する。

(もっと読む)

集積型半導体装置

【課題】 従来に比べて小型で、素子機能部間で、高い周波数の信号を高精度に伝送することができる集積型半導体装置を提供する。

【解決手段】

サファイア単結晶基板10の一方主面10A上に配置された第1素子機能部26と、一方主面上10Aに配置された第1アンテナ部23と、他方主面10Bに配置された第2素子機能部36と、他方主面10B上に配置された第2アンテナ部33とを備え、第1素子機能部26が第1アンテナ部23に送信用電気信号を送り、第1アンテナ部23が送信用電気信号に応じた電波を発信し、第2アンテナ部33がサファイア単結晶基板10を透過した電波を受信することで、高い周波数の信号を基板の上下面で高精度に処理することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線中に、抵抗率が高く、かつ抵抗温度係数が小さい抵抗素子を備える半導体装置を提供する。

【解決手段】第1絶縁層(層間絶縁層340)と、第1絶縁層(層間絶縁層340)上に設けられ、少なくとも表層がTaSiN層440である抵抗素子400と、第1絶縁層(層間絶縁層340)および抵抗素子400上に設けられた層間絶縁層360と、層間絶縁層360に設けられ、一端がTaSiN層440と接続する複数のビア500と、を備えている。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

保護回路、及び半導体装置

【課題】ESDの影響を効果的に抑制する保護回路を提供すること。またESDの影響が効果的に抑制された半導体装置を提供すること。

【解決手段】保護回路は、少なくとも2つの保護ダイオードを有し、当該保護ダイオードを、チャネルを形成する半導体層を挟んで対向する2つのゲートを有するトランジスタで構成する。さらに当該トランジスタのゲートの一方に、固定電位が入力される構成とすればよい。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

半導体ウェハ及びその製造方法

【課題】スクライブ線領域におけるダミーパターンが影響して配線形成の際に露光時のアライメント波形検出精度を低下させるおそれがあった。

【解決手段】複数の素子形成領域と、素子形成領域を相互に区画するスクライブ線領域と、素子形成領域において半導体基板上に配置された複数のパターンと、スクライブ線領域において半導体基板上に配置されるとともに、パターンと同様な構成の複数のダミーパターンと、パターン及びダミーパターンを含む半導体基板上に形成されるとともに、上面が平坦化された層間絶縁膜と、スクライブ線領域における層間絶縁膜に形成されるとともに、ダミーパターンと重ならない領域にて半導体基板に通じないように形成された穴状のアクセサリパターンと、を備える。

(もっと読む)

誘電体膜及びその製造方法、並びにキャパシタ

【課題】結晶粒のサイズを制御し、誘電体膜を貫通する結晶粒界やクラックの発生を抑制することによって、リーク電流の少ない高性能のキャパシタを提供する。

【解決手段】電極3,5の間に誘電体膜4が挟持されてなるキャパシタであって、誘電体膜4は、アルカリ土類金属と遷移金属との酸化物に、アルカリ土類金属の炭酸塩を0.1〜10mol%の範囲で含む。

(もっと読む)

半導体装置および半導体装置設計方法

【課題】半導体基板においてダミーパターンの配置密度を高める。

【解決手段】半導体基板104には、配線パターン102とダミーパターン106がレイアウトされる。配線パターン102の周囲にはマージン領域がレイアウトされ、マージン領域の周囲にダミー領域がレイアウトされる。このダミー領域に、複数のダミーパターン106がレイアウトされる。ダミーパターン106は、ダミー領域の延伸方向に配列される。マージン領域とダミー領域は、配線パターン102を基準として交互にレイアウトされる。

(もっと読む)

容量素子及びその製造方法並びに半導体集積回路

【課題】高い周波数帯での導体損失の増加を抑え、幅広い周波数範囲で低損失な動作を実現することが可能な容量素子及びその製造方法並びに半導体集積回路を提供すること。

【解決手段】本発明の容量素子10は、第1電極11と、第1電極11上に設けられた誘電体層12と、誘電体層12上に設けられた第2電極13とから構成されている。容量素子10は、誘電体層12を第1電極11と第2電極13とにより挟むようにしたサンドイッチ構造になっており、第2電極13の外表面に凹凸が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

半導体装置

【課題】裏面FIB加工における場所特定を容易にする。

【解決手段】半導体装置は、第1方向および前記第1方向に直交する第2方向の平面内に広がる第1導電型の半導体基板60の表面上に形成された回路部65と、前記半導体基板内の表面側に形成され、前記回路部を構成し、素子として機能する、前記第1導電型と異なる第2導電型の複数のウェル61と、前記半導体基板内の表面側に形成され、前記回路部を構成せず、素子として機能しない、前記第2導電型の複数のダミーウェル62と、を具備する。

(もっと読む)

半導体装置

【課題】送信機の変調器のキャリアリークを従来よりも高精度に抑制する。

【解決手段】半導体装置10において、信号分配部37は、発振器26によって生成されて入力部IN1に入力された高周波信号を第1および第2の信号に分配し、第1および第2の出力部OA1,OB1からそれぞれ出力する。変調器30は、ベースバンド信号を第1の信号で変調して出力する。オフセット調整部90は、第2の信号と変調器30の出力から漏洩した第1の信号とを比較することによってベースバンド信号のオフセットを調整する。上記の信号分配部37は、入力部IN1と第1の出力部OA1との間に設けられた第1の容量素子Ccapと、第1の出力部OA1と第2の出力部OB1との間に設けられた第2の容量素子Cpとを含む。第1の容量素子Ccapの静電容量は、第2の容量素子Cpの静電容量よりも大きい。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化されても高精度を維持できるキャパシタを提供する。

【解決手段】キャパシタは、平面上に交互に配列した、直線状で第1の長さを有し第1の方向に延在する第1の電極パターンと、直線状で前記第1の長さより短い第2の長さを有し、前記第1の方向に延在する第2の電極パタ―ンと、前記第1の電極パターンに第1の電圧を、第1のビアプラグを介して供給する第1の配線パタ―ンと、前記第2の電極パターンに第2の電圧を、第2のビアプラグを介して供給する第2の配線パタ―ンと、を備え、前記第1および第2の電極パターンをそれぞれの前記第1の方向で比較した場合、前記第1の電極パターンの第1の端部が、前記第1の端部に対応する前記第2の電極パターンの第2の端部よりも突出しており、前記第1の電極パターンの前記第1の端部に対向する第3の端部が、前記第3の端部に対応する前記第2の電極パターンの第4の端部よりも突出している。

(もっと読む)

キャパシタ構造体およびその製造方法

【課題】シリコン基板に設けられた穴の内部に導電体と誘電体を配置することにより、キャパシタを構成してなるキャパシタ構造体において、穴をより深くしたり、穴の平面形状を複雑な形状とすることなく、導電体間の対向面積を増加させて容量値の増大が実現できるようにする。

【解決手段】穴20は、シリコン基板10の一方の主面に開口する有底穴であり、穴20の内部にはシリコン基板10よりなる突起21が設けられ、穴20の底面は、突起21による凹凸面とされており、穴20の内部では、穴20の底面および側面に、これらの面側から第1の導電体31、誘電体40、第2の導電体32が順次積層されているとともに、第1の導電体31および誘電体40は、突起21による凹凸面の形状を承継した層形状とされている。

(もっと読む)

半導体装置、パターンレイアウト作成方法および露光マスク

【課題】 高集積化に有効な複数の配線パターンを含む配線パターン群を備えた半導体装置を提供すること。

【解決手段】 同一の配線用途のN(N≧3)本の配線パターンを含む配線パターン群を含む。N本の配線パターンの各々は別の層の配線郡内の配線パターンと電気的に接続するための接続領域を含む。N本の配線パターンは、配線パターンN1と、配線パターンN1の長手方向と異なる一方向に配置された二つ以上の配線パターンNi(i≧2)を含む。二つ以上の配線パターンNiはiの値が大きいほど配線パターンN1から離れた位置に配置され、二つ以上の配線パターンNiは少なくとも一つ以上のパターンNp(2≦p<N)と少なくとも一つ以上の配線パターンNq(p<q≦N)を含む。少なくとも一つ以上の配線パターンNpはpの値が大きいほど長手方向の寸法が長く、少なくとも一つ以上の配線パターンNqは、qの値が大きいほど、長手方向の寸法が短い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】プローブ跡を除去でき、かつ、製造コストが増加することを抑制できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】この半導体装置は、回路が形成された基板100と、この基板100上に形成され、表面に保護絶縁膜300が形成された多層配線層と、この多層配線層の最上層の配線層に位置し、上記回路に接続し、かつ、表面が保護絶縁膜と略同一面となっている電極パッド200と、を備える。また、このような半導体装置の製造方法は、回路が形成された基板100上に、この回路に接続し、かつ、保護絶縁膜300から突出した突出部201を有する電極パッド200を形成する工程と、プローブ端子500を電極パッド200に接触させることにより、回路の動作テストを行う工程と、突出部201の少なくとも表面を研磨する工程と、有する。

(もっと読む)

1 - 20 / 334

[ Back to top ]