Fターム[5F038EZ12]の内容

Fターム[5F038EZ12]に分類される特許

1 - 20 / 241

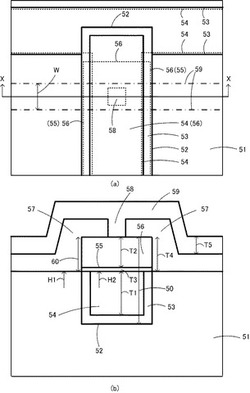

トレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法

【課題】製造コストの増加を抑制し、キャパシタの端部の段差を小さくできるトレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法を提供することにある。

【解決手段】トレンチ52内壁に分離絶縁層53を配置し、この分離絶縁層53を介して下部電極となる第1ポリシリコン54を埋め込んだトレンチ型PIPキャパシタ50を半導体基板に形成することで、キャパシタの端部に形成される段差を低減できる。その結果、配線となるメタル層59を過度に厚くする必要がなく、メタル層59を微細化することができる。その結果、パワーICを微細化することができる。

(もっと読む)

半導体装置

【課題】バイアスに依存した抵抗値の変化をさらに低減できるようにした半導体装置を提供する。

【解決手段】N型シリコン層3と、N型シリコン層3上に形成されたP型拡散抵抗7と、P型拡散抵抗7上に形成されたシリコン酸化膜11と、シリコン酸化膜11を貫いてP型拡散抵抗7の一方の端部7aに接続され、一方の端部7aに高電位を印加するための高電位用電極15と、シリコン酸化膜11を貫いてP型拡散抵抗7の他方の端部7bに接続され、他方の端部7bに低電位を印加するための低電位用電極17と、を備える。高電位用電極15及び低電位用電極17はそれぞれシリコン酸化膜11上に延設されると共に、シリコン酸化膜11上において高電位用電極15と低電位用電極17との間にはスリット21が設けられている。このスリット21は、P型拡散抵抗7の一方の端部7aと他方の端部7bとの間の中間位置23よりも一方の端部7aに近い側に位置する。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3からなるPN接合ダイオード35と、P+型拡散層6と繋がるP+型引き出し層5aをエミッタ、N−型エピタキシャル層4をベース、P型半導体基板1をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構成する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それと接続され、取り囲むN+型拡散層7とはカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、そのときの放電電流I1によりP+型引き出し層5aよりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし、大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

半導体装置

【課題】パッド下のクラックによるショート不良が抑制された半導体装置を提供する。

【解決手段】パッド開口部18aの下の層間絶縁膜16はコンタクト17で囲われているので、ワイヤボンディング時に生じたパッド開口部18aの下の層間絶縁膜16のクラックはコンタクト17の外周縁17aよりも外側に入らない。よって、クラックを通し、パッド開口部18aは、外周縁17aよりも外側のアルミやポリシリコンなどの金属膜や拡散層とショートしない。

(もっと読む)

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

半導体装置

【課題】精度良く形成されたフィンを有しつつ、十分な特性を有するESD保護素子を形成することができる半導体装置を提供する。

【解決手段】実施形態にかかる半導体装置は、制御整流素子を有し、このシリコン制御整流素子は、半導体基板と、第1のウェル領域と、第2のウェル領域と、複数のフィン領域とを有する。第1のウェル領域は半導体基板の最外周に位置する。さらに、ウェルコンタクト領域よりも外周に位置し、第1の導電型の不純物拡散層領域を有し、且つ、電気的に浮遊状態にある最外周フィン領域を有する。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を確保する。

【解決手段】基板と、基板に埋め込まれ、複数の開口部を有する絶縁膜と、複数の開口部内に位置する基板に設けられた複数のダミー拡散層20と、抵抗素子形成領域40において、平面視でダミー拡散層20と重ならないように絶縁膜上に設けられ、かつ第1方向に延伸する複数の抵抗素子10と、抵抗素子形成領域40において、絶縁膜上およびダミー拡散層20上に設けられ、かつ第1方向に延伸する複数のダミー抵抗素子12と、を備え、ダミー抵抗素子12は、平面視で、第1方向と基板に水平な面内において垂直な第2方向に並ぶ少なくとも二つのダミー拡散層20と重なっている。

(もっと読む)

半導体装置

【課題】不要な寄生素子の影響を排除できる低容量の過渡電圧保護素子を提供する。

【解決手段】半導体基板上に第1のエピタキシャル層210を形成し、第1のエピタキシャル層の表面近傍に埋め込み層220を形成し、埋め込み層上に第2のエピタキシャル層211を形成し、第2のエピタキシャル層内に第1のディープ拡散層250を形成し、第1のディープ拡散層内にツェナーダイオードを形成し、ツェナーダイオードから離れた位置に第1のPNダイオードを形成し、ツェナーダイオードは第1の分離層240により分離されており、第1のPNダイオードは第2の分離層241で分離されており、ツェナーダイオードと第1のPNダイオードが埋め込み層を経由して逆方向に直列接続されることにより、不要な寄生素子の影響を排除でき、かつ低容量の過渡電圧保護素子を実現する。

(もっと読む)

フリップチップ半導体ダイのパッドレイアウトを形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】主に半導体ダイの周辺領域中に位置する信号パッドと、主に前記信号パッドから半導体ダイの内部領域中に位置する電力パッドおよび接地パッドとを伴う、ダイパッドレイアウトを有する半導体ダイを提供するステップと、前記信号パッド、電力パッド、および接地パッド上に複数のバンプを形成するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、相互接続部位よりも幅広い、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

半導体装置およびその製造方法

【課題】工程が簡単で、よりラッチアップに強いCMOS構造を得る。

【解決手段】1×1018cm−3から1×1019cm−3の高不純物濃度の半導体基板2を用い、CMOS構造のP型ウェル4とN型ウェル5の境界に設けられた溝分離部13の先端部分がその高不純物濃度領域に達する(エピタキシャル層3を貫通して半導体基板2の領域に至る)ように深く形成することにより、従来のように溝分離部13よりも更に深い領域(溝分離部13の下側)を電子が通過することなく、従来のようにウェル領域内にN+埋め込み層やP+埋め込み層を基板深く埋め込む必要もなく、簡便な方法で、よりラッチアップに強いCMOS構造を得ることができ、コスト性能の両方に優れた半導体装置1を得ることができる。

(もっと読む)

高電圧バイポーラベースESD保護構造

【課題】面積効率の良い高電圧の単極性ESD保護デバイスを提供する。

【解決手段】ESD保護デバイス300は、p型基板303と、基板内に形成され、カソード端子に接続されるn+及びp+コンタクト領域310、312を包含し、第1のpウェル308−1と、基板内に形成され、アノード端子に接続されるp+コンタクト領域311のみを包含する第2の別個のpウェル308−2と、第1及び第2半導体領域を取り囲み且つこれら半導体領域を分離するように基板内に形成された、電気的にフローティングのアイソレーション構造304、306、307−2とを含む。カソード及びアノードの端子に、トリガー電圧レベルを上回る正電圧が印加されると、ESD保護デバイスは、構造を通り抜ける低インピーダンス経路を提供してESD電流を放電するよう、内在サイリスタをスナップバックモードに入らせる。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体抵抗素子

【課題】意図しない不純物による抵抗精度およびノイズ特性の低下を抑制した半導体抵抗素子を提供する。

【解決手段】半導体抵抗素子100は、N型拡散層2と、P型抵抗不純物領域4と、N型抵抗不純物層5と、P型高濃度不純物層7と、タングステンプラグコンタクト12a、12bと、N型高濃度不純物層6と、タングステンプラグコンタクト12cとを備え、N型抵抗不純物層5の不純物濃度は、P型抵抗不純物領域4の不純物濃度よりも高くP型高濃度不純物層7の不純物濃度よりも低い。

(もっと読む)

静電気保護用のMOS型半導体装置

【課題】ESD素子のESD耐量を向上させる。

【解決手段】ESD素子21は半導体基板1表面に形成したP型ウェル領域2上にゲート絶縁膜を介して、一方向に延びた複数本のゲート電極3が相互に平行に設けられており、P型ウェル領域2の表面におけるゲート電極3の直下域がチャネル領域9になっている。そして、チャネル領域9間の領域がN+ソース領域5又はN+ドレイン領域4となっており、N+ソース領域5とN+ドレイン領域4とは交互に配列されている。そして、並列して隣接するゲート電極3間に位置するN+ドレイン領域4を分割し、かつ隣接するゲート電極3を接続するようにゲート電極接合領域10を設ける。なお、ゲート電極接合領域10の直下域にはチャネル領域9と同一の不純物濃度を有する領域11が設けられている。

(もっと読む)

可変容量素子および可変容量素子の製造方法

【課題】 可変容量素子の動作不良を防止し、可変容量素子の信頼性を向上する。

【解決手段】 可変容量素子は、固定電極と、固定電極上に積層された絶縁層を含む絶縁部と、絶縁層上に絶縁層から離れる方向に移動可能に積層された可動部および可動部の一端を絶縁部に固定する固定部を含む可動電極と、可動電極に間隔を空けて対向する対向電極とを有している。

(もっと読む)

DC/DCコンバータ用半導体装置

【課題】半導体装置の電源電圧の変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ローサイドスイッチ用のパワーMOS・FETと、そのローサイドスイッチ用のパワーMOS・FETに並列に接続されるショットキーバリアダイオードD1とを同一の半導体チップ5b内に形成した。ショットキーバリアダイオードD1の形成領域SDRを半導体チップ5bの短方向の中央に配置し、その両側にローサイドのパワーMOS・FETの形成領域を配置した。また、半導体チップ5bの主面の両長辺近傍のゲートフィンガ6aから中央のショットキーバリアダイオードD1の形成領域SDRに向かって、その形成領域SDRを挟み込むように複数本のゲートフィンガ6bを延在配置した。

(もっと読む)

半導体装置の製造方法

【課題】不純物拡散領域の抵抗値のばらつきを抑制しうる半導体装置の製造方法を提供する。

【解決手段】半導体層にドーパント不純物を添加し、0.1秒〜10秒の活性化熱処理を行う。次いで、半導体層にイオン注入を行い、半導体層のドーパント不純物が添加された領域をアモルファス化する。次いで、0.1ミリ秒〜100ミリ秒の活性化熱処理を行い、アモルファス化した半導体層を再結晶化することにより、半導体層にドーパント不純物の拡散領域を形成する。

(もっと読む)

1 - 20 / 241

[ Back to top ]