Fターム[5F038EZ19]の内容

Fターム[5F038EZ19]に分類される特許

1 - 20 / 163

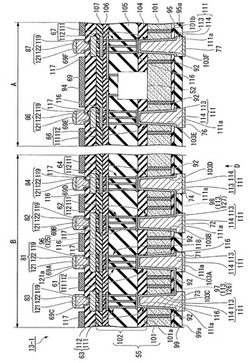

半導体チップ及びその抵抗測定方法、並びに半導体装置

【課題】本発明は、貫通電極のサイズ(直径)が縮小化された場合でも、4端子法により貫通電極の抵抗値を正確に測定することの可能な半導体チップ及びその抵抗測定方法、並びに半導体装置を提供することを課題とする。

【解決手段】半導体基板101及び回路素子層102を有する半導体チップ本体55と、半導体チップ本体55を貫通する第1乃至第4の貫通電極61〜64と、回路素子層102に設けられた回路素子を介することなく、第1の貫通電極61と第2の貫通電極62とを電気的に接続する第1の導電経路96と、回路素子を介することなく、第1の貫通電極61と第3の貫通電極63とを電気的に接続する第2の導電経路97と、回路素子を介することなく、第2の貫通電極62と第4の貫通電極64とを電気的に接続する第3の導電経路98と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる半導体装置及びその製造方法を得る。

【解決手段】半導体基板1の有効領域2と有効領域2の周囲の無効領域3にそれぞれ拡散層4,5を同時に形成する。拡散層4,5上にそれぞれエミッタ電極6及び小信号電極7を同時に形成する。小信号電極7にプローブ12を接触させて拡散層5の電気特性又は拡散層5と小信号電極7のコンタクト抵抗を測定するテストを行う。テストの後に、エミッタ電極6上に開口10を有し、小信号電極7を覆う絶縁膜9を形成する。開口10を介してエミッタ電極6上にメッキ11を形成する。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

半導体ウェハ及びその製造方法

【課題】スクライブ線領域におけるダミーパターンが影響して配線形成の際に露光時のアライメント波形検出精度を低下させるおそれがあった。

【解決手段】複数の素子形成領域と、素子形成領域を相互に区画するスクライブ線領域と、素子形成領域において半導体基板上に配置された複数のパターンと、スクライブ線領域において半導体基板上に配置されるとともに、パターンと同様な構成の複数のダミーパターンと、パターン及びダミーパターンを含む半導体基板上に形成されるとともに、上面が平坦化された層間絶縁膜と、スクライブ線領域における層間絶縁膜に形成されるとともに、ダミーパターンと重ならない領域にて半導体基板に通じないように形成された穴状のアクセサリパターンと、を備える。

(もっと読む)

半導体集積回路及びそれを備えた半導体装置、並びに電子機器

【課題】半導体集積回路において、ダイシング時の保護膜の剥離を抑制しつつ保護膜の密着性を確保し、チップサイズの小型化を実現する。

【解決手段】半導体集積回路は、スクライブ領域2近傍に形成されたシールリング3と、パッド4と、シールリング3とパッド4との間に形成された配線5と、シールリング3と、ダミーパターン8と、保護膜6と、保護膜7とを備えている。保護膜7の終端縁9は、シールリング3とパッド4との間に位置しており、ダミーパターン8における配線5を挟んで互いに向かい合う部分の端部が、保護膜7の終端縁9を中心に半導体チップ1の周縁部側及び中央部側方向に5μmの間隔以内に位置している。

(もっと読む)

半導体ウェハ、半導体装置、及び半導体装置の製造方法

【課題】ヒューズメモリを利用したトリミングを行う半導体ウェハにおける各半導体チップの回路面積を小さくする。

【解決手段】半導体ウェハ10におけるシリコン基板上は、複数個のチップ領域TARとこの領域TARを囲むスクライブ領域SARとに区画されている。チップ領域TARには、トリミング対象回路11と、ヒューズ素子Fm(m=1〜2M)と、ヒューズ素子Fm(m=1〜2M)が断線状態であるか否かを検出する検出回路としての役割を果たす定電流源IPm(m=1〜2M)及びインバータINm(m=1〜2M)とが形成されている。スクライブ領域SARには、制御信号に応じてON/OFFが切り換わり、ONとなることによりヒューズ素子Fm(m=1〜2M)を断線させる電流を発生するNチャネル電界効果トランジスタTSm(m=1〜2M)がある。

(もっと読む)

半導体装置

【課題】LSIチップの製造コストを低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板に形成され、第1の電源配線を含む第1の電源配線層を備える複数のLSI領域と、前記半導体基板に形成された第1の電源端子と、前記LSI領域の間のダイシングライン領域に、前記LSI領域と前記ダイシングライン領域とを区画するダイシングラインに沿って形成され、前記第1の電源配線と前記第1の電源端子とを電気的に接続する第2の電源配線を含む第2の電源配線層と、を備える。少なくとも前記LSI領域において、前記第1の電源配線と前記第2の電源配線との境界にバリアメタル膜が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、光電変換膜が半導体基板上に積層された積層型の半導体装置に関する。

【解決手段】半導体基板と、半導体基板上に形成され、交互に積層された層間絶縁膜と配線層とからなる多層配線層と、多層配線層内において、半導体基板の周縁に沿って環状に形成されたシールリングとを備え、シールリングは、各配線層に形成された環状のシール配線と、各層間絶縁膜に少なくとも1つ形成された環状のシールビアとが積層された構造であり、シールビアを介して積層方向に隣接する少なくとも1組のシール配線では、下方のシール配線の外周面の位置が、上方のシール配線の外周面の位置よりも外側にあることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】電源ノイズを一層効果的に解消する技術を提供する。

【解決手段】半導体装置1は、所定動作を実行するための内部回路6と、内部回路6に対して高電位電圧を供給するための電源ライン7と、内部回路6に対して低電位電圧を供給するためのグラウンドライン8と、ウェハテスト用電極パッド9と、ウェハテスト用電極パッド9を内部回路6に接続するための電気線10と、電気線10を内部回路6に対して非導通状態にすると共に、電気線10を電源ライン7とグラウンドライン8のうち何れか一方に対して選択的に導通状態とする接続切替部11と、を備える。

(もっと読む)

半導体装置

【課題】大量生産が可能で、かつ従来の小型素子とは異なる構造を有する半導体装置を提供する。また、強度を向上させることが可能であり、作製段階における素子の破壊を抑制することができ、信頼性及び歩留まりの高い半導体装置の構造、及び半導体装置の作製方法を提供することを目的としている。

【解決手段】集積回路を有する層と、集積回路を有する層上に形成され、集積回路を有する層と電気的に接続された第1の端子と、第1の端子上に形成され、第1の端子と電気的に接続されたアンテナとして機能する導電層と、集積回路を有する層上に形成され、集積回路を有する層と、アンテナとして機能する導電層と、第1の端子と電気的に接続されていない第2の端子を有する。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

フリップチップ半導体ダイのパッドレイアウトを形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】主に半導体ダイの周辺領域中に位置する信号パッドと、主に前記信号パッドから半導体ダイの内部領域中に位置する電力パッドおよび接地パッドとを伴う、ダイパッドレイアウトを有する半導体ダイを提供するステップと、前記信号パッド、電力パッド、および接地パッド上に複数のバンプを形成するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、相互接続部位よりも幅広い、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

半導体装置、半導体集合部材及び半導体装置の製造方法

【課題】様々なオン抵抗の素子を容易に製造することができる半導体装置、半導体集合部材及び半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、素子部と、第1の電極部と、第2の電極部と、延出部と、を備える。素子部は、基板に設けられる。第1の電極部は、素子部の上に設けられ、素子部と導通する。第2の電極部は、素子部の上において第1の電極部と離間して設けられ、素子部と導通する。延出部は、素子部の上に設けられ、第1の電極部及び第2の電極部の周縁部から基板の周縁部に向けて延出して設けられる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】入出力端子と半導体スイッチとの間を接続する配線同士が交差する箇所が発生しても、端子間のアイソレーション特性を向上させつつ、サイズ及びコストを抑制可能な半導体装置を提供する。

【解決手段】半導体スイッチ回路(20)は、複数の入力端子(31,32)のうち任意の入力端子を配線層(51)又は再配線層(251)を介して複数の出力端子(41〜44)のうち任意の出力端子と接続させるように構成される。複数の入力端子及び複数の出力端子のうち、ある端子と半導体スイッチ回路との間を接続する配線と、他の端子と半導体スイッチ回路との間を接続する配線とが交差している箇所において、交差する配線のうち、一方の配線を配線層とし、他方の配線を再配線層とする。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

半導体装置、電子装置、及び半導体装置の製造方法

【課題】第1インダクタと第2インダクタを構成する金属材料のマイグレーションに起因して第1インダクタと第2インダクタの絶縁が確保できなくなることを、抑制する。

【解決手段】半導体チップ100は配線基板200の第1面上に実装されており、多層配線層を有している。第1インダクタ112は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は第1インダクタ112に対向している。封止樹脂400は、配線基板200の少なくとも第1面と、半導体チップ100とを封止している。溝500は、封止樹脂400と多層配線層の界面のうち、少なくとも第1インダクタ112と第2インダクタ122の間に位置している部分の全域に形成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】工程を追加せずに、アライメントマークの形成領域におけるゲート電極膜の残渣を低減する。

【解決手段】半導体装置の製造方法は、アライメントマーク10を有する第1領域R1と、抵抗体40が形成される第2領域R2と、ゲート電極15が形成される第3領域R3と、を主面1aに有する基板の主面1a上に、金属材料を含有するゲート電極膜11を形成する工程を有する。更に、第1及び第2領域R1、R2のゲート電極膜11を等方性エッチングにより除去する工程を有する。更に、ゲート電極膜11を除去した第2領域R2と、第3領域R3と、に導電膜(ポリシリコン膜13)を成膜する工程を有する。更に、導電膜を成膜する工程の後に、基板の主面1a上にフォトレジスト膜を形成し、アライメントマーク10をアライメントに用いて所定のパターンをフォトレジスト膜に転写する工程を有する。

(もっと読む)

半導体装置

【課題】ダイシング処理に起因する、チップ用パッド同士のショートを抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板と複数の第1のパッドと、複数の第2のパッドとを備える半導体装置であり、第1のパッドは素子形成領域IMC内に、第2のパッドは素子形成領域IMCを取り囲むダイシングライン領域DLR内に形成される。ダイシングライン領域DLRには、第2のパッド同士が電気的短絡を生じさせやすい第1の領域SLRと、第2のパッド同士が電気的短絡を生じさせにくい第2の領域SURとを有している。第1の領域SLRに対向する位置に配置された一部の第1のパッドは、第2の領域SURに対向する位置に配置された残りの第1のパッドよりも、素子形成領域IMCの外縁の1辺BDLから離れて配置されている。

(もっと読む)

リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法

【課題】 リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法に関し、複数種類のデバイス特性をできるかぎり同じ構造のモニタで評価する。

【解決手段】 形状或いはしきい値電圧の少なくとも一方が異なる複数種類のトランジスタを異なった領域に同じ間隔で配置するとともに、前記複数種類のトランジスタの内、設計データにおける設置頻度の比を反映した数のトランジスタのゲート電極同士、ソース電極同士、及び、ドレイン電極同士を電気的に共通に接続する。

(もっと読む)

1 - 20 / 163

[ Back to top ]