Fターム[5F038BH12]の内容

Fターム[5F038BH12]の下位に属するFターム

静電気 (1,330)

誤接続 (27)

高電圧(電源ライン) (490)

Fターム[5F038BH12]に分類される特許

1 - 20 / 25

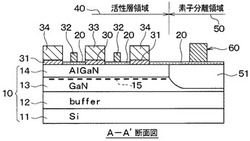

半導体装置およびその製造方法

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

半導体集積回路装置

【課題】レベル変換回路のレイアウト面積の縮小を図る。

【解決手段】半導体集積回路装置(10)は、レベル変換回路(14)と、D/A変換回路(12)とを備える。このとき、パラレル形式のデジタル信号をシリアル形式に変換して上記レベル変換回路に供給するためのパラレル・シリアル変換回路(15)と、上記レベル変換回路の出力をパラレル形式のデジタル信号に変換して上記D/A変換回路に供給するためのシリアル・パラレル変換回路(13)とを設ける。上記レベル変換回路は、シリアル形式のデジタル信号に対応するレベル変換機能を備えていれば良く、パラレル形式のデジタル信号に対応させる場合に比べて、レベル変換回路のレイアウト面積を縮小することができる。

(もっと読む)

入力保護回路および半導体集積回路

【課題】全ての入力端子に対してアナログ電流検出回路を設けなくても、入力端子に入力される信号にもとづくデバイスの誤動作やデバイスの故障を防止することができるようにする。

【解決手段】入力保護回路2は、入力回路11と電流供給源12との間に設けられているスイッチ回路21と、入力信号11における所定時間内の論理レベルの変化を検出するレベル変化検出回路22と、レベル変化検出回路22が検出した論理レベルの変化回数を計数し、計数値が所定のしきい値を越えているか否か判定するレベル変化判定回路23と、レベル変化判定回路23が上記の所定時間よりも長い所定期間において計数値が所定のしきい値を越えていると判定した回数が、所定回数を越えているか否か判定し、所定回数を越えていると判定した場合にスイッチ回路21を遮断状態に設定する異常判定回路24とを含む。

(もっと読む)

半導体装置の電源供給方法、半導体装置の制御方法、半導体装置及び半導体チップ

【課題】同一パッケージ内に複数の半導体チップが搭載された半導体装置において、一部の半導体チップに対する電源供給を、その内部回路を保護しつつ停止することができる、半導体装置の電源供給方法、半導体装置の制御方法、半導体装置及び半導体チップを提供すること。

【解決手段】本発明は、通常時に動作モードが入力側に設定される双方向端子21を有する半導体チップ1と、半導体チップ1と同一パッケージ内に搭載される半導体チップ2と、に電源を供給する。そして、双方向端子21の動作モードを入力側から出力側に切り替える。次いで、半導体チップ1から半導体チップ2にLow信号を出力する。続いて、半導体チップ2の電源供給を停止する。

(もっと読む)

半導体集積回路装置

【課題】 半導体集積回路装置の特性を保持或いは高めると共に小型化を図る。

【解決手段】 主面および前記主面とは反対側の裏面を有し、第1辺を含む平面形状が矩形状の半導体基板と、前記主面上に形成された複数のボンディングパッドと、前記主面上に形成された内部回路形成部と、前記第1辺と前記内部回路形成部との間に配置されており、前記内部回路形成部に電位を供給する内部回路用電源配線と、前記第1辺と前記内部回路用電源配線との間に配置されており、前記複数のボンディングパッドと電気的に接続され、トランジスタを備えた複数のセルと、前記複数のセル上に配置され、前記複数のセルに電位を供給するセル用電源配線と、を有し、前記複数のセルは、外部からの入出力信号を送受信する回路を含む入出力セルを有し、前記複数のボンディングパッドのそれぞれは、前記入出力セルと平面的に重なるように配置されている。

(もっと読む)

固体撮像装置

【課題】固体撮像装置の垂直転送期間で発生するアンダーシュートによる保護回路のブレークダウンを防止する。

【解決手段】垂直転送及び水平転送を行う固体撮像装置50には、転送クロック信号が入力される入力端子と撮像部40の間に保護回路2及び保護回路3が設けられる。保護回路2及び保護回路3には、Pch MOSトランジスタPMT1が設けられる。Pch MOSトランジスタPMT1は、ソースが高電位側電源Vddに接続され、ゲートがソースに接続され、ドレインが撮像部40側(内部回路)と入力端子に接続される。

(もっと読む)

論理回路及び半導体装置

【課題】電気特性の制御された酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体構造、半導体構造の形成方法、半導体装置の動作方法(高周波の高調波を減少するためのSOIRFスイッチ)

【課題】SOI基板における容量結合を減少した集積回路を提供する。

【解決手段】底部半導体層と同じ導電型のドーパントを含む第1のドープされた半導体領域18及び反対導電型のドーパントを含む第2のドープされた半導体領域28がSOI基板の埋め込み絶縁層20の直下に形成される。第1のドープされた半導体領域18及び第2のドープされた半導体領域28は、共にグランド電位に接続されるか、又は底部半導体層への少数キャリアの順方向バイアス注入に基づく過剰な電流を生じるには不十分は電圧、即ち、0.6V乃至0.8Vを越えない電位差を保って底部半導体層に対して順方向バイアスされる。上部半導体の半導体装置内の電気信号により誘起される電荷層内の電荷は第1及び第2のドープされた半導体領域に接続されている電気的コンタクトを介して引き出され、これにより半導体装置内の高調波信号を減少させる。

(もっと読む)

電力スイッチ回路

【課題】従来の電力スイッチ回路では、パワーMOSトランジスタのゲート端子の電圧を精度良く制御することができなかった。

【解決手段】本発明の電力スイッチ回路は、第1の電源端子Vccと出力端子OUTとの間に接続され、負荷2を駆動する出力トランジスタ11と、出力トランジスタ11の異常状態を検出する異常検出回路15と、ウェル領域上に形成される拡散層によって抵抗成分を発生し、入力端子INと出力トランジスタ11の制御端子との間に設けられる抵抗素子12と、異常検出回路15による検出結果に基づきウェル領域に出力端子OUTの電圧と第2の電源端子GNDの電圧とのいずれの電圧を供給するかを切り替えるウェル電位切替回路14と、を有するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】 チップサイズを大きくせずに、大きなサージに耐えうる保護ダイオードを備えた半導体装置を提供する。

【解決手段】 ウエーハと導電型が逆になるような不純物領域8を裏面に複数作製し、ウエーハ表面に作られる内部回路の接地電極2が保護ダイオードのアノード、裏面電極4、5が前記保護ダイオードのカソードとなるように、チップをパッケージする際に前記内部回路の入力端子1と出力端子3をそれぞれ前記裏面電極4、5に結線する。

(もっと読む)

半導体集積回路

【課題】終端抵抗の抵抗値を接触抵抗の影響を除いて正確に測定でき、占有面積の増大を防止できる半導体集積回路を提供する。

【解決手段】半導体集積回路は、少なくとも、第1状態ST1−1の際に、第1,第5制御信号ENPb,VBSを第1電圧レベルとし、前記第2,第3,第4制御信号ENNb,qb,qを第2電圧レベルとし、第2状態ST1−2の際に、前記第1乃至第4制御信号ENPb,ENNb,qb,qを第1電圧レベルとし、前記第5制御信号VBSを任意の電圧レベルとするように構成された制御信号発生回路41を具備する。

(もっと読む)

半導体装置

【課題】電源投入順序によらず、半導体装置における入出力回路を正常に動作させるようにする。

【解決手段】電圧変換回路2により内部電源電圧VDIレベルから外部インターフェイス電源電圧VDEレベルに信号電圧レベルが変換された信号を出力する出力バッファを、外部インターフェイス電源電圧VDEの供給が開始されてから一定期間だけオフ状態にする不正出力抑止回路4Aを設け、内部電源よりも先に外部インターフェイス電源が投入されても、不正に出力状態となることを防止できるようにする。

(もっと読む)

半導体装置、及び半導体装置のテスト方法

【課題】本発明によれば、高品質な半導体装置を提供することにある。

【解決手段】本発明による半導体装置100は、P型ウェル9上に形成される第1Nチャネル型MOSトランジスタ30及び第2Nチャネル型MOSトランジスタ31と、第1N型ウェル8b上に形成される第1P型拡散抵抗41と、第2Nチャネル型MOSトランジスタ31のゲートに接続され、第2Nチャネル型MOSトランジスタ31の駆動動作を制御する制御回路800とを具備する。第1Nチャネル型MOSトランジスタ30のドレインは第1外部端子401に接続され、ソースは第2Nチャネル型MOSトランジスタ31のソースとP型ウェル9とに電気的に接続される。第1P型拡散抵抗41の一端51は、第2Nチャネル型MOSトランジスタ31のドレインに接続され、他端は第2外部端子402と第1N型ウェル8bとに電気的に接続される。

(もっと読む)

半導体装置

【課題】製造コストを増大させることなく、複数の電源パッドを有する半導体装置の小型化を実現できる技術を提供する。

【解決手段】半導体チップ1の中央部に内部回路形成部2を形成する。この内部回路形成部2の周囲を囲むように内部回路用電源配線4a、4bを形成する。そして、内部回路用電源配線4a、4bと一体的に内部回路用電源パッド8a、8bを形成する。内部回路用電源配線4bの外側に複数の入出力セル5を形成し、この入出力セル5の外側にある半導体チップ1の外周部に複数のパッド6を形成する。このパッド6の一部に内部回路用電源パッド7a、7bを形成する。

(もっと読む)

高周波半導体装置及びその製造方法

【課題】 高周波半導体装置において、空間伝搬による高周波信号の漏れが発生し入力部の高周波信号が出力部に悪影響を及ぼす問題がある。これを回避するために入力部と出力部を離間したり、これらの間にボンディングワイヤを固着して接地するなどの方法がとられるが何れもチップ上の入力部と出力部間に十分な離間距離を確保する必要があった。

【解決手段】 基板表面に第1素子と第2素子を設け、基板裏面に接地電位の第1電極を設ける。第1素子と第2素子間に基板を貫通する第2電極を設け、第1電極と接続する。第1素子と第2素子間で空間伝搬による高周波信号の漏れが発生しても、接地電位の第2電極によるトラップにより接地することができる。トラップのために基板表面にワイヤボンド固着領域を確保する必要がなく、チップの小型化寄与し配線レイアウトの自由度も大きくなる。

(もっと読む)

半導体集積回路装置

【課題】内部のESDに対する破壊耐圧を更に向上することができる半導体集積回路装置を提供する。

【解決手段】出力回路14は、各1個のpMOSトランジスタ31及びnMOSトランジスタ32からなるトランジスタ対33を複数有し、複数のトランジスタ対33は、信号電極15及び信号線16の間に接続されCMOSインバータを構成する少なくとも1つのトランジスタ対33からなる第1トランジスタ群34と、CMOSインバータを非構成とする残りのトランジスタ対33からなる第2トランジスタ群35とにグループ分けされている。第2トランジスタ群35の各トランジスタ対33は、pMOSトランジスタ31のソース、ゲート及びドレインがプラス側電源線27に接続され、nMOSトランジスタ32のソース、ゲート及びドレインがマイナス側電源線29に接続されている。

(もっと読む)

静電保護素子及び静電保護回路

【課題】本発明は、静電気から内部回路を保護する静電保護素子及び静電保護回路に関し、静電耐量を大きくして、静電保護素子及び静電保護回路の保護特性を向上させることを課題とする。

【解決手段】半導体基板21に設けられたN型埋め込み拡散層22と、N型エピタキシャル成長層23と、P型アイソレーション層24と、N型カソードコンタクト層27と、P型アノードコンタクト層26とを備えた静電保護素子12であって、N型カソードコンタクト層27とP型アイソレーション層24との間に、N型埋め込み拡散層22を囲む溝28を設け、溝28の底面28AをN型埋め込み拡散層22の底面22Aと略面一とした。

(もっと読む)

半導体チップおよびその駆動方法

【課題】識別コードの作り込みが簡単で低コストであって、かつ、識別コードの読み出しを簡単に行うことができる半導体チップおよびその駆動方法を提供する。

【解決手段】入出力パッドP0〜P4は、入力保護回路10を介して内部回路11に信号を入出力する。識別用ダイオード12は、一例としての識別コード“1010”に応じ、入出力パッドP0,P2に対してそれぞれ設けられている。識別用ダイオード12のアノードは、入出力パッドP0,P2にそれぞれ接続されている。識別用パッドP6は、各識別用ダイオード12のカソードに共通に接続されている。識別用パッド6に接地電圧を印加した状態で、入出力パッドP0〜P4に対して正の電流を印加することにより、上記識別コードが電圧値として読み出される。また、識別用ダイオード12のアノードとカソードとを逆にして接続することも可能である。

(もっと読む)

駆動回路およびデータ線ドライバ

【課題】PDP等を駆動するドライバICの出力回路において、隣接端子間に形成される寄生NPNバイポーラトランジスタが自己ノイズやパネルからのノイズによって動作し、誤動作や破壊の原因になっていた。

【解決手段】端子間の分離領域115に0V以上の電位に固定されるN型拡散層116を設け、トランジスタのドレインをN型ウェル上の高濃度N型拡散層と同電位の高濃度P型拡散層113で形成する。これにより寄生バイポーラトランジスタのコレクタ電流を削減することができるので、通常のCMOSプロセスを用いて、チップサイズを抑制しながら隣接端子間のノイズに対する耐性を向上することができる

(もっと読む)

半導体装置

【課題】 小さな電流能力しか持たない信号源によるスイッチ制御と保護機能を備えたパワーMOSFETを備えた半導体装置を提供する。

【解決手段】 第1端子にドレインを接続し、第2端子に上記パワーMOSFETのソースを接続し、上記第3端子と上記パワーMOSFETのゲートの間に高抵抗手段を接続する。上記パワーMOSFETに流れる電流を検出する電流検出手段の出力信号を受けて上記パワーMOSFETに流れる電流を制限する電流制限回路を上記パワーMOSFETのゲートと上記第2端子との間に設ける。

(もっと読む)

1 - 20 / 25

[ Back to top ]