Fターム[5F038EZ08]の内容

Fターム[5F038EZ08]の下位に属するFターム

CAD、DA (704)

シミュレーション評価 (439)

Fターム[5F038EZ08]に分類される特許

161 - 180 / 453

回路装置の検査装置、検査方法及び製造方法

【課題】回路装置に検査用のパッドや専用の付加回路を設けることなく、回路装置に含まれた複数のモジュールに欠陥があるか否かを判定できる検査装置とその検査方法を提供する。また、上記の検査方法を用いることによって回路サイズの増大を抑制しつつ欠陥を救済できる回路装置の製造方法を提供する。

【解決手段】半導体集積回路は、互いに機能を代替可能な複数のモジュールを含んでいる。複数のモジュールの全体に割り当てる機能を同一に保ちつつ、その少なくとも一部において個々のモジュールに割り当てる機能を変更するように、半導体集積回路を制御する。そして、モジュール機能の割り当ての変更に応じた半導体集積回路の機能の変化を検出し、当該検出結果に応じて、上記少なくとも一部のモジュールに欠陥のあるモジュールが含まれるか否かを判定する。

(もっと読む)

半導体デバイス

【課題】半導体デバイスの閾値電圧の制御を実現しつつ、より小さな回路面積の半導体デバイスを提供する。

【解決手段】印加される基板バイアス(Vnw)(Vpw)に応答してMOSトランジスタ(14)(15)の閾値電圧を決定する半導体デバイス(1)において、前記半導体デバイス(1)は、基板バイアス(Vnw)(Vpw)を生成する基板バイアス生成部を具備する。また、前記半導体デバイス(1)は、クロック信号線(3)と他の配線とをシールドするシールド配線(4)(5)を具備する。そして、その基板バイアス生成部は、前記シールド配線(4)(5)を介して前記基板バイアス(Vnw)(Vpw)を半導体基板(12)(13)に印加する。

(もっと読む)

半導体集積回路およびその製造方法

【課題】占有面積の増大を抑制しつつ、高性能のテスト回路を備えた半導体集積回路装置を提供する。

【解決手段】テスト対象回路を構成しているセルおよびテスト回路を構成するために準備された未接続セルの配置位置を決定した後に、それらの配置情報に基づいて、テスト回路を構成するために準備された未接続セルの接続関係を決定し、テスト回路を構成することによりテスト回路を備えた半導体集積回路を提供する。

(もっと読む)

スタンダードセル、半導体集積回路、半導体集積回路の設計方法、半導体集積回路の設計装置、及びスタンダードセルライブラリ

【課題】基板電圧制御技術を実装したスタンダードセルにおいて、設計自由度を高めながら設計工数を少なくする。

【解決手段】スタンダードセル300は、通常電源配線160、161が予め設定した位置に配置されている。従って、このような通常電源配線160、161を持つ他のスタンダードセルが隣接して配置された場合には、これ等の通常電源配線160、161は互いに結線される。更に、スタンダードセル300には、前記他のスタンダードセルを隣接して並べたとき、互いに接続されない基板用電源端子120が配置される。従って、複数のスタンダードセル300を並べて半導体集積回路を構成する場合には、セル間基板電源配線の配線経路などを自由に設定でき、設計自由度が向上する。

(もっと読む)

半導体装置

【課題】給電経路に挿入される半導体スイッチの特性が全体の動作に及ぼす影響とのバランスを図りながら、リーク電流を効果的に削減できる半導体装置を提供する。

【解決手段】回路ブロック1の動作状態に応じて、その給電経路に挿入される半導体スイッチSW1,SW2のリーク電流に係わる特性が制御される。例えば、スリープモードにおいて半導体スイッチSW1,SW2のリーク電流が小さくなり、アクティブモードにおいて半導体スイッチSW1,SW2の導通抵抗が低くなるように基板バイアス電圧Vn_well,Vp_wellを制御する。これにより、半導体スイッチSW1,SW2の導通抵抗に起因するアクティブモード時の電源電圧変動を抑制しつつ、スリープモード時のリーク電流を効果的に低減することができる。

(もっと読む)

ダイレクトチャージ型スイッチト・キャパシタ回路を含む電気回路

【課題】スイッチト・キャパシタ回路における寄生容量の影響を抑制する。

【解決手段】 キャパシタCの第1の端子に入力信号を供給し、第2の端子を基準電位に維持させることによってキャパシタCに入力信号の強度に応じた電荷を蓄積させる第1のモードと、キャパシタCの第1の端子をオペアンプ50bの出力端子TbOUTに接続し、第2の端子をオペアンプ50bの反転入力端子Tb(−)に接続する第2のモードとを選択可能とするスイッチング素子Toa,Tia,Tob,Tibとを含むメモリ単位52を少なくとも1つ備え、メモリ単位52に含まれるキャパシタCは、半導体基板の表面のウェル、ウェル上に形成された絶縁膜及び電極層とによって構成され、電極層をキャパシタの第1の端子とし、ウェルをキャパシタの第2の端子とすることによって上記課題を解決することができる。

(もっと読む)

半導体集積回路の設計方法および半導体集積回路

【課題】

アンテナ基準を満足するMOSFETとダミーのMOS容量素子を形成することにより、アンテナ効果による素子破壊を防止する半導体集積回路の設計方法および半導体集積回路に関する。

【解決手段】

半導体基板4上に形成されたゲート配線層2と、トランジスタ形成領域上の前記ゲート配線層2下部に形成されたゲート酸化膜5と、半導体基板4上の前記ゲート配線層2下部に形成されたダミーゲート酸化膜13とを有し、前記ゲート酸化膜5と前記ダミーゲート酸化膜13を合わせた電荷許容量が、予め設定された値以上であることを特徴とする半導体集積回路である。

(もっと読む)

昇圧回路

【課題】レイアウトの小面積化を実現する標準CMOSプロセスのLSIに混載可能な昇圧回路を提供する。

【解決手段】各段がMOSトランジスタ(M04、M14、M24、M34)と、前記MOSトランジスタのドレイン又はソースの一方に一端が接続されたキャパシタ(C14、C24a、C24b、C34a、C34b、C34c)とからなり、前記MOSトランジスタが縦列接続されることによって各段が接続され、各段における前記MOSトランジスタのゲートとドレイン又はソースの一方とが互いに電気的に接続されるとともに、少なくとも1組の隣接するMOSトランジスタの基板がその一方のドレイン又はソースの一方と電気的に接続される。バックバイアス効果が抑制され、かつレイアウト面積を縮小することができる。また、後段の昇圧キャパシタを複数の直列キャパシタで構成することにより、各キャパシタの耐圧劣化を抑制することができる。

(もっと読む)

半導体装置のコンタクト不良検査方法及びその検査方法が適用される半導体装置

【課題】ボルテージコントラスト検査を行う場合における検査パターンを有効に利用してコンタクトチェーンの不良を検出する。

【解決手段】基板検査方法は、基板の第1層に配置された複数の第1導電素子と、基板の第2層に配置された複数の第2導電素子と、第1導電素子と第2導電素子とを第1層と第2層との間で接続するコンタクトホールとの組み合わせによる導電路を検査領域の周辺部から中央部に至る経路に形成し、検査領域に電子線を照射することによって検査領域から放出される電子を検出する。

(もっと読む)

半導体装置

【課題】ヒューズ素子を備えた半導体装置において静電ノイズの影響を抑制する。

【解決手段】スイッチング素子26と、第1及び第2のヒューズ素子22,24とを備え、第1のヒューズ素子22とスイッチング素子26とは直列接続され、その直列回路の両端は共に基準電位(接地電位GND)に保持された基準ラインに接続され、第1のヒューズ素子22とスイッチング素子26との接続点に第2のヒューズ素子24の一端が接続され、第2のヒューズ素子24の他端に制御電圧を印加することによって第1のヒューズ素子22を溶断することができる半導体装置によって上記課題を解決することができる。

(もっと読む)

半導体ウェハ及びそのレイアウト設定方法並びにレチクルレイアウト設定方法

【課題】デバイスチップ領域及びスクライブラインの幅を広げることなく、アライメントマークを配置する。

【解決手段】半導体ウェハに、デバイスチップ領域2を2つ以上含む複合チップ領域4がX軸方向及びY軸方向に複数配置されている。デバイスチップ領域2を分離するための複数のスクライブライン6がX軸及びY軸に平行に形成されている。複合チップ領域4に、半導体ウェハの位置合わせを行なうためのアライメントセル8が、複合チップ領域4内において隣り合うデバイスチップ領域2の間のスクライブライン6に複合チップ領域4内のデバイスチップ領域数よりも少ない個数で形成されている。

(もっと読む)

半導体集積回路

【課題】 I/O部からのノイズの侵出を低減することができる半導体集積回路を提供する。

【解決手段】 この半導体集積回路1は、半導体基板2の外周に沿って環状に形成されたN型のレトログレードウェル8と、レトログレードウェル8の上層に形成されたPウェル15と、Pウェル15の周囲を囲うようにレトログレードウェルの上層に形成されたNウェル13、21と、半導体基板2に形成されたNウェル23と、NMOSトランジスタ31がPウェル15の中に形成され、PMOSトランジスタ32がNウェル23の中に形成されたI/Oセル7とを具備する。

(もっと読む)

半導体装置

【課題】ヒューズ素子を備えた半導体装置において静電ノイズの影響を抑制する。

【解決手段】第1から第3のヒューズ素子22,24,26を備え、第1のヒューズ素子22の第1端子は所定の基準電位Vccに保持された基準ラインに接続され、第1のヒューズ素子22の第2端子は第2のヒューズ素子24の第1端子及び第3のヒューズ素子26の第1端子と接続され、第2のヒューズ素子24の第2端子は第1の電極28に接続され、第3のヒューズ素子26の第2端子は第2の電極30に接続される。これによって、上記課題を解決することができる。

(もっと読む)

マルチチップパッケージ型半導体装置

【課題】 複数の半導体チップの実装状態の管理が可能なマルチチップパッケージ型半導体装置を提供する。

【解決手段】 本発明のマルチチップパッケージ型半導体装置は、モジュール基板10、第1の半導体チップ15、第2の半導体チップ25、およびこのモジュール基板10上に実装され、書き込み可能で電気的に読み出し可能な不揮発性メモリチップ35とを備え、この不揮発性メモリチップ35に、第1の半導体チップ15および第2の半導体チップ25の実装状態を示す実装管理データ、製造履歴を示す製造管理データ、および購入履歴を示す購入管理データを記憶させている。

(もっと読む)

ヒューズトリミング回路

【課題】ヒューズ素子の未切断か切断かを精度良く判定し、信頼性の向上と低消費電力化を図る。

【解決手段】NMOS34−1,34−2のソース抵抗の大小関係で決まるそれらドレイン電流Ids34-1,Ids34-2の大小関係によって、ヒューズ素子35−2の未切断か切断かをヒューズ状態判定回路30Aで判定して、結果をラッチ回路30Bに保持し、その判定動作後は、ペアNMOS34−1,34−2のゲートに印加するバイアス電圧Bias0を発生させるバイアス回路20を停止させ、バイアス電圧Bias0をGNDレベルにしてドレイン電流Ids34-1,Ids34-2が流れない構成にしている。これにより、ヒューズ素子35−2に切り残しがあって未切断状態の場合でも、(抵抗素子35−1の抵抗R35-1<ヒューズ素子未切断抵抗R34-2)であれば、未切断か切断かを的確に判定できる。

(もっと読む)

半導体装置

【課題】ヒューズ素子を備えた半導体装置において静電ノイズの影響を抑制する。

【解決手段】スイッチング素子24と、スイッチング素子24と直列に接続され、スイッチング素子24が導通状態となることによって流れる電流によって溶断するヒューズ素子22と、を備え、スイッチング素子24を制御する制御信号を印加するための制御ライン28に静電破壊を防止するための静電破壊防止回路30を接続することによって上記課題を解決することができる。

(もっと読む)

半導体装置

【課題】 従来より少ない占有面積及び測定端子数で多種の配線評価を可能とする。

【解決手段】 配線のオープン不良とショート不良とを評価するために複数のスネークアンドコム回路3を設ける。複数のスネークアンドコム回路3の各スネーク回路部の一端に電圧印加用端子4Aを共通に接続し、各コム回路部の一端に電圧印加用端子4Bを共通に接続し、各スネーク回路部および各コム回路部の共通の他端にそれぞれ複数の抵抗7の一端を接続し、複数の抵抗7の他端に電流測定用端子5を共通に接続する。電圧印加用端子4Aと各スネーク回路部の一端との間に第1の逆流阻止ダイオードを個別に挿入する。複数の抵抗の各々は、複数の評価素子の各々と複数の抵抗の各々とからなる直列回路の何れか一つの抵抗値または何れか二つ以上の並列合成抵抗値と直列回路の残りの何れか一つの抵抗値または何れか二つ以上の並列合成抵抗値とが一致しないように、抵抗値が設定されている。

(もっと読む)

バス回路及び半導体回路

【課題】波形品質の劣化、電源バウンス、及び電磁波放射を抑制して、高速動作を実現すると共に、使用ピンの数の増大及び回路規模の拡大を抑制することができるようにする。

【解決手段】バス回路10は、伝送線路12と、伝送線路12の送信端に接続されたオープンドレインのPMOS素子からなる駆動スイッチング回路14と、一端が伝送線路12の受信端に接続された終端抵抗16と、インダクタンス成分を有する接続回路20を介して、終端抵抗16の他端に接続され、終端電位となっている電源22と、終端抵抗16の一端に接続され、かつ、信号を受信するためのレシーバ素子18とを備える。バス回路10は、ドレインが、終端抵抗16を迂回するように接続回路20を介して電源22に接続され、ソースが接地されているNMOS素子からなる迂回スイッチング回路24を備え、迂回スイッチング回路24のゲートは伝送線路12の受信端に接続されている。

(もっと読む)

半導体装置および集積回路の設計方法

【課題】 回路の変更または追加に柔軟に対応することを可能としつつ、スタンダードセルとゲートアレイとを混在させる。

【解決手段】 半導体チップには、I/O部1、IPマクロ部2〜5およびランダムロジック部6が配置され、ランダムロジック部6には、スタンダードセルおよびゲートアレイを混在させて配置するとともに、スタンダードセルとゲートアレイが配置されたランダムロジック領域6の残りのスペースには、ゲートアレイからなる基本セルを敷き詰めて配置する

(もっと読む)

半導体装置

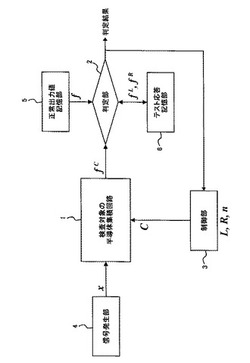

【課題】半導体装置の実装後にAC信号のタイミングの最適な自動調整を可能にする。

【解決手段】外部と送受信するAC信号を監視し予め選定されたACパラメータの値を測定するACパラメータ抽出手段102と、測定されたACパラメータの値を所定の基準と比較しACパラメータの判定情報を出力するACタイミング判定手段103と、AC信号に対して可変に遅延を付与することができる遅延調整手段105と、遅延調整手段105を構成する遅延素子の遅延時間を測定する遅延素子測定手段106と、ACパラメータの判定情報および測定された遅延素子の遅延時間に基づきAC信号に対する遅延付与方法を指定する遅延制御情報を出力するACタイミング制御手段104とを備え、遅延調整手段105はACタイミング制御手段104が出力する遅延制御情報に従いAC信号に対して可変に遅延を付与する。

(もっと読む)

161 - 180 / 453

[ Back to top ]