Fターム[5F038EZ15]の内容

Fターム[5F038EZ15]に分類される特許

141 - 160 / 1,501

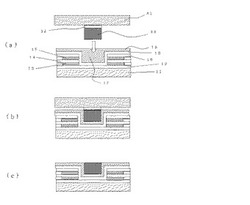

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離酸化膜上に所望の形状の抵抗素子を形成して、抵抗値の精度を高めて信頼性を向上させる。

【解決手段】半導体基板1の表面に形成された所定領域の素子分離酸化膜2上に複数の抵抗素子4が形成された半導体装置であって、抵抗素子4と近接する位置に活性領域3を設けた。抵抗素子4近傍の素子分離酸化膜2を必要な範囲に区切ることができ、CMP法による素子分離酸化膜2の研磨の際に素子分離酸化膜2の中央部に凹みが形成されてしまうことを抑止できるため、抵抗素子4の形状の寸法精度を向上させることが可能となる。

(もっと読む)

フリップチップ半導体ダイのパッドレイアウトを形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】主に半導体ダイの周辺領域中に位置する信号パッドと、主に前記信号パッドから半導体ダイの内部領域中に位置する電力パッドおよび接地パッドとを伴う、ダイパッドレイアウトを有する半導体ダイを提供するステップと、前記信号パッド、電力パッド、および接地パッド上に複数のバンプを形成するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、相互接続部位よりも幅広い、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

プラズマ処理方法、記憶媒体及びプラズマ処理装置

【課題】高誘電率絶縁膜のエッチング制御性を向上することができるプラズマ処理方法を提供する。

【解決手段】ウエハW上の半導体デバイスに形成されたハフニウム酸化膜にエッチング処理を施す際、ウエハWをプラズマ処理装置10のチャンバ11内に搬入し、該チャンバ11内の処理空間SにC4F8ガス、一酸化炭素ガス、アルゴンガス及びキセノンガスを所定の流量比で供給し、処理空間Sに高周波電力を印加して供給された処理ガスからプラズマを発生させ、キセノンによってC4F8からのフッ素の解離をより促進して高いエッチレートで高誘電率絶縁膜をエッチングする。

(もっと読む)

半導体チップ、半導体装置、及び半導体チップの製造方法

【課題】2次電池パックの保護回路を更に小型化すること。

【解決手段】本発明に係る半導体チップは、双方向スイッチを構成する2個のパワートランジスタと、抵抗素子とを備える。2個のパワートランジスタのドレイン同士は接続されている。抵抗素子の一端は、2個のパワートランジスタのうち一方のソース電極と電気的に接続され、その他端は、第1外部パッドと電気的に接続されている。それら2個のパワートランジスタと抵抗素子とは、同一の半導体チップ上に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】工程が簡単で、よりラッチアップに強いCMOS構造を得る。

【解決手段】1×1018cm−3から1×1019cm−3の高不純物濃度の半導体基板2を用い、CMOS構造のP型ウェル4とN型ウェル5の境界に設けられた溝分離部13の先端部分がその高不純物濃度領域に達する(エピタキシャル層3を貫通して半導体基板2の領域に至る)ように深く形成することにより、従来のように溝分離部13よりも更に深い領域(溝分離部13の下側)を電子が通過することなく、従来のようにウェル領域内にN+埋め込み層やP+埋め込み層を基板深く埋め込む必要もなく、簡便な方法で、よりラッチアップに強いCMOS構造を得ることができ、コスト性能の両方に優れた半導体装置1を得ることができる。

(もっと読む)

パワー半導体デバイスおよびその製造方法

【課題】改善されたパワーデバイスに加えてそれらの製造方法,パッケージ化の実施例を提供する。1実施例としては、シールドされたゲートトレンチMOSFETにおいて、多くの電荷調整技術と寄生容量を低減する他の技術とを組み合わせて、改善された電圧性能,速いスイッチング速度および低いオン抵抗を有するパワーデバイスを提供する。

【解決手段】シールドポリ311の上にゲートポリ310を含み、垂直方向電荷制御のために、ゲートトレンチ302より深い位置にある非ゲートトレンチを含み、電荷制御トレンチ301は、トレンチの最上部でソース金属に接続する導電材料の単層を有し得るが、独立してバイアスがかけられ、多重に積み重ねられたポリ電極313を使用する。また、デュアルゲート構造を用いることによってゲートとドレインとの間の容量Cgdを低減する。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化されても高精度を維持できるキャパシタを提供する。

【解決手段】キャパシタは、平面上に交互に配列した、直線状で第1の長さを有し第1の方向に延在する第1の電極パターンと、直線状で前記第1の長さより短い第2の長さを有し、前記第1の方向に延在する第2の電極パタ―ンと、前記第1の電極パターンに第1の電圧を、第1のビアプラグを介して供給する第1の配線パタ―ンと、前記第2の電極パターンに第2の電圧を、第2のビアプラグを介して供給する第2の配線パタ―ンと、を備え、前記第1および第2の電極パターンをそれぞれの前記第1の方向で比較した場合、前記第1の電極パターンの第1の端部が、前記第1の端部に対応する前記第2の電極パターンの第2の端部よりも突出しており、前記第1の電極パターンの前記第1の端部に対向する第3の端部が、前記第3の端部に対応する前記第2の電極パターンの第4の端部よりも突出している。

(もっと読む)

半導体装置、半導体集合部材及び半導体装置の製造方法

【課題】様々なオン抵抗の素子を容易に製造することができる半導体装置、半導体集合部材及び半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、素子部と、第1の電極部と、第2の電極部と、延出部と、を備える。素子部は、基板に設けられる。第1の電極部は、素子部の上に設けられ、素子部と導通する。第2の電極部は、素子部の上において第1の電極部と離間して設けられ、素子部と導通する。延出部は、素子部の上に設けられ、第1の電極部及び第2の電極部の周縁部から基板の周縁部に向けて延出して設けられる。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】半導体装置に用いられるキャパシタを効率よく、しかも少ない占有床面積で行うことができる半導体装置の製造方法および基板処理装置を提供する。

【解決手段】基板200上に下電極を形成する工程(S104)と、下電極の上に、それぞれ異なる金属元素を含む3種の金属酸化膜を積層して誘電膜を形成する工程(S106、S108、S110)と、誘電膜の上に、上電極を形成する工程(S112)と、を有し、各工程は同一の装置で行う。

(もっと読む)

抵抗素子および抵抗素子の製造方法

【課題】膜厚のばらつきに起因する抵抗値の変動を抑制し、より高精度な抵抗素子を提供する。

【解決手段】第1膜厚(T1)(H1)で形成され、第1幅(W1)を有する抵抗素子第1部分(2)と、第1膜厚(T1)(H1)で形成され、第1幅(W1)に依存して決定する第2幅(W2)を有する抵抗素子第2部分(3)とを具備する抵抗素子を構成する。ここにおいて、第1幅(W1)と第2幅(W2)との和は一定である。また、抵抗素子第1部分(2)は、抵抗素子第1部分(2)の底面からの高さが第1高さ(H1)となる位置に、抵抗素子第1部分(2)の上面を有する。また、抵抗素子第2部分(3)は、抵抗素子第1部分(2)の底面を含む面からの高さが第1高さ(H1)となる位置に、抵抗素子第2部分(3)の上面を有する。そして、抵抗素子第1部分(2)と抵抗素子第2部分(3)とは、接続部を介して互いに接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

電子装置およびその製造方法

【課題】半導体基板に設けられた貫通穴に、絶縁体を介して2つの導電体を充填してなるキャパシタ構造体を有する電子装置において、2つの導電体間の容量を大きくするのに適した構成を提供する。

【解決手段】半導体基板10の表裏両主面11、12間を貫通する貫通穴30には、当該穴の内面側から第1の導電体40、絶縁体50、第2の導電体60が順次充填されてキャパシタ構造体20が形成されており、キャパシタ構造体20は、貫通穴30の内部から半導体基板10の両主面11、12まで連続して形成され、キャパシタ構造体20の静電容量は、キャパシタ構造体20のうち貫通穴30に位置する部位の容量と両主面11、12に位置する部位の容量との合計とされている。

(もっと読む)

半導体装置の作製方法

【課題】必要十分なキャパシティをもつ保持容量を備えた半導体装置を提供する。

【解決手段】金属表面を有する基板11と、前記金属表面を有する基板上に形成された絶縁膜12と、前記絶縁膜上に形成された画素部とを有する半導体装置において、前記画素部は、TFTと、該TFTと接続する配線21とを有しており、保持容量は、前記金属表面を有する基板、前記絶縁膜および前記配線により構成されている。前記絶縁膜の膜厚が薄いほど、また、前記絶縁膜と前記配線の接する領域の面積が大きいほど、大きなキャパシティを得られるので有利である。

(もっと読む)

半導体装置

【課題】無線通信によりデータの交信を行う半導体装置において、装置を大型化することなく、アンテナの感度を向上させ、チップをノイズから保護することを課題とする。

【解決手段】コイル状のアンテナと当該コイル状のアンテナに電気的に接続された半導体集積回路とを有する。コイル状のアンテナと重なるように半導体集積回路を配置する。このように、半導体装置内のコイル状のアンテナと半導体集積回路の配置を工夫することで、装置を大型化することなく、アンテナの感度を向上させて、半導体集積回路が動作するために十分な電力を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲート電極を備えるトレンチゲート構成のパワーMISFETにおいて、MISFETの性能向上を図りながら、ゲート絶縁膜の静電破壊を防止することができる技術を提供する。

【解決手段】ダミーゲート電極9aを備えるトレンチゲート構成のパワーMISFETと保護ダイオードとを同一の半導体基板1上に形成する。そして、保護ダイオードをソース電極24とゲート配線25の間に設ける。このような半導体装置の製造方法において、ダミーゲート電極9a用のポリシリコン膜と保護ダイオード用のポリシリコン膜を同時に形成する。また、パワーMISFETのソース領域と保護ダイオードのn+型半導体領域15を同一工程で形成する。

(もっと読む)

有機抵抗による基準電圧発生回路、それを備えたA/D変換回路

【課題】アナログオプション回路を備えた半導体集積回路(A/D変換)を構成する抵抗を、簡便かつ大面積を専有されることなく作成する製造方法、及びその製造方法により作成されるAD変換回路を提供する。

【解決手段】高電源の電圧と低電源の電圧との間に直列に接続された複数個の抵抗からなるストリング抵抗を備えた基準電圧発生部と、入力アナログ電圧値と前記抵抗間の接続点の分圧電圧値とを比較する電圧比較部とを含むA/D変換回路において、

前記抵抗が有機材料で形成されていることを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

キャパシタ構造体およびその製造方法

【課題】シリコン基板に設けられた穴の内部に導電体と誘電体を配置することにより、キャパシタを構成してなるキャパシタ構造体において、穴をより深くしたり、穴の平面形状を複雑な形状とすることなく、導電体間の対向面積を増加させて容量値の増大が実現できるようにする。

【解決手段】穴20は、シリコン基板10の一方の主面に開口する有底穴であり、穴20の内部にはシリコン基板10よりなる突起21が設けられ、穴20の底面は、突起21による凹凸面とされており、穴20の内部では、穴20の底面および側面に、これらの面側から第1の導電体31、誘電体40、第2の導電体32が順次積層されているとともに、第1の導電体31および誘電体40は、突起21による凹凸面の形状を承継した層形状とされている。

(もっと読む)

141 - 160 / 1,501

[ Back to top ]