Fターム[5F044AA14]の内容

ボンディング (23,044) | ワイヤによるペレット電極との接続構造 (951) | ペレット電極のワイヤの接続部 (106)

Fターム[5F044AA14]の下位に属するFターム

保護膜を形成しているもの (20)

Fターム[5F044AA14]に分類される特許

1 - 20 / 86

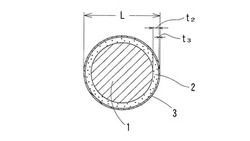

ボンディングワイヤ及びその製造方法

【課題】集積回路間の縮小化の要求に応えた、安定した接合強度を有する純銅にPdを被覆したボンディングワイヤを提供する。

【解決手段】集積回路素子電極aと回路配線基板導体配線cをボールボンディング法によって接続するための線径L50.8μm以下のボンディングワイヤWである。芯材1が純銅及び不可避不純物からなり、その芯材1の外周全面に、Pdによる厚みt2:0.010〜0.090μmの被覆層2を形成し、その表面に0.0001〜0.0005μm厚t3の炭素濃縮層3を形成する。また、調質熱処理の炉温度:400℃以上800℃以下、同処理時間は0.33〜1秒で行なって、室温での引張試験による引張強さTSRと250℃での引張試験による引張強さTSHの比(HR=TSH/TSR×100)を50〜70%とする。その炭素濃縮層3は、伸線時の潤滑剤の洗浄度合によって形成する。

(もっと読む)

半導体装置

【課題】ワイヤボンドの非有効エリアとされていた、傾斜部やビア上、ビアカバー上に安定に、かつ少ない接続面積でワイヤを接続できる半導体装置を提供する。

【解決手段】開口部と、開口部内に設けられたダイパッドと、開口部の周囲に設けられた傾斜部と、インナリードと、を有するパッケージと、第1の電極パッドを有し、かつ、ダイパッド上に搭載された半導体チップと、インナリードと第1の電極パッドとを接続する第1のワイヤと、を備え、インナリードの少なくとも一部は、傾斜部上に配置され、前記傾斜部上において、かつ、前記インナリード上には、第1の部材が配置され、前記第1の部材上には、前記第1のワイヤが接続されている半導体装置を提供する。

(もっと読む)

厚膜レジストの現像方法、及び半導体デバイスの製造方法

【課題】生産性を低下させることなく、基板の外周部にレジスト残渣が発生することを抑制可能な厚膜レジストの現像方法、及び半導体デバイスの製造方法を提供する。

【解決手段】回路素子層の上面に、厚膜レジストを形成する工程と、厚膜レジストを露光する工程と、露光後に、30〜50rpmの範囲内の一定の回転速度で炭化珪素基板を回転させながら、厚膜レジストの上方から現像液を供給することで、厚膜レジストの上面に現像液よりなるパドルを形成し、該パドルにより厚膜レジストを現像して、厚膜レジストに回路素子層の上面を露出する開口部を形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】所定値以上の厚みを有するパッドを少ない工程数で形成することができる半導体装置の製造方法を提供すること。

【解決手段】本発明は、アルミ層22を、半導体基板上に形成された層間絶縁膜1の上方に堆積させる。アルミ層22上には、アルミ層24を堆積させる。パッド領域102のアルミ層24の上方に、フォトレジスト7を形成する。フォトレジスト7を用いてエッチングを行うことにより、パッド領域102にパッド上層52を形成するとともに、配線領域101のアルミ層24を除去する。そして、フォトレジスト8を、パッド領域102のパッド上層52を覆い、かつ、配線領域101で配線パターンを構成するように形成する。フォトレジスト8を用いてエッチングを行うことにより、パッド領域102にパッド下層51を形成するとともに、配線領域101に配線2を形成する。

(もっと読む)

半導体チップの実装方法、及び光電変換モジュールの製造方法

【課題】フェイスアップ実装方法において、低コストで半導体チップを損傷する虞のない半導体チップの実装方法を提供する。

【解決手段】主平面20Aと、裏面20Bとを備えた半導体チップ20を基板10上に実装する半導体チップ実装方法であって、半導体チップ20の主平面20Aにチップ側バンプ41を形成するチップ側バンプ形成工程と、ピックアップ手段60の吸着面61にチップ側バンプ41を当接させながら半導体チップ20をピックアップするピックアップ工程と、裏面20Bが基板10と対向するように半導体チップ20を基板10の所定位置に載置する載置工程と、半導体チップ20を基板10に固定する固定工程と、を有する半導体チップの実装方法により上記課題が解決される。

(もっと読む)

半導体装置

【課題】信頼性の低下を抑制し得る半導体装置を提供する。

【解決手段】半導体装置2は、表面に表面電極44が形成されている半導体素子40と、表面電極44上に接合される導電板材50と、を有している。導電板材50は、表面電極44と対向する底面102と、底面102と反対側であって、大電流用ワイヤ60がボンディングされる領域を有する上面104とを備える。上面104の面積は底面102の面積より大きい。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の組み立てにおけるボイドの発生を抑制する。

【解決手段】一対の第1辺3aa,3ab及び一対の第2辺3ac,3adを有する四角形からなるダイパッド3aにMCUチップ1とAFEチップ2を搭載し、MCUチップ1及びAFEチップ2にワイヤボンディングを行った後、2つの第2辺3ac,3adのうちの一方の第2辺3ac側から他方の第2辺3ad側に向かって樹脂を供給し、前記樹脂をMCUチップ1上の第1パッド群1ccと第2パッド群1cdとの間の開口に通してチップ間を充填することで、チップ間の領域におけるボイドの発生を抑制する。

(もっと読む)

ワイヤーボンディング方法、及び、半導体装置

【課題】半導体チップを搭載する半導体装置の大きさを拡大することなく、隣り合う電極パッド間やボンディングワイヤー間で電流が流れるのを防止又は可及的に抑制することのできるワイヤーボンディング方法及び半導体装置を提供する。

【解決手段】第1電極パッド3に対するボンディングワイヤーW1と、第1電極パッド3に隣り合う第2電極パッド4に対するボンディングワイヤーW2とを、互いに隣り合わないボンディングポイントでボンディングするようにした。

(もっと読む)

半導体装置の製造方法

【課題】実施形態によれば、オーバーハング部に対するワイヤボンディング不良を防ぐ半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、実ボンディング時におけるボンディングヘッドが接地基準位置をサーチする下降速度及び荷重と同じ下降速度及び荷重でもってボンディングヘッドをオーバーハング部のボンディングパッドに対して下降させて接触させ、接地基準位置を予め取得する。実ボンディングでは、半導体チップにおける下方の支持体から張り出したオーバーハング部に形成されたボンディングパッドに対する前記接地基準位置までボンディングヘッドを下降させて、ボンディングヘッドの先端でワイヤをボンディングパッドに押し付けて接合する。

(もっと読む)

電力用半導体装置

【課題】モールド樹脂注入時にワイヤが倒れることを防止し、チップエッジからワイヤまでの距離を大きくして絶縁距離を確保する電力用半導体装置を提供する。

【解決手段】ワイヤで接続された制御チップとパワーチップがモールド樹脂10により封止された電力用半導体装置100であって、パワーチップは、ワイヤがウエッジボンディングされた接合部と、接合部の近傍に設けられたバンプとをその表面上に有し、ワイヤは、バンプの上を通って延びる。

(もっと読む)

半導体装置

【課題】ボンディングパッドの下の絶縁膜にクラックが入ることをより防止する。

【解決手段】三層構造のボンディングパッドを有する半導体装置とし、この三層構造のボンディングパッドは、第一金属膜と、第二金属膜と、第三金属膜とからなり、第二金属膜は、第一金属膜及び第三金属膜のヤング率よりも高いヤング率を有するようにした。

(もっと読む)

ボンディングワイヤの接合構造及び接合方法

【課題】非貴金属を主成分とするボンディングワイヤを使用した接合の信頼性を向上できるボンディングワイヤの接合構造及び接合方法を提供する。

【解決手段】ボンディングワイヤ50の接合構造は、半導体素子10の電極10a上に形成されたバンプ上にボンディングワイヤを接合するボンディングワイヤの接合構造であって、ボンディングワイヤは、非貴金属を主成分とする芯材と、芯材を被覆する貴金属層とからなり、半導体素子の電極上に形成されたバンプ及びバンプ上にウエッジ接合されたボンディングワイヤが貴金属層を介して接合されていることを特徴とする。

(もっと読む)

半導体装置の配線構造及びその製造方法

【課題】第2メタル層が密着する絶縁層にクラックを生じさせ難い半導体装置の配線構造及びその製造方法を提供する。

【解決手段】半導体装置の配線構造は、絶縁層12と、絶縁層12によって覆われた第1メタル層13と、互いに間隔をあけて絶縁層12上に配列され且つ第1メタル層13より厚く形成された複数の電極部分101,102,…を有する第2メタル層14とを備え、絶縁層12の複数のビアホール内に配置された第1メタル層13と複数の電極部分101,102,…との間を繋ぐ複数の電極部分によって、複数の電極部分を第1メタル層13に電気的に接続する複数の貫通配線15を備えている。

(もっと読む)

半導体装置、及びその製造方法

【課題】ウェハテスト時に生じたプローブ痕を有する電極パッドに対してワイヤボンディングの接合が十分な強度で接合されたボンディングワイヤを備えた半導体装置、及びその製造方法を提供する。

【解決手段】電極パッド1を有する半導体チップと、一端に形成された圧着ボール3が電極パッド1に接合されたボンディングワイヤ10と、ボンディングワイヤ10の他端が接続された配線とを備える。ウェハテストにより電極パッド1に形成されたプローブ痕2の凹部底面2cに圧着ボール3が接合され、凹部底面2cと圧着ボール3との接合領域4の大きさが凹部底面2cの大きさと等しい、または小さい。

(もっと読む)

半導体チップおよび半導体装置

【課題】半導体チップを実装する際のコスト低減、パッケージ基板の小型化、および配線パターンの最適化を実現できる半導体チップを提供することである。

【解決手段】本発明にかかる半導体チップ10は、半導体チップ10に設けられると共に、少なくとも一つの電極パッド6を備える電極パッド群1と、半導体チップ10に設けられる少なくとも一つの電極パッドであって、電極パッド6から出力される信号と同じ信号を出力可能である電極パッド7を備える電極パッド群2と、を備える。そして第1の電極パッド群の一の電極パッドおよび第2の電極パッド群の一の電極パッドうち、当該信号が供給される他の半導体チップの他の電極パッドと距離が近い方の電極パッドが、他の半導体チップの当該他の電極パッドと接続される。

(もっと読む)

半導体装置および半導体装置製造方法

【課題】ボンディングワイヤーをより確実にボンディングパッドに接続すること。

【解決手段】配線6が形成される半導体チップ本体部分2と、ボンディングワイヤー22に接続されるボンディングパッド12と、半導体チップ本体部分2とボンディングパッド12との間に配置されるボンディングパッド下層絶縁体14と、配線6とボンディングパッド12とを接続する接続ビア16とを備えている。このような半導体装置によれば、ボンディングパッド12のうちのボンディングワイヤー22に接続される表面は、ボンディングパッド下層絶縁体14の分だけより高い位置に配置され、ワイヤーボンディングに利用されるキャピラリ21は、ボンディングパッド12と異なる他の部分11に接触することが防止される。このため、このような半導体装置は、ボンディングパッド12がより確実にボンディングワイヤー22に接続されることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線基板の一面を封止する封止体の配線基板の端縁部における剥離を防止し、信頼性を大幅に向上させると共に、更なる小型化を可能とした半導体装置を提供する。

【解決手段】配線基板2の一面には、複数のボンディングパッド6が端縁部に沿って並ぶボンディングパッド群6A,6Bと、一面を被覆する絶縁膜11とが設けられ、半導体チップ3の配線基板2と対向する面とは反対側の面には、複数のチップパッド13が端縁部に沿って並ぶチップパッド群13A,13Bが設けられ、ボンディングパッド6とチップパッド13との間がボンディングワイヤー14を介して電気的に接続され、絶縁膜11には、ボンディングパッド群6A,6Bを露出させる開口部12が設けられ、この開口部12は、配線基板2の端縁部に臨んで開口されると共に、配線基板2の端縁部に沿って並ぶボンディングパッド群6A,6Bの間で連続して開口されている。

(もっと読む)

半導体装置

【課題】半導体装置における多ピン化とコスト低減化を実現する。

【解決手段】マイコンチップ3と、マイコンチップ3の横に並べて配置され、かつマイコンチップ3より厚さが薄いSDRAM2と、タブ5cと、複数のインナリード5aおよびアウタリード5bと、マイコンチップ3のパッドとSDRAM2のパッドとを接続する第1のワイヤ6aと、マイコンチップ3の前記パッドとインナリード5aとを接続するとともに、SDRAM2を飛び越えて配置され、かつ第1のワイヤ6aのループより高い位置にループが形成された第2のワイヤ6bとからなり、メモリ用バスのインターフェイス回路を外部端子に接続せずにチップ間接続のみとしてパッケージ内で閉じるようにしたため、その分のピンを他の機能に活用でき、多ピン化を図ることができ、かつフレームタイプの採用によりSIP(半導体装置)1のコスト低減化を図る。

(もっと読む)

パワーデバイス

【課題】ポリイミド膜上に設けた電極パッドに導体バンプなしにAlワイヤを確実に接合でき、ポリイミド膜からの電極パッドの剥離や電極パッドとAlワイヤとの接合不良を防止できるパワーデバイスを提供する。

【解決手段】絶縁基板1上に設けられた半導体素子(2,3,6)と、絶縁基板1上に形成され、半導体素子(2,3,6)を覆う軟質ポリイミド膜11と、軟質ポリイミド膜11上に形成された電極パッド9と、電極パッド9にワイヤボンディングにより一端が接合されたAlワイヤ12とを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】プローブ跡を除去でき、かつ、製造コストが増加することを抑制できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】この半導体装置は、回路が形成された基板100と、この基板100上に形成され、表面に保護絶縁膜300が形成された多層配線層と、この多層配線層の最上層の配線層に位置し、上記回路に接続し、かつ、表面が保護絶縁膜と略同一面となっている電極パッド200と、を備える。また、このような半導体装置の製造方法は、回路が形成された基板100上に、この回路に接続し、かつ、保護絶縁膜300から突出した突出部201を有する電極パッド200を形成する工程と、プローブ端子500を電極パッド200に接触させることにより、回路の動作テストを行う工程と、突出部201の少なくとも表面を研磨する工程と、有する。

(もっと読む)

1 - 20 / 86

[ Back to top ]