Fターム[5F044EE02]の内容

ボンディング (23,044) | ボンディングパッド電極 (1,310) | パッドの配置 (187)

Fターム[5F044EE02]の下位に属するFターム

千鳥状 (23)

Fターム[5F044EE02]に分類される特許

1 - 20 / 164

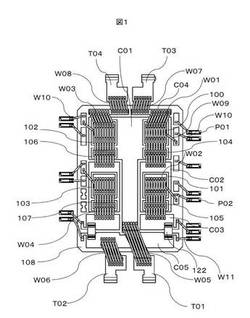

パワー半導体モジュール

【課題】単一のパワー半導体モジュールに例えば12アームを搭載可能にコンパクトに実装するとともに、直流端子と交流端子のそれぞれの端子をモジュール端面にそれぞれ配置し、また、電力回路のインダクタンスを低く保つこと。

【解決手段】1枚の絶縁基板108上に2組の上アーム(100,104と102,106)を絶縁基板上の上寄り左右に配置し、2組の下アーム(101,105と103,107)を絶縁基板上の下寄り左右に配置して、絶縁基板上の配線パターンとして、2組の上アームを第1の配線パターンC01上に実装し、2組の下アームは第1の配線パターンの下に配置した第2、第3の配線パターンC02,C02上にそれぞれ実装して、第2、第3の配線パターンの間に第1の配線パターンC01を延長し、その延長した端部に正極端子T01からの配線を接続し、さらに、絶縁基板108を1モジュール中に3枚並置して実装して12in1モジュールの構成とすること。

(もっと読む)

半導体装置

【課題】半導体装置の最上層の保護膜のクラックを防いで、半導体装置の信頼性の向上を図ることのできる技術を提供する。

【解決手段】ボンディングパッドBP1を長方形状とし、ボンディングパッドBP1のワイヤボンディング領域BP1wでの保護膜5の重なり幅を、ボンディングパッドBP1のプローブ領域BP1pでの保護膜5の重なり幅よりも広くなるように、ボンディングパッドBP1上の保護膜5に開口部6を形成する。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

配線基板の製造方法

【課題】ボンディングパッドの変色の発生を抑制することのできる配線基板の製造方法を提供する。

【解決手段】樹脂基板10の上面にフリップチップ接続用の接続パッド13となる第1パッド13Aと、ボンディングパッド14となる第2パッド14Aとを形成し、第2パッド14Aの表面にめっき14Bを形成し、第1パッド13Aの表面にのみ選択的に粘着層15を被着する。続いて、粘着層15にはんだ粉16を付着し、樹脂基板10の上面全面にハロゲン濃度が0.15wt%以下のフラックス40を塗布し、はんだ粉16をリフローにより溶融して第1パッド13Aにはんだ13Bを被着する。

(もっと読む)

半導体装置、半導体装置の設計方法、半導体装置設計装置、及びプログラム

【課題】より多くのI/Oセルを配置することができるようにする。

【解決手段】多層配線層には、電位供給用接続配線230が設けられている。電位供給用接続配線230は、平面視で外周セル列20を構成するI/Oセル200のいずれか、および内周セル列30を構成するI/Oセル200のいずれかと重なっている。そして電位供給用接続配線230は、外周セル列20の下方に位置する電源電位供給配線222を、内周セル列30の下方に位置する電源電位供給配線222に接続するとともに、外周セル列20の下方に位置する接地電位供給配線224を、内周セル列30の下方に位置する接地電位供給配線224に接続している。

(もっと読む)

半導体装置

【課題】半導体チップを実装するパッケージ基板における、半導体チップを囲む最内周のリング状領域に、電源用導体およびグラウンド用導体を設けても、半導体装置全体としてはサイズおよび製造コストが増大しない手段を提供する。

【解決手段】半導体チップ10における最外周のリング状領域に、電源用パッド11およびグラウンド用パッド12を集める。半導体チップを実装するパッケージ基板における、半導体チップを囲む最内周のリング状領域に、電源用端子21およびグラウンド用端子22を集める。こうすることで、半導体装置全体としてのサイズおよび製造コストを縮小することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の組み立てにおけるボイドの発生を抑制する。

【解決手段】一対の第1辺3aa,3ab及び一対の第2辺3ac,3adを有する四角形からなるダイパッド3aにMCUチップ1とAFEチップ2を搭載し、MCUチップ1及びAFEチップ2にワイヤボンディングを行った後、2つの第2辺3ac,3adのうちの一方の第2辺3ac側から他方の第2辺3ad側に向かって樹脂を供給し、前記樹脂をMCUチップ1上の第1パッド群1ccと第2パッド群1cdとの間の開口に通してチップ間を充填することで、チップ間の領域におけるボイドの発生を抑制する。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体装置

【課題】兼用パッドのサイズを専用パッドよりも大きくするとともに、半導体装置のサイズ増大を抑制する。

【解決手段】半導体装置は、第1の方向に延伸された第1のエッジE1と、第1の方向と実質的に直交する第2の方向に延伸された第2のエッジE2とを含む半導体チップ10と、半導体チップ上に形成され、互いに第2の方向に沿った長さが実質的に等しい複数の第1グループパッドGP1と、半導体チップ上に形成され、第2の方向に沿った長さが、複数の第1グループパッドの第2の方向に沿った長さよりも長い、第2グループパッドGP2と、を備える。複数の第1グループパッドと第2グループパッドとは、第2グループパッドと第2のエッジとの間に複数の第1グループパッドのいずれをも含まずに、第1の方向に沿って一列に並んで配置されている。

(もっと読む)

半導体装置

【課題】ワイヤボンディングにおいて、隣接する電極パッド間でショートさせることなく、電極パッドを狭ピッチ化した半導体装置を提供する。

【解決手段】この半導体装置100は、複数の電極パッド(第一電極パッド420、第二電極パッド440)と、ボンディングワイヤ600と、を備える。また、ボンディングワイヤ600は、第一電極パッド420と第二電極パッド440にボンディングされている。このとき、隣接する第一電極パッド420と第二電極パッド440は、上面の高さが交互に異なるように形成されている。また、第一電極パッド420と第二電極パッド440との間の段差部のうち、側面の少なくとも表面は、絶縁膜(保護絶縁膜260または保護絶縁膜500)で形成されている。

(もっと読む)

半導体チップおよび半導体装置

【課題】半導体チップを実装する際のコスト低減、パッケージ基板の小型化、および配線パターンの最適化を実現できる半導体チップを提供することである。

【解決手段】本発明にかかる半導体チップ10は、半導体チップ10に設けられると共に、少なくとも一つの電極パッド6を備える電極パッド群1と、半導体チップ10に設けられる少なくとも一つの電極パッドであって、電極パッド6から出力される信号と同じ信号を出力可能である電極パッド7を備える電極パッド群2と、を備える。そして第1の電極パッド群の一の電極パッドおよび第2の電極パッド群の一の電極パッドうち、当該信号が供給される他の半導体チップの他の電極パッドと距離が近い方の電極パッドが、他の半導体チップの当該他の電極パッドと接続される。

(もっと読む)

半導体装置及び半導体装置を搭載したプリント基板

【課題】個々のインナーリード間の容量カップリング、及び相互インダクタンス干渉によって、内部回路が動作する際に生じる電源電圧変動の高周波成分がノイズとして他のインナーリードに伝播することを抑制するとともに、ノイズからの輻射を抑制可能な安価な半導体装置及び半導体装置を搭載したプリント基板を提供する

【解決手段】半導体装置は、外部と信号をやり取りする入出力回路と、演算処理を行う内部回路Eとを備え、本体が矩形形状を有する半導体チップ7と、半導体チップの各辺にそれぞれ設けられた複数の接続端子と、複数の接続端子のうち、1つの辺の一端からN番目(Nは、1<=N<=4の自然数)の接続端子に接続される内部回路用の電源ラインと、複数の接続端子のうち、1つの辺の一端からN+M番目(Mは、1<=M<=4の自然数)の接続端子に接続される内部回路用のグランドラインとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】配線基板の一面を封止する封止体の配線基板の端縁部における剥離を防止し、信頼性を大幅に向上させると共に、更なる小型化を可能とした半導体装置を提供する。

【解決手段】配線基板2の一面には、複数のボンディングパッド6が端縁部に沿って並ぶボンディングパッド群6A,6Bと、一面を被覆する絶縁膜11とが設けられ、半導体チップ3の配線基板2と対向する面とは反対側の面には、複数のチップパッド13が端縁部に沿って並ぶチップパッド群13A,13Bが設けられ、ボンディングパッド6とチップパッド13との間がボンディングワイヤー14を介して電気的に接続され、絶縁膜11には、ボンディングパッド群6A,6Bを露出させる開口部12が設けられ、この開口部12は、配線基板2の端縁部に臨んで開口されると共に、配線基板2の端縁部に沿って並ぶボンディングパッド群6A,6Bの間で連続して開口されている。

(もっと読む)

半導体集積回路装置

【課題】入力回路ブロックの入力配線と出力回路ブロックの出力配線を短くする。

【解決手段】半導体集積回路装置30において、入力回路ブロック32用の外部接続用電極P2及びP3は、入力回路ブロック32と出力回路ブロック33との間に複数配置されており、出力回路ブロック33用の外部接続用電極P1及びP4は、出力回路ブロック33とリード電極34及び35との間に複数配置されており、金属細線Wb1及びWb2を介して外部接続用電極P1及びP2に接続されるリード電極34と、金属細線Wb3及びWb4を介して外部接続用電極P3及びP4に接続されるリード電極35は、いずれも、入力回路ブロック32、外部接続用電極P2及びP3、出力回路ブロック33、外部接続用電極P1及びP4、リード電極34及び35の順に配置された方向と平行する方向に複数配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】回路規模の大きな半導体チップを用いる場合においても、チップ中央部に安定して電源電圧を供給できる半導体装置を低コストに実現する。

【解決手段】半導体装置25は、半導体チップ4と、半導体チップ4の主面の周縁部上に形成された外部パッド7と、主面上であって、外部パッド7よりも内側に形成された複数の内部パッド8及び9と、主面上を覆い、外部パッド7上及び複数の内部パッド8及び9上に開口を有する保護膜6と、内部パッド同士を電気的に接続する第1の金属細線16とを備える。複数の内部パッド8及び9は、外部パッド7よりも小さい。

(もっと読む)

半導体素子

【課題】高周波特性を損なうことなく、チップ単体又はウェハレベルでプローブ検査を可能とする半導体素子を提供する。

【解決手段】EAM領域12に電界を印加又は電流を注入するEAM部電極14と、EAM部電極14と接続されたワイヤボンディング用のパッド電極15とを有するEAM付き半導体レーザにおいて、パッド電極15を複数のメッシュ穴16を有するメッシュ形状に形成した。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の生産性を向上させる。

【解決手段】複数の第1電極11、第2電極12が設けられたプリント基板10と、プリント基板10上に搭載され、上面の外周に沿った第1列L1をなす複数の第1接続パッド21及び第1列L1と平行かつ第1列L1よりも内側に離間した第2列L2をなす複数の第2接続パッド22が設けられた半導体チップ20と、第1電極11、第2電極12と第1接続パッド21、第2接続パッド22とを接続する第1ボンディングワイヤ31、第2ボンディングワイヤ32とを備え、半導体チップ20の電源電圧端子、システムリセット端子は、第1接続パッド21のいずれかが用いられ、複数の第2接続パッド22と接続される第2ボンディングワイヤ32は、複数の第1接続パッド21と接続される第1ボンディングワイヤ31よりも上方に設けられている。

(もっと読む)

半導体装置

【課題】チップサイズの縮小化や多ビット化に対応した半導体装置を提供する。

【解決手段】第1及び第2チップパッド列4A,4Bの端部よりも外側に位置する第3チップパッド列4Cが、第1チップパッド列4Aと第2チップパッド列4Bとの間の中心線の延長線上に並んで配置されている。これにより、第3チップパッド列4Cを構成するチップパッド4は、第1及び第2チップパッド列4A,4Bを構成するチップパッド4よりも、第1又は第2ボンディングパッド列6A,6Bを構成するボンディングパッド6に対するY方向の距離を大きく確保することができる。したがって、これらチップパッド4とボンディングパッド6との間を接続するボンディングワイヤー7のY方向に対する角度を緩和することが可能である。

(もっと読む)

半導体チップ及び半導体装置

【課題】ボンディングに用いるパッド全体のレイアウトで必要な面積の増大を抑制できる半導体チップ及び半導体装置を提供する。

【解決手段】半導体チップに、ボンディング用のパッドであるボンディングパッドとテスト用のパッドであるプローブパッドとを含む複数のパッド形成部を備える。パッド形成部はボンディングパッドとプローブパッドの配列方向と直交する方向に2列で配置される。ボンディングパッドとプローブパッドとは、パッド形成部の列方向において、互いの位置が順次入れ替わるように配置される。

(もっと読む)

半導体チップ及び半導体装置

【課題】半導体チップの小型化を妨げず、集積度を低下させずに、Alワイヤによるボンディングが可能な半導体チップ及び半導体装置を提供する。

【解決手段】プリント基板10と、プリント基板10上に搭載され、上面の外周に沿った第1の列L1をなす複数の第1の接続パッド21、及び、第1の列L1と平行かつ第1の列L1よりも内側に離間した第2の列L2をなす複数の第2の接続パッド22が設けられた半導体チップ20と、プリント基板10と半導体チップ20とを接続する第1のボンディングワイヤ31、第2のボンディングワイヤ32とを備える半導体装置1である。第1の列L1をなす第1の接続パッド21と第2の列L2をなす第2の接続パッド22との間には回路素子23、24が設けられている。

(もっと読む)

1 - 20 / 164

[ Back to top ]