Fターム[5F044EE03]の内容

ボンディング (23,044) | ボンディングパッド電極 (1,310) | パッドの配置 (187) | 千鳥状 (23)

Fターム[5F044EE03]に分類される特許

1 - 20 / 23

半導体装置

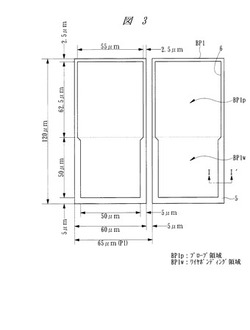

【課題】半導体装置の最上層の保護膜のクラックを防いで、半導体装置の信頼性の向上を図ることのできる技術を提供する。

【解決手段】ボンディングパッドBP1を長方形状とし、ボンディングパッドBP1のワイヤボンディング領域BP1wでの保護膜5の重なり幅を、ボンディングパッドBP1のプローブ領域BP1pでの保護膜5の重なり幅よりも広くなるように、ボンディングパッドBP1上の保護膜5に開口部6を形成する。

(もっと読む)

電子装置及びその製造方法並びに画像形成装置

【課題】小型化及び低コスト化を図りつつ、導電ワイヤとの干渉を回避しながら、溝の底面に形成されたパッドと溝の外側周辺部の上面に形成されたパッドとをワイヤボンディングにより接続することができる電子装置を提供する。

【解決手段】電子装置100は、互いに対向する2つの壁面107、108からなる溝102が形成され、溝102の外側周辺部の上面側に第1のパッド104が設けられ、溝102の底面側に第2のパッド105が設けられ、ワイヤボンディングにより第1のパッド104と第2のパッド105とが接続されている。溝の102の底面に垂直な方向から見た場合における溝102の2つの壁面107、108のうち第1のパッド104により近い一方の壁面107の上端から第2のパッド105までの距離(LW)109よりも、もう一方の壁面108の上端から第2のパッド105までの距離(LN)110が短くなるように構成されている。

(もっと読む)

半導体パッケージ

【課題】ボンディングワイヤのループインダクタンスを低減した半導体パッケージを提供する。

【解決手段】所定の方向に交互に配置された信号用パッドおよび補助パッドのそれぞれが複数設けられた半導体装置と、信号用ボンドフィンガー、電源電圧用ボンドフィンガーおよび接地電位用ボンドフィンガーのそれぞれが複数設けられたパッケージ基板と、を有する。複数の信号用パッドのそれぞれが複数の信号用ボンドフィンガーのそれぞれと第1のワイヤを介して接続され、複数の電源電圧用ボンドフィンガーおよび複数の接地電位用ボンドフィンガーのそれぞれが複数の補助パッドのそれぞれと第2のワイヤを介して接続されている。第1のワイヤが、電源電圧用ボンドフィンガーに接続された第2のワイヤと接地電位用ボンドフィンガーに接続された第2のワイヤとの間に配置されている。

(もっと読む)

半導体チップ及び半導体装置

【課題】半導体チップの小型化を妨げず、集積度を低下させずに、Alワイヤによるボンディングが可能な半導体チップ及び半導体装置を提供する。

【解決手段】プリント基板10と、プリント基板10上に搭載され、上面の外周に沿った第1の列L1をなす複数の第1の接続パッド21、及び、第1の列L1と平行かつ第1の列L1よりも内側に離間した第2の列L2をなす複数の第2の接続パッド22が設けられた半導体チップ20と、プリント基板10と半導体チップ20とを接続する第1のボンディングワイヤ31、第2のボンディングワイヤ32とを備える半導体装置1である。第1の列L1をなす第1の接続パッド21と第2の列L2をなす第2の接続パッド22との間には回路素子23、24が設けられている。

(もっと読む)

半導体パッケージ

【課題】現実的な実装方法で寄生インダクタンスを低減する手段を提供する。

【解決手段】半導体パッケージ1表層には、ワイヤボンディングの接続点である該半導体パッケージ表層上で突出する複数の櫛歯状グラウンドパッド31を有するグラウンドパッドを設ける。櫛歯状グラウンドパッドの間には、電源パッド25を配置する。

1つの櫛歯状グラウンドパッド31には長短二本のグラウンドワイヤが配される。また、1つの電源パッド25には長短二本の電源ワイヤが配される。

長いグラウンドワイヤ12−2と長い電源ワイヤ11−2、短い電源ワイヤ11−1と短いグラウンドワイヤ12−1を平行かつ近接するように配置することで寄生インダクタンスを低減する。

(もっと読む)

半導体装置及びそのワイヤーボンディング方法

【課題】キャピラリーとワイヤーとの干渉・接触を避けながらボンディングパッドとフィンガーが接合される半導体素子及びそのワイヤーボンディング方法を提供すること。

【解決手段】半導体素子10は、ボンディングパッド12を備えた矩形の半導体チップ14とフィンガー16を備えた矩形のリードフレームよりなる。ワイヤー20により、それぞれのボンディングパッド12とそれぞれのフィンガー16は接合される。ワイヤーは、比較的短い第1のワイヤー群20と、比較的長い第2のワイヤー群(図示せず)に振り分けられる。第1のワイヤー群20のボンディングパッド側接合点は、半導体チップ14の外縁に近い位置に、第2のワイヤー群のボンディングパッド側接合点は、半導体チップ14の外縁から離れた位置にずれている。これにより、先行形成されたワイヤーとキャピラリーの干渉を避けることができる。

(もっと読む)

電子装置、画像形成装置、および画像入力装置

【課題】導通信頼性の高い電子装置、およびそれを用いた、画像形成装置並びに画像入力装置を提供する。

【解決手段】電子装置は、基板102と、基板102の一表面上に形成された電子素子103と、電子素子103が形成された領域とは異なる領域に、所定間隔をあけて列状に配列され、第一の接続配線104を介して電子素子103と電気的に接続された、第一のパッド106と、電子素子103が形成された領域および第一のパッド106が形成された領域とは異なる領域に設けられ、第一のパッド106間を横切る第二の接続配線105を介して電子素子103と電気的に接続された、第二のパッド107と、を具備しており、第一のパッド106間において、第二の接続配線105の基板102とは反対側の表面が、第一のパッド106の基板102とは反対側の表面よりも基板102側に位置している。

(もっと読む)

半導体集積回路

【課題】半導体集積回路におけるパッドの配置の自由度を増加させること。

【解決手段】本発明の一態様に係る半導体集積回路は、半導体チップ100に形成されたI/Oバッファ102と、単層パッド103と、多層パッド104とを備える。単層パッド103は、I/Oバッファ102上に形成されている。多層パッド104は、I/Oバッファ102上に形成され、単層パッド103と分離して設けられている。単層パッド103はボンディング専用のパッドであり、多層パッド104はプロービングとボンディングが行われるパッドである。

(もっと読む)

半導体集積回路装置

【課題】プローブ検査においては、パッド上のプローブ痕を確認する工程が必要となる。しかし、ウェハ状態でプローブ検査を実施した後に、ボンディング・パッドにワイヤ・ボンディングするため、パッド上にプローブ痕がある状態でワイヤ・ボンディングする。プローブ痕がある場所にボンディングすることは、プローブ痕がない場所にボンディングした場合に比べてボンディング強度を弱めてしまう。

【解決手段】本願発明は、半導体チップの辺に沿ってボンディング・パッドを配置するに当たり、直線状に配置された実ボンディング・パッド列の各実ボンディング・パッド上の実ボンディング・パッド列の中心線に関して交互に垂直方向にずれて形成されたプローブ痕の内、一方の側へずれたプローブ痕の回帰直線上に、ほぼ、その中心が来るように配置され、実ボンディング・パッドよりも面積が小さいダミー・パッドを配置するものである。

(もっと読む)

半導体装置及び検査方法

【課題】半導体装置のワイヤ流れによる不具合の発生を防止することが可能な技術を提供すること。

【解決手段】本発明の一態様に係る半導体装置10は、半導体チップ11に設けられた回路ブロック12と、回路ブロック12上に設けられた接続パッド15(1br)と、接続パッド15(1br)と電気的に接続され、ボンディングされるボンディングパッド17(1)とを備え、回路ブロック12は、接続パッド15(1br)を介してボンディングパッド17(1)と接続される。

(もっと読む)

半導体装置

【課題】ユーザの要求に出来る限り対応しつつも、チップサイズを増大させないようにすることが重要となる。

【解決手段】本発明の半導体装置は、基板上の外周に沿って配置される第1乃至第4内部端子と、第1内部端子に接続される回路と、第2内部端子と接続される第1外部端子と、第3内部端子と接続される第2外部端子と、第4内部端子と接続される第3外部端子と、を備え、回路は、第1内部端子と第1外部端子との接続状態に応じた信号を出力し、第1及び第2内部端子は、第1外部端子が対応する基板の1辺に平行な方向における第1及び第2内部端子の中心間の距離がL1となるように配置され、第3及び第4内部端子は、第2及び第3外部端子が対応する基板の1辺に平行な方向における第3及び第4内部端子の中心間の距離がL2となるように配置され、距離L1は、距離L2よりも小さいことを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】列状に配置された複数の電極パッド20paと、電極パッド20paの夫々に電気的に接続され、電極パッド20paの列より外側に位置する、列状に配置された複数の試験パッド20taと、を有する半導体素子20と、半導体素子20を搭載し、半導体素子20の搭載領域以外に、複数の電極端子10aを列状に配置した配線基板10と、を備え、全ての試験パッド20taが、電極端子10aと電極パッド20taとを電気的に接続するボンディングワイヤ40aの下に位置している半導体装置が提供される。当該半導体装置1aによれば、ボンディングワイヤ40a自体の変形によってもたらされる、半導体素子20の電極パッド20pa,20pb間の短絡を解除し、半導体装置の製造歩留りを高め、より高い信頼性を有する半導体装置を提供することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置を小型化できる技術を提供する。

【解決手段】配線基板2上に搭載された半導体チップ5の電極15と配線基板2の接続端子25a,25b,25cとの間をボンディングワイヤ7a,7bで接続し、樹脂封止して半導体装置が形成されている。配線基板2の上面において、接続端子25a,25b,25cは半導体チップ5の辺5bに沿って3列に配置されている。3列のうち、半導体チップ5の辺5bに最も近い1列目の接続端子25aには、ループ高さが低いボンディングワイヤ7aが接続され、半導体チップ5の辺5bから最も遠い3列目の接続端子25cには、ループ高さが高いボンディングワイヤ7bが接続され、2列目の接続端子25bには、ボンディングワイヤ7aまたはボンディングワイヤ7bが接続されている。

(もっと読む)

半導体装置および当該半導体装置の製造方法

【課題】高周波特性を重視する回路に接続される電極パッドの寄生容量の増大を抑える。

【解決手段】半導体チップ100は、複数の内部回路と、外縁近傍に設けられ、それぞれ複数の内部回路のいずれかに電気的に接続された複数の電極パッドとを含む。複数の電極パッドは、プローブが接するためのプローブ用領域104と、プローブ用領域104とは異なる位置に設けられ、ワイヤ108をボンディングするためのボンディング用領域とを含む長パッド102と、ボンディング用領域を含むがプローブ用領域を含まない構成とすることにより長パッド102よりもパッド面積が小さく形成された高周波信号を入出力する高周波用の小パッド110とを含む。

(もっと読む)

半導体装置

【課題】単位面積あたりに配置可能な電極パッド数を減らすことなく、プローブ検査により生じるクラックの影響を抑制し、信頼性を向上させた半導体装置を提供する。

【解決手段】電極パッド21内にプローブコンタクト可能なプローブ領域32と非プローブ領域31を設ける。2列以上の千鳥状に配置された電極パッド21において、異なる電極パッド21と内部回路とを接続する引き出し配線52を、プローブ領域32の直下に配置せず、非プローブ領域31の直下に配置する。

(もっと読む)

ボンディングパッド配置方法

【課題】シグナルパッドおよびリングパッドを半導体パッケージの基板面上において偏りのないように配置する設計処理を演算処理装置により効率的に実行するボンディングパッド配置方法を実現する。

【解決手段】半導体パッケージの基板面上におけるシグナルパッドもしくはリングパッドの位置を半導体パッケージの基板面上に相当する仮想平面上において設計する配置処理を、演算処理装置により実行するボンディングパッド配置方法は、仮想平面上の位置を決定すべき位置決定対象シグナルパッドが、設計データにより規定された配置順に従って位置決定対象シグナルパッドよりも1つ先に既に仮想平面上の位置を決定した位置決定済シグナルパッドとは設計データの規定上異なる列に属するか否かを判定する判定ステップS100と、判定ステップS100の判定結果に基づき、位置決定対象シグナルパッドの仮想平面上の位置を決定する決定ステップS200と、を備える。

(もっと読む)

半導体装置

【課題】パッケージ配線の接続直後や熱衝撃試験時などで半導体装置の温度が変化する際において半導体装置を構成する各部材やパッケージ配線に互いにかかる応力を低減することが可能な半導体装置を提供することを目的とする。

【解決手段】複数の半導体素子が形成される半導体基板34上に設けられる金属配線35とパッケージ配線31とが金属パッド36を介して電気的に接続される半導体装置1において、その金属パッド36を分割する。

(もっと読む)

半導体装置

【課題】多数回のプロービング検査を行っても問題の生じる懸念を解消した狭パッドの配置を実現する。

【解決手段】半導体チップのパッドがプロービングパッド専用パッド、プロービングとボンディングの兼用パッド、ボンディング専用パッドに区別されている。プロービング用に用いられるパッドはボンディング専用パッドよりも半導体チップの周辺部に配置される。これにより、半導体チップの周辺部に設けられたプロービング専用パッド及び兼用パッドに対してプロービングを行えば足りるようになり、ボンディング専用パッドは入出力バッファ上等に配置しても、多数回のプロービングに対しても不都合が生じる懸念が解消される。

(もっと読む)

半導体集積回路

【課題】コア領域への電源供給のための接続パッド不足を防止し、IOセルのセル幅を小さくする必要を無くし、全ての接続パッドに同一接続方法が適用できるようにする。

【解決手段】IO領域30のIOセル31a〜31g上に接続パッド41a〜41cの列と接続パッド42a〜42dの列をずらせて配置し、コア領域20の一辺に沿うコア電源配線21上に接続パッド43a〜43dを配置し、接続パッド41a〜41c,42a〜42d,43a〜43dのそれぞれのパッドピッチPをIOセルのセルピッチSに対してP=2Sとし、且つ接続パッド41a〜41c,42a〜42d,43a〜43d全体のパッドピッチをP/3(=2S/3)として、2個のIOセル当り3個の接続パッドを配置する。

(もっと読む)

半導体装置

【課題】 必要な面積を持ったパッドの領域を確保しつつ、チップ面積のオーバヘッドを解消する工夫が施された半導体装置を提供する。

【解決手段】 半導体装置1の中央部に設けられ、内部回路が形成された内部回路領域11と、長方形状の一方の短辺が内部回路領域11の各辺と対向して順次並んで設けられた、半導体装置1の外部との間で信号の入出力を担う複数の入出力セル12と、半導体装置1の外部との間でワイヤにより電気的に接続されるワイヤボンディング部14と動作確認用のプローブ針が当てられるプローブ部15とを有し、前記入出力セル12上に重なり、かつ各入出力セル12の長辺に対して長辺が垂直に交わるように千鳥配列された複数のパッドとを備える。

(もっと読む)

1 - 20 / 23

[ Back to top ]