Fターム[5F045AB01]の内容

気相成長(金属層を除く) (114,827) | 成長層の組成 (12,584) | 4族 (3,529)

Fターム[5F045AB01]の下位に属するFターム

Fターム[5F045AB01]に分類される特許

201 - 220 / 241

ヘキサクロロジシラン又はその他の塩素含有シリコン前駆体を用いた微小造形物充填方法及び装置

処理システム内で低圧堆積プロセスによって基板上の微小造形物内にシリコン含有膜を堆積する方法が提供される。シリコン含有膜は、基板を処理システムの処理チャンバー内に設置し、基板をヘキサクロロジシラン(HCD)処理ガスに晒すことによって、微小造形物内に形成されることができる。また、例えばHCD処理ガス等の、シリコン及び塩素を含有するガスを用いて微小造形物内にシリコン含有膜を形成する処理システムを有する処理ツールが提供される。代替的に、微小造形物は、DCS、SiCl4及びSiHCl3ガスに晒されてもよい。さらに代替的に、微小造形物は、(SiH4+HCl)に晒されてもよい。  (もっと読む)

(もっと読む)

シリコン−ゲルマニウム層を備えた半導体ウェハ及びその製造方法

【課題】勾配シリコン−ゲルマニウム層中の転位密度を低下させること

【解決手段】単結晶シリコン層と、前記層に接する、Si1−xGex組成(その際、xはゲルマニウムの物質量割合を表し、かつxは0<x≦1の条件が通用し、かつxは単結晶シリコン層からの距離aの増大と共により大きな値をとる)を有する厚さdの勾配シリコン−ゲルマニウム層とを有する半導体ウェハにおいて、勾配シリコン−ゲルマニウム層の表面上でのゲルマニウムの物質量割合x(d)と、単結晶シリコン層と前記勾配シリコン−ゲルマニウム層の表面との間の距離の中心でのゲルマニウムの物質量割合x(d/2)との間に、次の関係式x(d/2)>0.5・x(d)が成り立つことを特徴とする、半導体ウェハ。

(もっと読む)

基板処理装置

【課題】

基板処理装置の高さを増大させることなく、排気コンダクタンスを増大させ、処理室の圧力を低下させて基板に対する処理が行える様にする。

【解決手段】

基板50を収容し、該基板上に所望の膜を生成する処理室85と、該処理室に所望のガスを供給するガス供給手段と、前記処理室と開口54を介して気密に連設する気密室43と、該気密室に直接取付けられる排気装置59とを具備し、前記処理室の雰囲気を前記排気装置により排気する様にした。

(もっと読む)

半導体装置およびその製造方法

【課題】 p型チャネルを有する半導体装置において、前記p型チャネル領域に一軸性圧縮応力をSiGe混晶層より印加して、前記チャネル領域におけるホール移動度を向上させる。

【解決手段】 シリコン基板中、ソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層によりエピタキシャルに充填する際に、前記トレンチの側壁面を複数のファセットにより画成し、さらにSiGe混晶層中のGe原子濃度を20%を超えて増大させる。

(もっと読む)

基板処理装置及び半導体デバイスの製造方法

本発明は、Ge含有ガスを供給してEpi−SiGe等の成膜処理をする場合に、基板界面の酸素濃度上昇を抑え、良好な膜を形成することができる基板処理装置を提供することを課題としている。

基板に成膜処理をする際に、ステップS18においてEpi−SiGe成膜処理を行う前に、ステップS13においてSiコーティング処理を行う。 これにより基板支持体に付着したGeO等の酸化物をコーティングで封じ込めることができ、GeOから脱離した酸素がEpi−SiGe膜のSi基板との界面に取り込まれるのを防止することができる。  (もっと読む)

(もっと読む)

歪みシリコンウェーハの製造方法

【課題】SiGe層を有する歪みシリコンウェーハにおいて、SiGe層上に形成される歪みSi層における貫通転位密度の一層の低減化を図ることができる歪みシリコンウェーハの製造方法を提供する。

【解決手段】単結晶シリコン基板上にGe濃度を上げながら組成傾斜SiGe層(Si1−xGex層のGe濃度比xが0<x≦0.5)を厚さ0.1〜3μmにエピタキシャル形成し、その上に厚さ0.1〜1μmのGe組成比が一定である歪み緩和Si1−xGex層を形成し、更に、厚さ5〜30nmの第1歪みSi層を形成し、その上に第2歪みSi層として、第1歪みSi層の成膜温度より低い温度で厚さ10nm以下の歪みSi層をエピタキシャル成長させる。

(もっと読む)

ひずみヘテロ接合構造体の製造

【課題】本発明は、ひずみへテロ接合構造体の製造を提供する。

【解決手段】多層膜の成長は、成長された層のひずみの厳密な制御及び成長された膜の完全な剥離を可能にする方法で行なわれて選択された基板への剥離された多層構造体の取付けを可能にする。シリコン−ゲルマニウムのような材料の層が、テンプレート層がその上に形成される犠牲層を有する基板の、シリコンのようなテンプレート層の上に成長される。成長層は、テンプレート層と格子不一致を有して堆積されるときに成長層がひずまされる。シリコンのような、結晶材料の最上層は、成長層及びテンプレート層を有する多層構造体を形成するために合金層の上に成長される。犠牲層は、多層構造体を犠牲層から剥離するために優先的にエッチングされて、成長層を緩和し且つ成長層と連結される結晶層をひずませる。

(もっと読む)

半導体基板上にエピタキシャル層を形成する方法およびこの方法によって形成するデバイス

本発明は、エピタキシャル層の製造に関し、半導体基板を用立てるステップと、第1の深さを有するSi−Ge層を半導体基板上に設けるステップと、第1の深さよりも十分に深い第2の深さを有し、かつ、n型のドーパント材料でドープした層を、半導体基板に設けるステップと、Ge原子およびn型原子が、二酸化シリコン/シリコン界面にて二酸化シリコンによって半導体基板内へ押し込まれるように、二酸化シリコン層を形成すべく酸化処理を行うステップであって、n型原子が、Ge原子よりも深く半導体基板内に押し込まれて、その結果頂部層のn型原子の濃度を低減させるようにするステップと、二酸化シリコン層を取り除くステップと、半導体基板上にシリコンのエピタキシャル層を、外方拡散またはオートドーピングを低減させて成長させるステップとを含む。  (もっと読む)

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】 ヘテロエピタキシャル成長膜の、応力の緩和と、緩和に伴って発生し表面へ貫通する結晶欠陥の密度の抑制を両立させるために要求される、膜厚に対する制限を低減し、プロセス設計の自由度を向上させる。

【解決手段】 単結晶半導体基板10の上に単結晶半導体基板10とは格子定数及び/又は熱膨張率が異なる第1単結晶半導体層12を成長させた後に、水素を含む還元性雰囲気中で熱処理することにより、第1単結晶半導体層12の表面は平坦化され、結晶欠陥は単結晶半導体基板10との界面近傍の領域14に局在化され、表面近傍の領域16に加わる応力は緩和される。この熱処理工程の後に実施される第2成長工程において、下地となる第1単結晶半導体層12はその応力が緩和されているので、第1単結晶半導体層12とは格子定数及び/又は熱膨張率が異なる第2単結晶半導体層18に応力が加わり、良質な歪み半導体基板を得ることができる。

(もっと読む)

交互ガス供給による選択的エピタキシープロセス

一実施形態において、基板表面上にシリコン含有材料をエピタキシャル形成する方法であって、単結晶表面及び第2表面(アモルファス又は多結晶)を有する基板をプロセスチャンバー内に位置させるステップと、基板を、堆積ガスに露出されて、単結晶表面にエピタキシャル層を形成すると共に、第2表面に多結晶層を形成するステップとを備えた方法が提供される。堆積ガスは、シリコンソースと、少なくとも第2の元素ソース、例えば、ゲルマニウムソース、炭素ソース又はその両方とを含むのが好ましい。その後、この方法は、更に、基板をエッチング剤ガスに露出させて、多結晶層がエピタキシャル層より速い速度でエッチングされるようにするステップも備えている。基板は、堆積ガス及びエッチング剤ガスに順次に繰り返し露出されて、シリコン含有材料を形成する。一実施例において、堆積ガスはシランを含み、エッチング剤ガスは塩素及び窒素を含む。 (もっと読む)

シリコン化合物によるシリコン含有層の堆積

本発明の実施形態は、一般的には、シリコン化合物の合成物及びシリコン含有膜を堆積させるためにシリコン化合物を用いる方法を提供する。本方法は、シリコン化合物を基板表面に導入するステップとシリコン化合物の一部、シリコンモチーフをシリコン含有膜として堆積させるステップとを用いる。リガンドはシリコン化合物の他の部分であり、インサイチュエッチング剤として遊離する。インサイチュエッチング剤は、選択的シリコンエピタキシーの成長を支持する。シリコン化合物は、SiRX6、Si2RX6、Si2RX8(ここで、Xは独立して水素又はハロゲンであり、Rはカーボン、シリコン又はゲルマニウムである。)を含んでいる。シリコン化合物は、また、3つのシリコン原子と、4つのカーボン、シリコン又はゲルマニウム原子と、水素又はハロゲンと少なくとも1つのハロゲン原子とを含む化合物、また、4つのシリコン原子と、5つのカーボンと、シリコン又はゲルマニウム原子と、水素又はハロゲンと少なくとも1つのハロゲン原子とを含む化合物を含んでいる。 (もっと読む)

シリコンエピタキシャル膜形成時のCl2および/またはHClの使用

第1の態様では、基板にエピタキシャル膜を形成するための第1の方法が提供される。該第1の方法は(a)基板を提供するステップと、(b)該基板の少なくとも一部にエピタキシャル膜を形成するために少なくともシリコンソースに該基板を暴露するステップと、(c)ステップ(b)中に形成された該エピタキシャル膜および他の膜をエッチングするためにHClおよびCl2に該基板を暴露するステップとを含む。多数の他の態様が提供される。 (もっと読む)

半導体基板及びその製造方法

【課題】小さい寄生容量及び高いキャリヤ移動度を有する半導体基板を提供する。

【解決手段】Si基板10と、Si基板10上に形成された所定幅のSiO2層12と、両側にそれぞれ第1の端部40a及び第2の端部40bを有し、第1の端部40a及び第2の端部40bから側方向のエピタキシャル成長によって形成され、SiO2層12を覆うSiGe層40と、SiO2層12に対応してSiGe層40上にエピタキシャル成長によって形成され、Siの格子変形が誘導されたストレインSi層50と、を備える半導体基板である。

(もっと読む)

並列ウエハ処理リアクタのための基板キャリア

並列ウエハ処理リアクタのための基板キャリアは、複数の基板を支持する。上記基板キャリアは、垂直スタックに水平に配列されるサーマルプレート又は環状リングでよい複数のサセプタを含む。上記基板は、サセプタの対の間でそれらサセプタの外周をめぐって設けられた2つ又はそれ以上のサポート上に取り付けられる。サセプタの各対の間に取り付けられる基板の数は、同じであっても異なっていてもよいが、サセプタの少なくとも1つの対の間では2つ又はそれ以上である。 (もっと読む)

半導体装置および半導体装置の製造方法

【課題】 トランジスタの信頼性の劣化を抑制しつつ、高電圧駆動を可能とするとともに高速化を図る。

【解決手段】 酸化防止膜4をマスクとしてエピタキシャル成長を行うことにより、第1単結晶半導体層3上に第2単結晶半導体層5を形成し、酸化防止膜4をマスクとして第2単結晶半導体層5の熱処理を行うことにより、第2単結晶半導体層5の構成成分を第1単結晶半導体層3内に拡散させ、第1単結晶半導体層3の一部を第3単結晶半導体層7に変換した後、第1単結晶半導体層3上および第3単結晶半導体層7上に第4単結晶半導体層8を形成し、第3単結晶半導体層7上に配置された第4単結晶半導体層8上にゲート絶縁膜11を形成するとともに、オフセットゲート層15bおよびドレイン層15cを第1単結晶半導体層3および第4単結晶半導体層8に形成する。

(もっと読む)

シリコンゲルマニウム層の低温選択エピタキシャル成長

本発明は、概して、選択エピタキシャル成長プロセスを用いて半導体基板上に歪シリコンゲルマニウム層(strained-SiGe-layer)又は緩和シリコンゲルマニウム層(relaxed-SiGe-layer)又は傾斜シリコンゲルマニウム層(graed-SiGe-layer)を成長させる方法及び手段に関する。特に、本発明は、600℃よりも低い温度でハロゲルマン前駆体物質及びシラン前駆体物質を用いてSiGe層をエピタキシャリーに成長させる方法を提供する。 (もっと読む)

超低水分Oリングおよびその準備のための方法

所望のガス発生率を達成するのに十分な時間(18)の期間、標準Oリング(16)を不活性雰囲気において真空下に置くことにより、超低水分Oリングが準備される。熱は加えられない。Oリングが真空下にある間に、水分は拡散輸送を介してOリング(20)から除去される。  (もっと読む)

(もっと読む)

歪みシリコンウェーハおよびその製造方法

【課題】貫通転位密度が低減され、かつ歪み緩和されたSiGe層を有する歪みシリコンウェーハおよびその製造方法を得る。

【解決手段】本歪みシリコンウェーハは、単結晶シリコン基板上に格子不整合性のあるエピタキシャルSiGe層と、窒素濃度が1×1019atoms/cc以上の窒化膜層と、歪みSi層とを備えたことを特徴としている。

(もっと読む)

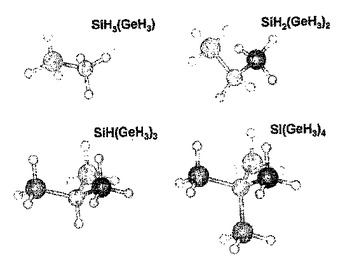

基板上でのSi−Ge半導体材料およびデバイスの成長方法

Geリッチな含有率(Ge>50原子%)および正確な化学量論的SiGe、SiGe2、SiGe3およびSiGe4を有するSi−Ge材料をSi(100)上に成長させる方法が提供される。化合物(H3Ge)xSiH4−x(x=1〜4)の群から得られる直接Si−Ge結合を有する新たな水素化物を用いて、約300〜450℃という前例のない低温で、欠陥密度の低い均一でリレーされた(relayed)高度に平面状の膜を成長させることで、厚い組成勾配のある緩衝層およびリフトオフ法を用いる必要が全くなくなる。約500〜700℃では、SiGex量子ドットが、狭い径分布、無欠陥微細構造および原子レベルで高度に均質な元素含有率にて成長する。その方法は、気体前駆体の全Si/Ge骨格の膜への組み込みを介して、形態、組成、構造および歪みの正確な制御を提供するものである。成長した材料は、高周波数電子および光学システム、ならびに高移動度SiおよびGeチャネルに基づく商業的デバイスの開発のための鋳型および緩衝層での利用に必要な形態的および微細構造的特徴を有している。  (もっと読む)

(もっと読む)

歪みシリコンウエハおよびその製造方法

【課題】 SiGe層を有する歪みシリコンウエハにおいて、SiGe層上に形成される歪みSi層における貫通転位密度の一層の低減化を図ることができる歪みシリコンウエハおよびその製造方法を提供する。

【解決手段】 単結晶シリコン基板上に、Ge濃度を段階的に増加させたSi1-xGex組成傾斜層を形成させる工程と、Ge濃度が一定であるSi1-xGex緩和層を成長させる工程と、Ge濃度yが一定で、0.5x≦y<xである歪み緩和Si1-yGey層を形成させる工程と、さらに、前記歪み緩和Si1-yGey層上に、歪みSi層をエピタキシャル成長させる工程とを経ることにより、歪みシリコンウエハを製造する。

(もっと読む)

201 - 220 / 241

[ Back to top ]