Fターム[5F045AB01]の内容

気相成長(金属層を除く) (114,827) | 成長層の組成 (12,584) | 4族 (3,529)

Fターム[5F045AB01]の下位に属するFターム

Fターム[5F045AB01]に分類される特許

141 - 160 / 241

ワイドバンドギャップ半導体材料

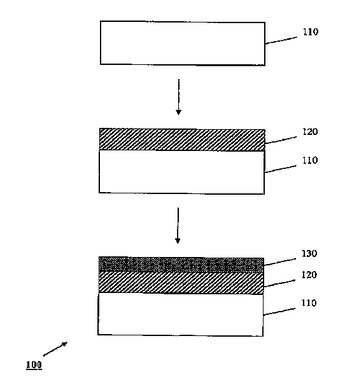

(AlN)x(SiC)(1-x)のような金属―有機アロイ薄膜の上に、バッファーなしに、半導体結晶を成長させる基板及び方法が開示されている。出発材料としてAlNとSiC粉末を用いた蒸着法により、SiC基板の上に(AlN)x(SiC)(1-x)アロイ薄膜は形成されることができる。(AlN)x(SiC)(1-x)アロイ薄膜は、GaNまたはSiCのエピタキシャル成長のためのより良い格子整合を与え、よりよい格子整合と相性によりエピタキシャルに成長されたGaNにおける欠陥を減少させる。  (もっと読む)

(もっと読む)

エピタキシーチャンバにおける基板の予備洗浄

【課題】 予備洗浄エッチングと減圧処理を含む基板を処理する方法を開示する。

【解決手段】 予備洗浄エッチング処理は、基板を処理チャンバに導入するステップと;処理チャンバにエッチングガスを流すステップと;基板の少なくとも一部をエッチングで処理して汚染された又は損傷した層を基板表面から除去するステップと;エッチングガスの流れを停止するステップと;処理チャンバを排気してチャンバ内の減圧を達成するステップと;基板表面を減圧で処理するステップと;を含む。

(もっと読む)

半導体装置の製造方法

【課題】低温で自然酸化膜または有機物等の汚染物を除去できる基板処理装置、基板処理方法、および半導体装置の製造方法を提供することにある。

【解決手段】一部分にSi面が露出した基板を処理室内に搬入する工程と、前記基板を所定の温度に加熱する工程と、前記処理室内に少なくとも塩素ガスを供給し、少なくとも前記Si面の表面に存在する自然酸化膜または汚染物をエッチング処理する工程と、前記処理室内に少なくともSiを含むガスまたはSiを含むガスとGeを含むガスを供給し、前記エッチング処理が施された前記Si面の上に、SiまたはSiGeのエピタキシャル膜を成長する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体バッファ構造

厚い傾斜バッファ層中の貫通転位のパイル−アップは、転位映進を促進することにより低減される。傾斜SiGeバッファ層の形成中に、シリコン前駆体及びゲルマニウム前駆体からのSiGe堆積は、1つ以上の期間において中断される。該期間においては、基板へのゲルマニウム前駆体のフローが維持されているが、基板へのシリコン前駆体のフローが止められている。 (もっと読む)

GeSn半導体デバイスの製造方法

【課題】不整合転位や不純物をほとんど含まず良質であり、光デバイスとして利用可能なGeSn半導体デバイスを得る。

【解決手段】シリコン基板1に形成した極薄酸化膜2上に分子線エピタキシャル法を用いてGe5とSn6とを蒸着することで、GeSn半導体のナノメーターサイズの微結晶(ナノドット)3を超高密度に形成して、GeSn半導体デバイスを得る。該半導体のドット3は不整合転位や不純物をほとんど含まず良質であり、光デバイスとして利用することができる。

(もっと読む)

基板処理装置

【課題】本発明は、基板上に自然酸化膜が形成されるのを抑制することができる基板処理装置を提供することを課題とする。

【解決手段】処理装置101は、ウエハを熱処理する処理室201と、処理室201内を加熱するヒータ206と、処理室201と炉口を介して連接するロードロック室141と、処理室201内へ水素ガスを供給する第3のガス供給源182と、前記炉口を開閉するための炉口ゲートバルブ147と、ロードロック室141内のガスを排出する排気装置300と、コントローラ240と、を備えている。そして、コントローラ240は、処理室201内が所定温度に加熱されている状態で、炉口ゲートバルブ147の開放、第3のガス供給源182によるガス供給、および、排出装置300によるガス排出を実行することで、処理室201内で加熱されたガスでロードロック室141内の壁面を加熱させる。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びその製造方法

【課題】 本願発明は、高コレクタ電流時、高速動作を維持できるSiGeCヘテロ接合バイポーラトランジスタ、及びその製造方法を提供する。

【解決手段】 SiGeCヘテロ接合バイポーラトランジスタの代表例のコレクタは、n型単結晶Si層、及びn型単結晶SiGe層からなる。又、ベースは高濃度p型単結晶SiGeC層からなり、更にエミッタはn型単結晶Si層からなる。n型単結晶SiGe層とp型単結晶SiGeC層のヘテロ界面において、p型単結晶SiGeC層のバンドギャップは、n型単結晶SiGe層以上である。コレクタ電流の増加によって、実効的な中性ベースが拡大した場合でも、n型単結晶SiGe層とp型単結晶SiGeC層のヘテロ界面における伝導帯に、エネルギー障壁が発生しない。このため、電子の拡散が阻害されないことから、高注入状態においても、高速動作性能を維持できるヘテロ接合バイポーラトランジスタを実現でき、これを用いた回路の高性能化が可能となる。

(もっと読む)

選択的堆積

基板の表面上にシリコン含有材料をエピタキシャルに形成する方法は、プロセスチャンバー温度及び圧力の調整を通じてハロゲン含有ガスをエッチングガス及び担体ガスの両方として使用する。HClをハロゲン含有ガスとして使用するのが有益である。なぜなら、HClを担体ガスからエッチングガスへ変換することが、チャンバー圧力の調整で容易に遂行できるからである。 (もっと読む)

光電変換素子用基板の製造方法

【課題】Si/Ge系構造のタンデム型光電変換素子の低コスト化を可能とする基板を提供すること。

【解決手段】シリコン基板100の表面にバルクの導電型とは反対の導電型のシリコン層10Bを設け、表面領域の所定の深さ(L)にシリコン層10Bを介して水素イオンを注入して水素イオン注入層11を形成する。続いて、シリコン層10Bと反対の導電型のn型のゲルマニウム系結晶層20A、および、ゲルマニウム系結晶層20Aと反対の導電型のp型のゲルマニウム系結晶層20Bを順次気相成長してゲルマニウム系結晶20を設ける。ゲルマニウム系結晶層20Bの表面と支持基板30の表面とを貼り合わせ、この状態で外部から衝撃を付与して水素イオン注入層11に沿ってシリコン基板100からシリコン結晶10を分離して、ゲルマニウム系結晶20とシリコン結晶10の積層構造体を支持基板30上に転写(剥離)する。

(もっと読む)

半導体薄膜の成膜方法および半導体薄膜の成膜装置

【課題】基板上に結晶質の半導体薄膜を成膜する際、膜質の良好な結晶性の半導体薄膜を得ることが可能な半導体薄膜の成膜方法および成膜装置を提供する。

【解決手段】エッチング性ガスと半導体材料を含有する成膜ガスとを加熱した基板表面に供給することにより、基板表面においてエッチング性ガスと成膜ガスとを熱化学反応させ、基板表面に結晶質の半導体薄膜を成膜する成膜方法において、エッチング性ガスと成膜ガスとは、基板表面に対向配置され冷媒管18によって冷却状態に保たれたシャワープレート17から基板表面の全面に対して供給される。

(もっと読む)

薄膜製造装置及び太陽電池の製造方法

【課題】放電電極と対向電極との間に形成される高周波プラズマを容易に均一にすることが可能な薄膜製造装置を提供する。

【解決手段】製膜室6と放電電極3と対向電極2と高周波電源60と整合器13と電極インピーダンス調整部40とを具備する薄膜製造装置を用いる。放電電極3は製膜室6内に設けられている。対向電極2は放電電極3に対向するように接地されて設けられ、基板8を保持可能である。高周波電源60は放電電極の給電点53、54に伝送線路12、14を介して高周波電力を供給する。整合器13は伝送線路12、14の途中に接続され、高周波電源60と放電電極3とのインピーダンスを整合する。電極インピーダンス調整部40は放電電極3に電気的に接続され、放電電極3のインピーダンスを調整する。

(もっと読む)

半導体層構造及び半導体層構造の製造方法

【課題】半導体材料の応力及び亀裂のない堆積のための基板と、かかる基板の製造方法を提供する。

【解決手段】半導体層構造の製造方法にあたり、a)半導体材料からなる基板を準備し、b)前記基板上に第二の半導体材料からなる層を施与して、半導体構造を作製し、c)該半導体層構造中に軽ガスイオンを注入して、半導体層構造内に空洞を含む層を作製し、d)前記空洞を規定種の不純物原子によって安定化し、e)該半導体層構造上に少なくとも1層のエピタキシャル層を施与する。

(もっと読む)

半導体基板及びその製造方法

【課題】 欠陥の充分少ない高品質な歪みSi基板を提供する。

【解決手段】 半導体基板の製造方法は、支持基板とは格子定数の異なるヘテロエピタキシャル層、多孔質層、Si層が順に積層された構造を少なくとも含む支持基板に、前記Si層の歪みを変化させるために、前記ヘテロエピタキシャル層の応力を変化させる工程を行なう。

(もっと読む)

光電変換素子及びその製造方法並びに薄膜形成装置

【課題】 短絡電流密度が向上した光電変換素子を提供することを目的とする。また短絡電流密度が向上した光電変換素子を製造するための製造方法及び薄膜形成装置を提供することを目的とする。

【解決手段】 pin接合またはnip接合からなる光電変換層を有する光電変換素子において、光電変換層における真性半導体層を微結晶シリコンゲルマニウムにより形成し、この真性半導体層中の酸素濃度を1020個/cm3未満とする。

(もっと読む)

半導体基板製造方法

【課題】CVD炉内におけるウェハの温度分布を均一化して、ウェハ表面に膜厚の均一な半導体膜を形成する。

【解決手段】CVD炉2内のサセプタ3にシリコンウェハWを載置し、CVD炉2の上下に配置したランプヒータ5U、5Lによりサセプタ3並びにシリコンウェハWを加熱しつつ、シリコンウェハWの表面に材料ガスGを供給して半導体膜を成長させる際、サセプタ3の下部の温度がシリコンウェハWの表面部の温度よりも10度〜100度高くなるようにランプヒータ5U、5Lを制御する。サセプタ3内における熱拡散を利用してサセプタ3表面の温度分布を均一化できるので、サセプタ3上に載置されたシリコンウェハWの温度分布を均一化してその表面に膜厚の均一な半導体膜を形成することができる。

(もっと読む)

SGOI基板の製造方法

【課題】本発明はSGOI基板及びその製造方法を提供する。

【解決手段】SOI基板上に歪み緩和SiGe層を有する歪み緩和SGOI基板の製造方法であって、(1)SOI基板のSi層上に、760トール未満の減圧CVD装置を用いて、雰囲気ガスがSiH4/GeH4で、かつ成長温度が550〜950℃でSiGe層をエピタキシャル成長させて、Ge濃度が10〜30%であり、表面平坦性が100μm2の観察領域でRMS値<0.5nm、クロスハッチ状の周期的表面凹凸を有しない歪みSiGe層を設け、(2)前記歪みSiGe層を有するSOI基板を900〜1350℃、50時間以内で熱処理して、Ge濃度を増大させ、ないしは増大させること無く、かつ歪みを緩和すること、を特徴とする。

(もっと読む)

有機金属組成物

【課題】有機金属組成物の提供

【解決手段】ゲルマニウム含有膜の蒸着前駆体として用いるのに好適なゲルマニウム化合物を含有する組成物が提供される。かかる組成物を用いる、ゲルマニウムを含有する膜の堆積方法も提供される。かかるゲルマニウム含有膜は電子装置の製造において特に有用である。

(もっと読む)

透明基板を用いる多結晶シリコン薄膜の製造方法及び製造装置

【解決手段】本発明は、透明基板を用いた多結晶シリコン薄膜の製造方法及び製造装置であり、RTP光源を、熱処理源ではなく、多結晶シリコン蒸着のためのエネルギー源として用いるものであり、その方法は、透明基板上に光吸収層を形成し、RTP(Rapid Thermal Process)光源の照射により光吸収層を加熱しながら、光吸収層上に多結晶シリコン薄膜を蒸着することを行うことで、電気的特性が良好な多結晶シリコン薄膜を製造することができる。 (もっと読む)

半導体基材及びその製造方法

【課題】IV族半導体多結晶の低温成長において、結晶性に優れ、かつ結晶粒径や配向性を制御した高品質のIV族半導体多結晶の成長を可能にする半導体基材の製造方法及び得られた半導体基材を提供する。

【解決手段】550℃以下の温度でハロゲン化ゲルマニウムとシラン類を原料とする熱CVD法を用いて、非晶質、多結晶あるいは金属などの基材上にSiGeあるいはGeの結晶核を形成し、該結晶核上に気相堆積法でSi多結晶膜を形成する半導体基材の製造方法により、上記課題を解決する。また、本発明の半導体基材は、非晶質、多結晶あるいは金属などの基材と、該基材上にハロゲン化ゲルマニウムとシラン類を原料とする熱CVD法で形成されたSiGeあるいはGeの結晶核と、該結晶核上に気相堆積法で形成されたSi多結晶膜とを有する。

(もっと読む)

基板上に積層する多結晶シリコンゲルマニウム層中の内部応力を制御する方法

【課題】基板上に積層する多結晶シリコンゲルマニウム層中の内部応力を制御する方法を提供する。

【解決手段】本発明の基板上に積層する多結晶シリコンゲルマニウム層中の内部応力を制御する方法は、シリコンゲルマニウム層内の内部応力の範囲を選択するステップ、蒸着圧力を選択するステップ、及び、蒸着温度を選択するステップを含み、シリコンゲルマニウム層内の内部応力が選択した範囲内となるように、蒸着圧力と蒸着温度のうちの少なくとも一つが選択されることを特徴とする。

(もっと読む)

141 - 160 / 241

[ Back to top ]