Fターム[5F045AB05]の内容

気相成長(金属層を除く) (114,827) | 成長層の組成 (12,584) | 4族 (3,529) | Ge (202)

Fターム[5F045AB05]に分類される特許

1 - 20 / 202

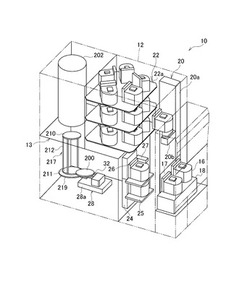

基板処理装置及び半導体装置の製造方法

【課題】 処理室内の異物を低減することで、基板処理の品質を向上させ、生産歩留りを改善する。

【解決手段】 基板を処理する処理室と、基板を保持し、処理室内外に搬送される基板保持具と、基板保持具への基板の装填、又は基板保持具からの基板の脱装が行われる移載室と、移載室内の基板保持具に、不活性ガスを噴射するノズルを備える不活性ガス供給機構と、処理室内から移載室内に搬出されて基板が脱装された基板保持具に、ノズルから不活性ガスを噴射するように不活性ガス供給機構を制御する制御部と、を備え、ノズルは、上方から下方に向かって角度をつけて不活性ガスを噴射する。

(もっと読む)

半導体装置の製造方法

【課題】ヒ素(As)を高濃度にドーピングした状態でエクステンション領域のエピタキシャル成長膜表面に凹凸を発生させることなく、平滑な面に形成することを可能とする。

【解決手段】半導体基板11上にゲート絶縁膜12を介してゲート電極13を備え、前記ゲート電極13の両側の前記半導体基板11上に形成された不純物を含有してなるエクステンション領域17、18を備えた半導体装置1であって、前記エクステンション領域17、18は、シリコンゲルマニウムにヒ素を含む状態でエピタキシャル成長されたエピタキシャル成長膜からなり、このエピタキシャル成長膜は、ヒ素をドーピングしながらシリコンとゲルマニウムとを前記半導体基板11上に選択的にエピタキシャル成長させて形成される。

(もっと読む)

シリコン基板上に高電子移動度トランジスタを成長させた構造及びその方法

【課題】シリコン基板上に高電子移動度トランジスタを成長させた構造及びその方法の提供。

【解決手段】本シリコン基板上に高電子移動度トランジスタを成長させた構造及びその方法は、半導体産業において半導体装置製造に用いられる。本発明によると、UHVCVDシステムを使用してGeフィルムをSi基板上に成長させ、その後、高電子移動度トランジスタを該Geフィルム上に成長させることで、バッファ層の厚さとコストを低減する。該Geフィルムの機能は、Si基板上にMOCVDによりIII-V MHEMT構造を成長させるときに、シリコン酸化物の形成を防止することである。本発明においてMHEMTを使用する理由は、MHEMT構造中の変成バッファ層がGeとSi基板間の非常に大きな格子不整合度のために形成される貫通転位をブロックし得ることにある。

(もっと読む)

気相成長装置

【課題】結晶膜を基板の上に成長させる化学気相成長(CVD)の量産では、均一性を改良しながらバッチサイズを大きくする装置構造が課題である。装置の部品の洗浄交換周期を長くし、CVDガスの基板上での消費効率を上げて、排気系のポンプや排気配管への付着を減らしたい。さらに有機金属ガスをCVDガスとして用いるとき、気相で重合反応を起こし粒子ゴミを発生させるので、加熱空間を横切る流路を短くしたい。これらの要求を満たす装置の構造が課題である。

【解決手段】表面に基板を載せる複数の加熱されるサセプタを立てて放射状に配置させ、当該放射状配置のサセプタを回転させながら外周から熱分解CVDガスを供給して当該基板の上にCVD膜を成長せしめ、当該放射状配置サセプタの配置中心に加熱可能な排気管が配置されてあり、当該CVDガスを当該排気管から排気することで、課題を解決する結晶膜の気相成長装置が可能である。

(もっと読む)

半導体装置

【課題】オフ電流を低減した優れた特性を有する薄膜トランジスタを作製する。

【解決手段】p型の逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜側から、微結晶半導体領域、非晶質半導体領域、及び不純物半導体領域が積層される半導体膜と、一対の配線とが接する領域が、ゲート絶縁膜を介してゲート電極と重畳し、一対の配線の仕事関数と、微結晶半導体領域を構成する微結晶半導体の電子親和力の差である電子のショットキーバリアφBnは0.65eV以上である。

(もっと読む)

プラズマ装置

【課題】薄膜がアンテナに付着するのを抑制可能なプラズマ装置を提供する。

【解決手段】プラズマ装置は、アンテナ1を備える。アンテナ1は、絶縁管1aと、導体1bと、伝熱材1cとを含む。絶縁管1aは、略U字形状を有し、Al2O3からなる。導体1bは、略U字形状からなり、筒状部分1dを有する。筒状部分1dには、冷却水が流される。そして、導体1bは、絶縁管1a内に挿入される。伝熱材1cは、絶縁管1aと導体1bとの間に充填される。そして、伝熱材1cは、シリコン樹脂からなる。

(もっと読む)

新規な水素化シリコンゲルマニウム、その製造法および使用法

【課題】本発明は、新規水素化シリコンゲルマニウム化合物、それらの合成法、それらの成膜法、およびそれらの新規化合物を用いて作製された半導体構造を提供する。

【解決手段】これらの化合物は、式:(SiHn1)x(GeHn2)yによって定義される。式中、xは2,3または4であり;yは1,2または3であり;x+yは3,4または5であり;n1は、化合物中の各Si原子に関して独立に0,1,2または3であって原子価を満たし;n2は、化合物中の各Ge原子に関して独立に0,1,2または3であって原子価を満たし;但し、yが1のとき、n2は0ではなく;さらに、xが3、かつ、yが1のとき、n2は2または3であり;さらに、xが2、かつ、yが1のとき、n2は3である。

(もっと読む)

多層膜構造体及びその形成方法

【課題】新規な多層膜構造体及びその形成方法を提供すること。

【解決手段】半導体素子用の多層膜構造体の形成方法であって、シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、前記半導体層上に表面保護層を形成する表面保護層形成工程と、前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層形成工程と、前記表面保護層を除去する除去工程と、前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする多層膜構造体の形成方法。

(もっと読む)

熱処理装置の運転方法

【課題】ゲルマニウムを含む薄膜の成膜処理をした後に、ゲルマニウムが汚染物質となる薄膜を成膜処理する場合に、後の成膜処理におけるゲルマニウム汚染を抑える熱処理装置の運転方法を提供する。

【解決手段】被処理体Wを保持具25に保持させて反応容器2内に搬入し、熱処理を行う熱処理装置1の運転方法において、反応容器2内に処理ガスを供給すると共に反応容器2内を加熱して、被処理体Wにゲルマニウムを含む薄膜を成膜する工程と、反応容器2内に被処理体Wが搬入されていない状態クリーニングガスを供給して前記反応容器2内に成膜された薄膜を除去する工程と、酸化ガスと、水素ガスとを反応容器2内に供給すると共に加熱して活性化されたガスにより反応容器2内に存在するゲルマニウムを除去する工程と、反応容器2内に被処理体Wを搬入して処理ガスを供給すると共に加熱して、被処理体にゲルマニウムが汚染物質となる薄膜を成膜する工程、とを含む。

(もっと読む)

ナノ結晶を有する半導体デバイスを形成する方法

【課題】

ナノ結晶を有する半導体デバイスを形成する方法を提供する。

【解決手段】

ナノ結晶を有する半導体デバイス10を形成する方法は、基板12を設けるステップと、基板の表面の上方に第1絶縁層14を形成するステップと、第1絶縁層上に第1の複数のナノ結晶26(21、22)を形成するステップと、第1の複数のナノ結晶上に第2絶縁層28を形成するステップと、第2絶縁層に第1材料を注入するステップと、第1材料をアニールして第2絶縁層内に第2の複数のナノ結晶34(36、37)を形成するステップとを含む。この方法は、より高いナノ結晶密度を有する不揮発性メモリの電荷格納層を提供するために使用され得る。

(もっと読む)

クリーニングガス及びそれを用いたリモートプラズマクリーニング方法

【課題】CVD装置内の堆積物のリモートプラズマクリーニング法に用いられるクリーニングガスにおいて、地球温暖化係数が低く、かつ、高いエッチング速度が得られるクリーニングガス、及びそれを用いるリモートプラズマクリーニング方法を提供する。

【解決手段】CVD装置の反応チャンバー1内に堆積した、Si含有物、Ge含有物、又は金属含有物を、リモートプラズマクリーニング法により除去するクリーニングガスにおいて、該ガスはCFxOy[但し、xは2又は4であり、x=2のときy=1〜3の整数、x=4のときy=1〜4の整数を表す。]とN2が含有されている混合ガスである。

(もっと読む)

微結晶半導体膜及びその作製方法、並びに半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜及びその作製方法を提供する。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】厚さが70nm以上100nm以下の微結晶半導体膜であり、微結晶半導体膜の表面から一部が突出する結晶粒を有し、当該結晶粒は配向面を有し、且つ13nm以上の大きさの結晶子を有する微結晶半導体膜である。また、微結晶半導体膜の膜密度が2.25g/cm3以上2.35g/cm3以下、好ましくは2.30g/cm3以上2.33g/cm3以下である。

(もっと読む)

半導体材料の選択堆積方法

【課題】シリコンやゲルマニウムのようなIV族半導体材料を、半導体表面上に、絶縁表面上への堆積無しに選択的に堆積する方法を提供する。

【解決手段】半導体プロセスで半導体材料の選択成長を行う方法が、第1領域11と第2領域12とを含むパターニングされた基板10を提供する工程を含み、第1領域11は露出した第1半導体材料を含み、第2領域12は露出した絶縁材料を含む。この方法は、更に、第2半導体材料の前駆体、Cl化合物とは応性しないキャリアガス、および錫テトラクロライド(SnCl4)を供給することにより、第1領域の第1半導体材料の上に第2半導体材料の膜を選択的に形成する工程を含む。錫テトラクロライドは、第2領域の絶縁材料上への第2半導体材料の堆積を阻害する。

(もっと読む)

ゲルマニウム層の直接成長方法

【課題】化学気相堆積により、基板上にGeの連続した層を堆積する方法を提供する。

【解決手段】非反応性キャリアガスと、高次のゲルマニウム前駆体ガス、即ちゲルマン(GeH4)より高次のゲルマニウム前駆体ガスとの混合物が適用される。好適には、約275℃と約500℃との間の堆積温度で堆積が行われ、混合物中の前駆体ガスの分圧は、約275℃と約285℃との間の温度で少なくとも20mTorrであり、約285℃と約500℃との間の温度で少なくとも10mTorrである。

(もっと読む)

薄膜製造装置及び薄膜製造方法

【課題】特性の良い半導体薄膜を高速且つ安価に製造することができる薄膜製造装置を提供する。

【解決手段】本発明に係る薄膜製造装置は、成膜室31に導入した複数の原料ガスをプラズマCVDにより基板上に成膜する薄膜製造装置において、前記複数の原料ガスを、各々の固体の原料をプラズマエッチングによりエッチングガスと反応させることで生成する原料ガス生成室12及び22と、前記原料ガス生成室12及び22内の圧力が、5000Pa以上大気圧以下、前記成膜室31内の圧力が500Pa以下となるように、それぞれの圧力を調整する圧力コントローラ19、29及び39と、前記原料ガス生成室12及び22と前記成膜室31の圧力差を維持しつつ、前記原料ガス生成室で生成された原料ガスを前記成膜室に導入するためのニードルバルブ17及び27と、を有することを特徴とする。

(もっと読む)

UV線を用いたシリコン含有膜の低温エピタキシャル成長

【課題】シリコン含有及び/又はゲルマニウム含有膜の一括的又は選択的エピタキシャル堆積の清浄な基板表面を調製する方法を提供する。更に、シリコン含有及び/又はゲルマニウム含有膜を成長させる方法であって、基板洗浄方法と膜成長方法の双方が750℃未満、典型的には約700℃〜約500℃の温度で行われる前記方法を提供する。

【解決手段】洗浄方法と膜成長方法は、シリコン含有膜が成長している処理容積において波長が約310nm〜約120nmの範囲にある放射線の使用を用いる。反応性洗浄又は膜形成成分化学種の具体的な分圧範囲と組み合わせたこの放射線の使用は、業界で以前に知られている温度より低い温度で基板洗浄とエピタキシャル膜成長を可能にする。

(もっと読む)

窒化物上へゲルマニウム・スペーサを選択的に堆積するための構造及び方法

【課題】 窒化物上へゲルマニウム・スペーサを選択的に堆積するための構造及び方法を提供すること。

【解決手段】 半導体製造プロセス中でゲルマニウム構造体を選択的に形成する方法は、化学的酸化物除去(COR)プロセスにおいて自然酸化物を除去し、次いで、加熱された窒化物及び酸化物表面を加熱されたゲルマニウム含有ガスに曝して、ゲルマニウムを選択的に窒化物表面上にだけ形成し、酸化物表面上には形成しない。

(もっと読む)

基板処理装置及び被処理基板の製造方法

【課題】基板を誘導加熱する際に、放射温度計を用いて正確な温度測定が可能な基板処理技術を提供する。

【解決手段】複数の基板を収容して処理する反応管と、該反応管の内部に設けられ、複数の基板を加熱する積層された複数の被誘導加熱体と、前記複数の被誘導加熱体からの光を同時に集光する集光部を備え、該集光部が同時に集光した被誘導加熱体からの光に基づき、前記複数の被誘導加熱体の温度を測定する放射温度計と、前記反応管の外部に設けられ、前記放射温度計が測定した温度情報に基づき、前記被誘導加熱体を誘導加熱する誘導加熱体と、を有するように基板処理装置を構成する。

(もっと読む)

半導体材料の選択堆積方法

【課題】第2半導体材料と絶縁材料とを含む基板上に、第1半導体材料を選択的に堆積する方法の提供。

【解決手段】第1半導体材料が第2半導体材料上に選択的に堆積され、この方法は、a)炭素および/またはハロゲン含有ガスから形成されたプラズマを用いて基板を前処理する工程と、b)化学気相堆積により、基板上に第1半導体材料を堆積する工程とを含む。

【効果】特に、半導体デバイス機構の製造のための改良された方法に関する。

(もっと読む)

半導体基板上での逆相境界の無いIII−V化合物半導体材料およびその製造方法

【課題】逆相境界(APB)の無いIII−V化合物半導体材料およびその製造方法を提供する。

【解決手段】III−V化合物半導体材料の製造方法は、a){001}配向を有する第1半導体材料からなる基板と、基板の上に位置し、これと接触する絶縁層と、絶縁層内に、少なくとも部分的に基板を露出させる凹部領域を用意する工程と、b)凹部領域において露出基板の上に位置し、これと接触するバッファ層を形成する工程工程と、c)バッファ層の表面を粗面化するために、熱処理を印加する工程とを含み、バッファ層が、熱処理の印加後に二重ステップ表面を有する丸み形状をなし、d)凹部領域を、バッファ層の二重ステップ表面の上に位置し、これと接触するIII−V化合物半導体材料で少なくとも部分的に充填する工程をさらに含む。

(もっと読む)

1 - 20 / 202

[ Back to top ]