Fターム[5F045AC07]の内容

気相成長(金属層を除く) (114,827) | 導入ガス (14,721) | 有機化合物ガス (3,422)

Fターム[5F045AC07]の下位に属するFターム

Fターム[5F045AC07]に分類される特許

1,501 - 1,519 / 1,519

傾斜した堆積を低減するためのハードウェア開発

本発明による実施形態は、半導体被加工物(882)の傾斜上の材料の堆積を低減する、またはなくすために単独または組み合わせて用いることができる種々の技術に関連する。一アプローチでは、傾斜領域へのガスの流れを妨げるためにシャドーリング(880)が基板(882)のエッジを覆っている。エッジをシャドーする間にウエハー全域で厚さの均一性を維持するために、シャドーリングのエッジ(880a)での形体がガスの流れをウエハーに向けて方向付ける。別のアプローチでは、基板ヒータ/支持部がパージガスを支持されている基板のエッジに流すように構成されている。これらのパージガスは、プロセスガスが基板エッジに達して傾斜領域上に材料が堆積するのを防ぐ。 (もっと読む)

アモルファス炭素膜のCVD堆積用の液体前駆体

アモルファス炭素材料を堆積するための方法が提供される。一態様では、本発明は、処理チャンバに基板を位置決めするステップと、該処理チャンバに処理ガスを導入するステップであって、該処理ガスがキャリアガス、水素および1つ以上の前駆体化合物を含むステップと、二重周波数RF源から電力を印加することによって該処理ガスのプラズマを生成するステップと、該基板上にアモルファス炭素層を堆積するステップとを含む基板処理方法を提供する。 (もっと読む)

半導体装置の製造方法

濃度1から10%のSiH3CH3をH2により希釈し、希釈したSiH3CH3の一部と、GeH4と、SiH4(またはDCS)とをそれぞれ所定の流量でエピタキシャル装置のチャンバへ供給し、SiGe:Cをエピタキシャル成長技術により形成する。SiH3CH3を希釈することにより、SiH3CH3に含まれる酸素系不純物の濃度が低減するので、チャンバへ供給される酸素系不純物が低減して、成膜されるSiGe:Cに含まれる酸素系不純物の濃度が低減する。 (もっと読む)

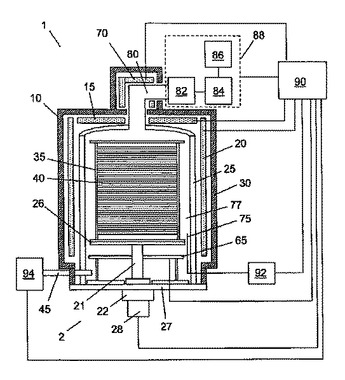

液状前駆物質のための高性能蒸発器、及び、半導体の薄膜蒸着における複数の液状前駆物質の蒸発

薄膜形成のため、及び、半導体表面上に膜を析出するための析出チャンバー(26、84、130)に蒸気を導入するための蒸発系(50、92、92a、92b、180)であって、この系は蒸発チャンバー(52、116、192)を有し、蒸発チャンバーには、ガスストリーム中で運ばれる少なくとも2つの異なる独立した液状前駆物質(54A、54B、54C、110A、110B、186)が選択的に提供される。ガスストリームは、ガス供給源(12、62A、62B、62C、98A、98B、184)からの単一のキャリヤガスか、又は複数のキャリヤガスのうち選択された1つであってもよい。導入しようとする液体が、高温表面との接触により熱分解を受けやすい場合は、蒸発チャンバー(52、116、192)の入口で噴霧器(94、142A、142B、154A、154B、182)を使用して、蒸発チャンバー(52、116、192)に同時又は連続的に導入するためのガス供給源12、62A、62B、62C、98A、98Bからの1種又はそれより多い個々のキャリヤガスから、蒸発チャンバー(52、116、192)にエアロゾルを提供する。蒸発チャンバー(52、116、192)は、蒸発させたガス/蒸気混合物が蒸発チャンバー(52,116,192)から出る前に、加熱された通路(198、124、202、212)を通る再循環ガスフローを組み込むことにより、完全な蒸発が確実になるように設計してもよい。  (もっと読む)

(もっと読む)

半絶縁III族窒化物においてフェルミ準位を制御するための同時ドーピング

半絶縁III族窒化物層および半絶縁III族窒化物層の製造方法は、III族窒化物層を浅い準位のp型ドーパントでドーピングすること、およびIII族窒化物層を、例えば深い準位の遷移金属ドーパントなどの深い準位のドーパントでドーピングすることを有する。このような層および/または方法はまた、III族窒化物層をおよそ1×1017cm−3よりも小さい濃度を有する浅い準位のドーパントでドーピングすること、およびIII族窒化物層を深い準位の遷移金属ドーパントでドーピングすることを有する。深い準位のドーパントの濃度は、浅い準位のp型ドーパントの濃度よりも大きい。  (もっと読む)

(もっと読む)

高品質低温窒化シリコン層を形成する方法及び装置

窒化シリコン層を形成する方法が記載される。本発明によれば、窒化シリコン層は、シリコンと窒素を含有するソースガス又はシリコン含有ソースガスと窒素含有ソースガスを低堆積温度(例えば、550℃未満)で熱分解して窒化シリコン層を形成することにより堆積される。その後、熱的に堆積した窒化シリコン層を水素ラジカルで処理して処理された窒化シリコン層を形成する。 (もっと読む)

窒化ケイ素の熱化学気相堆積

処理領域と、基板支持体と、ガス分配システムと、ガス混合領域と、フェースプレートに固定されたアダプタリングを所望の温度に加熱するように配置された加熱素子と、温度制御排気システムとを備えた装置。また、ビス(第三級ブチルアミノ)シランを蒸発させ、ビス(第三級ブチルアミノ)シランとアンモニアを処理チャンバへ流し、アダプタリングと少なくとも2つのブロッカープレーで画成された追加の混合領域を有する2つの反応種を合わせ、アダプタリングを加熱し、ビス(第三級ブチルアミノ)シランをガス分配プレートを通って処理領域に流す方法と装置。 (もっと読む)

炭化ケイ素膜およびセラミック膜を堆積するための方法

基体上へセラミック膜、特に炭化ケイ素膜を堆積する方法が開示され、その方法において、残存応力、残存応力勾配、および抵抗率が制御される。これらの制御された特性を備えた堆積された膜を有する基体、およびこれらの特性を備えた膜を有するデバイス、特にMEMSデバイスおよびNEMSデバイスもまた開示される。この堆積された炭化ケイ素膜中の残存応力は、約700MPaと約−100MPaとの間にあり、その電気抵抗率は、約10Ω・cm未満である。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

規格外れの不良ウェハをリアルタイムに検出することができる半導体集積回路装置の製造方法を提供することにある。

異常検知サーバ5は半導体ウェハを処理する半導体製造装置から出力された装置ログデータを装置ログデータ記憶部10に記憶する。その後、ロットエンド信号受信部12において、半導体製造装置から出力されるロットエンド信号を受信すると、異常データ検知部15は、第1検知条件記憶部13に記憶されている異常検知条件設定ファイル13aを参照した後、参照した内容に基づいて装置ログデータ記憶部10に記憶されている装置ログデータの中に異常データがあるか否かを判定する。そして、異常を検知するとエンジニアPCや作業者端末装置に検知結果を出力する。

(もっと読む)

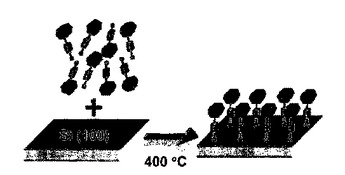

基板への有機分子の高温付着

本発明は、半導体表面、特にシリコンに分子を付着させるための新規手順を提供するものである。ポルフィリンおよびフェロセンを含む(しかし、これらに限定されない)分子が分子ベースの情報記憶のための魅力的な候補であることは、以前に示されてきた。この新規付着手順は、単純であり、短時間に完了させることができ、最少量の材料しか必要とせず、様々な分子官能基と両立でき、場合によっては従来にない付着モチーフを生じる。これらの特徴は、ハイブリッド分子/半導体情報記憶デバイスを作るために必要な加工段階への分子材料の組込みを非常に向上させる。  (もっと読む)

(もっと読む)

ナノサイズヒータ付きノズルおよびその製造方法ならびに微小薄膜の製造方法

ナノサイズヒータ付きノズルは、原料ガスを基板Wに向けて局所的に供給するためのノズルと、ノズルの側面に設けられた一対の電極と、カーボンナノチューブ等からなるナノサイズヒータなどで構成され、ナノサイズヒータは、ノズルの開口部を横切るように各電極にそれぞれ接続され、通電によって原料ガスを加熱する。

こうした構成によって、基板上の限定された領域において、局所的な成膜を容易に実現できる。

(もっと読む)

モノシラン誘導体またはジシラン誘導体、および、それを用いたシリコン含有膜の低温蒸着法

本発明は、ULSIデバイスおよびデバイス構造の製造のための低温(例えば<550℃)化学蒸着法によりシリコン含有膜を形成するケイ素前駆体組成物に関する。かかるケイ素前駆体組成物は、少なくとも1個のアルキルヒドラジン官能基と置換され、ハロゲン置換がない、少なくとも1種のシラン誘導体またはジシラン誘導体を含む。 (もっと読む)

システム構成要素の状態をモニタリングするための方法

バッチ式プロセスシステムのプロセスチャンバにおけるシステム構成要素の状態をモニタリングするための方法及びシステムが提供されている。この方法は、システム構成要素を光源からの光に露出させることと、システム構成要素の状態を決定するためにシステム構成要素との光の相互作用をモニタリングすることとを有している。この方法は、チャンバクリーニングプロセス、チャンバコンディショニングプロセス、基板エッチングプロセス及び基板フィルム形成プロセスを含み得るプロセスの間のシステム構成要素からの光の透過並びに/もしくは光の反射を検出することができる。システム構成要素は、プロセスチューブ、シールド、リング、バッフル及びライナーのようなシステムの消耗する部分であり得て、保護コーティングをさらに有することができる。  (もっと読む)

(もっと読む)

液状又は溶液の原料を用いマルチチャンネル装置を介して不連続に射ち込み、単元又は多元の層及びスタック層を堆積する方法及び装置

【課題】 接触なしで原料を蒸発させて、単元又は多元の層及びスタック層を堆積する方法及び装置を提供する。

【解決手段】 本発明は、プロセスチャンバー(2)内で少なくとも1層を少なくとも1つの基板上に堆積する装置であって、複数の成分からなり、絶縁性、パッシベーション性、又は導電性を有する層と、インジェクタユニット(5)を用いて液状又は液体に溶解した原料(3)を温度制御された蒸発チャンバ(4)に不連続に射ち込むことによって成分が蒸発され、これらの蒸気がキャリアガス(7)によってプロセスチャンバーに供給される装置に関する。各インジェクターユニット(5)を通る流量の時間プロファイルを決定する、射出圧、射出周波数、及びデューティ比、並びにオン/オフの他のインジェクターユニットのオン/オフに対する位相関係等の流量パラメータが個別に設定又は変更されることが基本である。

(もっと読む)

バッチタイプ処理システムにおける順次ガス露出による金属含有膜の形成

【課題】バッチタイプ処理システムにおいて順次ガス露出処理によって基板上に金属含有膜を形成するための方法を提供する。

【解決手段】バッチタイプ処理システムの処理チャンバーに基板を供給し、基板を加熱し、金属含有前駆体ガスのパルスと反応ガスのパルスを処理チャンバーに順に流し、これらの流し処理を所望の膜特性を有する金属含有膜が基板上に形成されるまで繰り返す。この方法によって、HfO2やZrO2などの酸化金属膜、HfxOzNwやHfxOzNwなどの酸窒化金属膜、HfxSiyOzやZrxSiyOzなどのケイ酸金属膜、HfxSiyOzNwやZrxSiyOzNなどの窒素含有ケイ酸金属が形成できる。

(もっと読む)

高純度結晶成長

反応器中に配置された基材上に結晶を成長させる方法であって、この反応器は、反応器チャンバを提供し、この基材は、この反応器チャンバの中に配置され、この方法は、この反応器チャンバの内部に反応性ガスをこの基材に向かって流す工程であって、この反応性ガスは、互いに結合してこの結晶を形成し得る成分を含有する工程;緩衝ガスを加熱する工程;およびこの加熱された緩衝ガスを、この反応性ガスとこの反応器壁との間のこの反応器チャンバ中で、この反応性ガスおよびこの緩衝ガスが相互作用し得るように、流す工程、を包含し、ここでこの流れている緩衝ガスが、この反応性ガスにより生成される第1の物質の少なくとも1つがこの反応器壁に到達するのを阻害し、そしてこの反応性ガスがこの基材に到達する前に、この反応器壁により生成される第2の物質が反応器チャンバー中のこの反応性ガスに到達するのを阻害する。  (もっと読む)

(もっと読む)

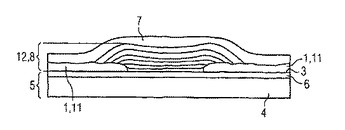

複数のオプトエレクトロニクス半導体チップの製造方法およびオプトエレクトロニクス半導体チップ

本発明は複数のオプトエレクトロニクス半導体チップの製造方法に関し、これらの半導体チップはそれぞれ少なくとも1つの半導体層を備えた複数の構造素子をそれぞれ有する。この方法においては基板ならびに成長表面を有するチップ結合体ベースが提供される。成長表面の上には複数の窓を有するマスク材料層が形成され、これらの窓の大部分は1μm以下の平均的な広がりを有する。マスク材料は後続のステップにおいて成長すべき半導体層の半導体材料がこのマスク材料上では実質的に成長しない、または成長表面に比べて実質的に成長しにくいように選択される。続けて、半導体層が実質的に窓の内部に位置する成長表面の領域の上に析出される。さらなるステップではチップ複合体ベースが被着された材料と共に半導体チップに個別化される。さらに本発明は本方法に応じて製造されるオプトエレクトロニクス半導体チップに関する。  (もっと読む)

(もっと読む)

成膜装置及び成膜方法

【課題】高速性、均一性に優れ、原料ガスの使用効率を高めて成膜コストを低減することを可能とした成膜装置及び成膜方法を提供する。

【解決手段】反応容器1と、該反応容器1内に設けられ、対向して設けられた少なくとも一対の基体7を支持するための支持体6と、該基体7を加熱する手段と、前記一対の基体7間に形成された空間に原料ガスを吐出するためのガス吐出口8aと、ガスの排出口9と、前記支持体6を同一方向に回転させる手段とを具備することを特徴とし、前記加熱する手段が高周波誘導加熱であることが好ましい。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】 電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置を実現する。

【解決手段】 本発明の化合物半導体装置は、GaAs等の第1の化合物半導体層上に、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にない、即ちタイプII構造のバンド構造を有する属元素と6属元素の化合物からなるアモルファス層、例えばアモルファスGaS層(a−GaS層)を有するものである。

(もっと読む)

1,501 - 1,519 / 1,519

[ Back to top ]