Fターム[5F045AD15]の内容

気相成長(金属層を除く) (114,827) | 成膜条件−成膜温度 (8,040) | 1100≦T<1200℃ (776)

Fターム[5F045AD15]に分類される特許

121 - 140 / 776

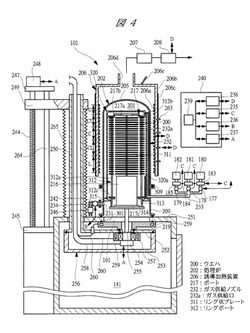

基板処理装置および半導体装置の製造方法

【課題】一度に処理できる基板の枚数を増加させたコールドウォール型の基板処理装置および半導体装置の製造方法を提供する。

【解決手段】処理炉202内に複数のウエハ200を積載したボート217を配置し、該ボート217の外周側に、リング状に形成されたリング状プレート311をリングボート312により支持して、前記ウエハ200の積載方向に複数並べて配置する。前記リング状プレート311を誘導加熱装置206で誘導加熱し、その輻射熱により前記ウエハ200を外周縁全体から加熱する。前記リング状プレート311の外周側にガス供給ノズル232を配置し、該ガス供給ノズル232のガス供給口232aから吐出されたガスを、隣り合う複数の前記リング状プレート311の間の隙間部分を通して前記ウエハ200に供給する。

(もっと読む)

半導体基板の製造方法

【課題】トレンチをエピタキシャル膜にて埋め込んで半導体基板を製造する上においてトレンチ開口部の塞がりの抑制と成長速度の向上の両立を図ることができる半導体基板の製造方法を提供する。

【解決手段】n+シリコン基板1の上に形成したn型エピタキシャル膜2に、複数のトレンチ4を、トレンチ幅Wtよりも、隣接するトレンチ4間の間隔Ltを大きく形成する。トレンチ4内を含めたエピタキシャル膜2上に、エピタキシャル膜2の不純物濃度よりも高濃度なp型エピタキシャル膜23を、少なくともトレンチ4の埋め込みの最終工程において、p型エピタキシャル膜23の成膜のために供給するガスとして、シリコンソースガスとハロゲン化物ガスとの混合ガスを用いて成膜し、トレンチ4の内部をp型エピタキシャル膜23で埋め込む。

(もっと読む)

III族窒化物半導体積層ウェハ及びIII族窒化物半導体デバイス

【課題】Alを含むIII族窒化物系半導体からなるチャネル層を備え、二次元電子ガスの移動度を高め電流特性を向上させることが可能なIII族窒化物半導体デバイス、及び該III族窒化物半導体デバイスの作製に用いられるIII族窒化物半導体積層ウェハを提供する。

【解決手段】III族窒化物半導体積層ウェハ10は、AlXGa1−XN(0<X≦1)からなる基板27と、Alを含むIII族窒化物系半導体からなり基板27上に設けられた第1のAlGaN層13と、第1のAlGaN層13上に設けられ、第1のAlGaN層13よりバンドギャップが大きいIII族窒化物系半導体からなる第2のAlGaN層15とを備える。第1のAlGaN層13の(0002)面及び(10−12)面におけるX線ロッキングカーブの半値幅は、1000[arcsec]未満である。

(もっと読む)

半導体素子の製造方法

【課題】本発明の実施形態は、ドライエッチングされた基板の表面に、良好な結晶性を有する窒化物半導体を形成することができる半導体素子の製造方法を提供する。

【解決手段】実施形態は、ドライエッチングにより処理された基板の表面をハロゲン元素を含む雰囲気中で熱処理し、前記熱処理した前記基板の前記表面に窒化物半導体層を形成することを特徴とする半導体素子の製造方法を提供する。

(もっと読む)

シリコンエピタキシャルウェーハおよびシリコンエピタキシャルウェーハの製造方法

【課題】ゲッタリング能力が高く、かつシリコンエピタキシャル層の最表面部の酸素濃度が極めて低いシリコンエピタキシャルウェーハを提供する。

【解決手段】酸素濃度が7ppma(JEIDA)以上のシリコン単結晶基板の主表面上にエピタキシャル層が形成されたシリコンエピタキシャルウェーハであって、該シリコンエピタキシャルウェーハは2層以上の炭素イオン注入層を有し、かつ前記シリコンエピタキシャル層の最表面部は酸素濃度が5ppma(JEIDA)以下であることを特徴とするシリコンエピタキシャルウェーハ。

(もっと読む)

化合物半導体の製造方法

【課題】大面積化が容易で且つ廉価なシリコンからなる基板に、残留応力が少なく且つ高品質の化合物半導体を形成する製造方法を提供する。

【解決手段】シリコン基板101の表面にシリコン酸化膜を形成し、その後、前記シリコン酸化膜よりも下層側の領域にイオン注入を行い、次いで熱処理して、イオン注入された単結晶のシリコンからなる下地層102を形成する。続いて、前記シリコン酸化膜を除去することにより下地層102を露出させる。その後、下地層102の上にAlNバッファ層103,AlGaNバッファ層104,およびGaN層105を形成する。

(もっと読む)

半導体製造方法

【課題】ウェーハ成膜後の降温時におけるスリップ発生を抑え、歩留り、信頼性の向上を図ることが可能な半導体製造方法を提供する。

【解決手段】反応室内にウェーハを搬入し、支持部材上に載置し、ウェーハの表面に、ソースガスを含むプロセスガスを供給し、ウェーハを第1の回転数で回転させながら、ヒータの出力を制御して所定温度に加熱することにより、ウェーハの表面に成膜を行い、ソースガスの供給を止め、ウェーハの回転数を、ウェーハのオフセットバランスを保持可能な第2の回転数に降下させるとともに、ヒータの出力を止め、第2の回転数で回転させながらウェーハを降温させる。

(もっと読む)

化合物半導体基板

【課題】Si単結晶基板を用いた化合物半導体基板において、化合物半導体基板の機械強度低下と熱伝導率低下を、Si単結晶基板のドーパント濃度制御で低減する。

【解決手段】Si単結晶基板上に中間層とデバイス活性層を備えた化合物半導体基板で、Si単結晶基板は、中間層側の一主面の表面から厚さ方向に向かってドーパント濃度が1×1019atoms/cm3以上1×1021atoms/cm3以下である領域1と、ドーパント濃度が連続的に減少する遷移領域1と、ドーパント濃度が1×1012atoms/cm3以上5×1017atoms/cm3以下である領域2と、ドーパント濃度が連続的に増加する遷移領域2と、ドーパント濃度が1×1019atoms/cm3以上1×1021atoms/cm3以下である領域3とからなる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

エピタキシャルウェーハの製造方法及びエピタキシャル成長装置

【課題】 本発明は、膜厚分布の偏りを解消し、均一な膜厚のエピタキシャル膜を形成させることができるエピタキシャルウェーハの製造方法及びエピタキシャル成長装置を提供する。

【解決手段】 基板載置台と該基板載置台に載置された基板とを回転させ、前記基板の主面上に原料ガスを流通させることにより、前記基板主面上にエピタキシャル膜を形成させるエピタキシャルウェーハの製造方法において、前記基板載置台の回転方向の位置に応じて、膜厚制御パラメータを変化させて前記エピタキシャル膜を形成させることを特徴とするエピタキシャルウェーハの製造方法。

(もっと読む)

成膜装置および成膜方法

【課題】反応ガスの気流を基板上に効率よく集めて、エピタキシャル膜の成長速度を増大させることのできる成膜装置および成膜方法を提供する。

【解決手段】成膜装置100は、チャンバ1と、チャンバ1の上部に設けられて反応ガス25をチャンバ1内に供給する供給部4と、チャンバ1内に設けられた中空筒状のライナ2と、ライナ2内に設けられて半導体基板6が載置されるサセプタ7と、サセプタ7を支持する回転筒23とを有する。回転筒23の回転によってサセプタ7を回転させながら、半導体基板6上に所定の膜が成膜される。ライナ2は、サセプタ7の周縁部上部を包囲するとともに、サセプタ7と一緒に回転するよう構成されている。

(もっと読む)

半導体基板の製造方法および発光素子

【課題】 半導体の結晶性を向上させることが可能な半導体基板の製造方法を提供する。

【解決手段】 本発明の半導体基板の製造方法は、単結晶基板2の上に単結晶基板2を覆うように半導体層を結晶成長させた半導体基板の製造方法であって、平坦な上面4Aを有する複数の突起4が第1主面2Aに設けられた単結晶基板2を準備する工程と、複数の突起4のうち、上面4Aから半導体層3を結晶成長させるものを第1突起4aとし、第1突起4a同士の間に位置する、上面4Aに半導体層3を結晶成長させないものを第2突起4bとして、第2突起4bの上面4Aを被覆するように実質的に半導体層3が結晶成長しないマスク層5を形成する工程と、第1突起4aの上面4Aからそれぞれ第2突起4bの上面4Aのマスク層5を越えて単結晶基板2を覆うように半導体層3を結晶成長させる工程とを有する。そのため、単結晶基板2上に成長させる半導体層3の単結晶基板2に対する平坦性を向上させることができ、半導体層3の結晶性を向上させることができる。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法およびシリコンエピタキシャルウェーハ

【課題】{110}面からの傾斜角度が小さくてもヘイズレベルが良好で、かつシリコン単結晶エピタキシャル層の層厚均一性も良好であり、更に表面欠陥の少ないシリコンエピタキシャルウェーハの製造方法を提供する。

【解決手段】シリコン単結晶基板の主表面上にシリコン単結晶エピタキシャル層を気相成長させるシリコンエピタキシャルウェーハの製造方法であって、前記シリコン単結晶基板として、主表面が{110}面または{110}面からのオフアングル角度が0.5度未満のものを用い、かつ前記気相成長工程では、前記シリコン単結晶基板温度を1170℃〜1190℃として気相成長することを特徴とするシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

半導体基板およびその製造方法

【課題】大面積化が可能な非極性基板およびその製造方法を提供する。

【解決手段】この半導体基板の製造方法は、サファイア基板10上に、GaN層11と、AlXGa(1−X)N(0<X≦1)層12とが交互に積層された半導体成長層20を形成する工程と、半導体成長層20を、半導体成長層20の成長面と交差する方向に沿って分割することにより、GaN層11からなる第1領域11aとAlXGa(1−X)N(0<X≦1)層12からなる第2領域12aとが縞状に配置された非極性面からなる主表面(切り出し面100a)を有する半導体基板100を形成する工程とを備える。

(もっと読む)

窒化物半導体発光素子

【課題】容易なプロセスで作製することができ、かつ、曲線光導波路の光導波ロスを低減する構造を有する窒化物半導体発光素子を提供する。

【解決手段】段差101bを有する基板101と、基板上に積層された、n型クラッド層102、活性層104およびp型クラッド層107を有する積層構造体とを備え、積層構造体は、曲線の光導波路である曲線光導波路11を含む光導波路部10を有し、曲線光導波路11の近傍であって曲線光導波路11の曲線の外側領域は、段差101bの上方に形成されている。

(もっと読む)

基板処理装置および基板処理方法

【課題】成膜処理する基板の歩留まりを向上できる技術を提供する。

【解決手段】ガス供給ノズル2321aのクリーニング工程において、ガス供給ノズル2321aからはエッチングガスEGが放出されるが、ガス供給ノズル2321aとは別のガス供給ノズル2321bから希釈ガスを放出している。この結果、インナーチューブ230内の処理室201内へ放出されたエッチングガスEGが処理室201内に配置されたウェハ200へ到達することを抑制できる。

(もっと読む)

窒化物半導体薄膜およびその成長方法

【課題】従来よりも原子レベルで平坦な表面を有する窒化物半導体薄膜及びその成長方法を提供すること。

【解決手段】ミスカットを有するGaN基板101のステップフロー成長(第1の成長工程)により制限領域102内に形成されたテラス202に、第1の成長工程よりも低い基板温度である第2の設定値T2でTMG又はTEGを供給する。これにより、テラス202の上にGaNの2次元核301が発生するが(図3(a)参照)、発生する2次元核301の個数が1個以上100個以下発生するだけの時間だけこの第2の成長工程を行う。次に、基板温度をT2よりも高い第3の設定値T3にする(第3の成長工程)。これにより、複数の2次元核301が横方向成長して1分子層の厚さの連続的なGaN薄膜302となる(図3(b)参照)。第2と第3の工程を交互に繰り返すことにより、2分子層以上の厚さのGaN薄膜303を成長可能である(図3(c)参照)。

(もっと読む)

気相成長方法

【課題】成長条件とを駆使し、基板上への成長膜厚を均一にする方法を提供する。

【解決手段】チャンバ120内に、支持台110上に載置された基板101が収容され、この基板101上に成膜するためのガスを供給する第1の流路及びガスを排気する第2の流路が接続された気相成長装置を用い、基板上に半導体層を気相成長する際に、成膜するための反応ガス及びキャリアガスの流量と濃度、チャンバ内の真空度、基板温度及び基板を回転する回転速度を制御して、半導体層の膜厚を均一にする。

(もっと読む)

III族窒化物結晶の成長方法

【課題】複数のタイル基板を用いて主表面におけるピットの発生が少ない大型のIII族窒化物結晶を成長させるIII族窒化物結晶の成長方法を提供する。

【解決手段】本III族窒化物結晶の成長方法は、平面充填ができる三角形および凸四角形のいずれかの形状である主表面10mを有するタイル基板10を複数準備する工程と、タイル基板10の頂点部が互いに向かい合う任意の点において互いに向かい合う頂点部の数が3以下であるように、複数のタイル基板10を平面充填させて配置する工程と、配置された複数のタイル基板10の主表面10m上にIII族窒化物結晶20を成長させる工程と、を備える。

(もっと読む)

半導体装置

【課題】ピンチオフ特性を改善することが可能な半導体装置を提供することを目的とする。

【解決手段】本発明は、SiC基板10上に設けられ、アクセプタ濃度(Na)がドナー濃度(Nd)以上の濃度であるAlGaNバッファ層18と、AlGaNバッファ層18上に設けられたGaN電子走行層14と、GaN電子走行層14上に設けられ、GaNよりもバンドギャップが大きいAlGaN電子供給層16と、を有する半導体装置である。

(もっと読む)

121 - 140 / 776

[ Back to top ]