Fターム[5F045AF16]の内容

気相成長(金属層を除く) (114,827) | 被成膜面の組成、基板の特徴、ダミー基板、マスク (7,328) | 基板の物性 (87)

Fターム[5F045AF16]の下位に属するFターム

酸素濃度 (24)

Fターム[5F045AF16]に分類される特許

21 - 40 / 63

単結晶基板、その製造方法、当該単結晶基板上に形成してなる半導体薄膜、および半導体構造

【課題】窒化インジウム(InN)を基としたバンドギャップEgが0.7〜1.05eVをもつIn1-(x+y)GaxAlyN(x≧0、y≧0、かつx+y≦0.35)単結晶薄膜と良好に格子整合する単結晶基板、その製造方法、当該単結晶基板上に形成してなる半導体薄膜、および半導体構造を提供する。

【解決手段】窒化インジウム(InN)を基とするIn1-(x+y)GaxAlyN薄膜を成長させる単結晶基板は、stillwellite型構造を持つ三方晶系に属する化学式REBGeO5(REは希土類元素)で標記される単結晶からなり、結晶学的方位{0001}を基板面とする。前記単結晶基板は、1000℃以上に加熱して形成した焼結体を原料として溶融し、必要に応じて、酸素雰囲気下あるいは不活性ガス雰囲気下で融液から単結晶を育成した後、結晶学的方位{0001}を基板面として切り出すことにより製造される。

(もっと読む)

エピタキシャルウェハ及びその製造方法

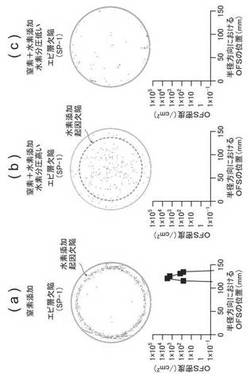

【課題】水素添加した場合のシリコンサブストレートウェハのボイドから発生するエピタキシャル層欠陥を抑制・防止する方法を提供する。

【解決手段】チョクラルスキー法により、水素、および窒素をシリコン融液に添加し、窒素濃度が3×1013atoms/cm3以上3×1014atoms/cm3以下であるシリコン結晶を引き上げる工程と、シリコン結晶を加工してシリコンサブストレートを作製し、シリコンサブストレートの表面にエピタキシャル層を形成する工程と、を含む。

(もっと読む)

III族窒化物半導体基板、エピタキシャル基板及び半導体デバイス

【課題】発光強度及び歩留を高度に両立することが可能なIII族窒化物半導体基板、エピタキシャル基板及び半導体デバイスを提供する。

【解決手段】半導体デバイス100では、S換算で30×1010個/cm2〜2000×1010個/cm2の硫化物、及び、O換算で2at%〜20at%の酸化物が表面層12に存在することにより、エピタキシャル層22とIII族窒化物半導体基板10との界面においてCがパイルアップすることを抑制できる。このようにCのパイルアップを抑制することで、エピタキシャル層22とIII族窒化物半導体基板10との界面における高抵抗層の形成が抑制される。これにより、エピタキシャル層22とIII族窒化物半導体基板10との界面の電気抵抗を低減することができると共に、エピタキシャル層22の結晶品質を向上させることができる。したがって、半導体デバイス100の発光強度及び歩留を向上させることができる。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】複数種類の面方位のYAG(Y3Al5O12)のいずれにも簡易な工程でIII族窒化物半導体層を形成する半導体素子の製造方法の提供。

【解決手段】半導体素子10において、YAG基板12は、面方位(100)、(110)、(111)のいずれかの単結晶基板として形成される。半導体素子10を製造する場合、まずYAG基板上にTMAlガスを供給し、III族元素であるアルミニウムにより核形成層18を形成する。次に核形成層18の表面にNH3ガスを供給して核形成層18の表面をV族化してAlNからなるIII−V族化合物層24を形成する。次にIII−V族化合物層24上にTMAlガスとNH3ガスとの混合ガスを供給してIII−V族化合物層20を形成する。最後にIII−V族化合物層20上にIII族窒化物半導体層16を成長結晶させる。

(もっと読む)

薄厚化デバイス素子用シリコンウェーハの製造方法

【課題】薄厚化デバイス素子用のシリコンウェーハをその有利な製造方法に併せて提供する。

【解決手段】CZ法により、前記炭素化合物成長層の炭素濃度が0.5×1016〜10×1016atoms/cm3 、酸素濃度が1.0×1018〜1.0×1019atoms/cm3 となるように単結晶を引き上げる引き上げ工程と、

引き上げた単結晶をスライスしてシリコンウェーハとするウェーハ加工工程と、

炭素と酸素による複合体を形成しゲッタリングシンクを形成する600〜800℃で0.25〜3時間のプレアニール工程と、

前記析出熱処理工程後にシリコンウェーハ表面にシリコンエピタキシャル層を形成するエピタキシャル工程と、

最高到達温度が900℃以下で30秒以下の熱処理とされるデバイスプロセス熱処理工程と、

を有する。

(もっと読む)

酸化亜鉛系基板及び酸化亜鉛系基板の製造方法

【課題】成長させた酸化亜鉛系半導体の不純物濃度を低減できる酸化亜鉛系基板を提供する。

【解決手段】酸化亜鉛系基板2は、IV族元素であるSi、C、Ge、Sn及びPbの不純物濃度が、1×1017cm−3以下の条件を満たす。より好ましくは、酸化亜鉛系基板2は、I族元素であるLi、Na、K、Rb及びFrの不純物濃度が、1×1016cm−3以下の条件を満たす。

(もっと読む)

電子デバイス用エピタキシャル基板およびその製造方法

【課題】横方向リーク電流の低減と横方向耐圧特性を両立させ、縦方向耐圧を向上させる電子デバイス用エピタキシャル基板を提供する。

【解決手段】Si基板1上のバッファ3上にIII族窒化物層をエピタキシャル成長させた、チャネル層4aおよび電子供給層4bを有する主積層体4を具え、前記バッファは、Si基板と接する初期成長層5および初期成長層上の超格子多層構造からなる超格子積層体6を有し、初期成長層はAlN材料からなり、前記超格子積層体はBa1Alb1Gac1Ind1N材料からなる第1層6aおよび第1層とはバンドギャップの異なるBa2Alb2Gac2Ind2N材料からなる第2層6bを積層してなり、前記超格子積層体と、前記主積層体を構成するチャネル層のバッファ側の部分は、C濃度が1×1018/cm3以上であり、チャネル層の電子供給層側の部分は、C濃度が4×1016/cm3以下であることを特徴とする。

(もっと読む)

化合物半導体エピタキシャルウェハおよびその製造方法

【課題】窒化物半導体からなる電子デバイスにおいてバッファ層に生じるリーク電流を抑制できる窒化物半導体エピタキシャルウェハを提供する。

【解決手段】化合物半導体エピタキシャルウェハは、単結晶基板101と、前記単結晶基板上にエピタキシャル成長された核生成層102と、前記核生成層の上に成長された窒化物半導体の単層あるいは複数層からなるバッファ層103と、前記バッファ層の上にエピタキシャル成長された窒化物半導体のチャネル層104と、前記チャネル層の上にエピタキシャル成長された窒化物半導体のキャリヤ供給層105とから成り、かつ前記核生成層からチャネル層までの合計の膜厚が1μm以下であること。

(もっと読む)

半導体ウエハの製造方法及び半導体ウエハ

【課題】格子不整合系基板を使用しながら、高品質な単結晶窒化物半導体の結晶成長を実現する半導体ウエハの製造方法を提供する。

【解決手段】半導体基板101の表面にグラフェン層110を設ける工程と、グラフェン層110の炭素原子の配列を示すハニカム構造の中心に、単結晶半導体層の結晶を構成する一の元素を吸着させる工程と、この一の元素に前記結晶を構成する当該元素とは異なる他の元素を結合させ、前記結晶の第1層114を形成する工程と、前記第1層の表面にさらに所定の層数の前記結晶半導体層を結晶成長する工程を備える。

(もっと読む)

化合物半導体エピタキシャル基板

【課題】電流増幅率を向上させ、基板種に影響されず良好な特性のデバイスを製造できる化合物半導体エピタキシャル基板を提供すること。

【解決手段】GaAs基板2上に、サブコレクタ層41、コレクタ層42、ベース層43、エミッタ層44、エミッタコンタクト層46、47がこの順序で形成されている化合物半導体エピタキシャル基板1において、GaAs基板2とサブコレクタ層41との間に形成されるバッファ層3を酸素を含むAlx Ga1-x As (0≦X≦1)層とし、酸素を含むバッファ層3によりGaAs基板2に存在する欠陥の伝播を抑制し、ベース層43の結晶性を基板種によらず安定かつ良好にできるようにした。

(もっと読む)

窒化物半導体用形成用基板およびその製造方法

【課題】シリコン基板上への窒化物半導体薄膜の形成時における、熱膨張係数差から生じる熱応力および多孔質シリコンの構造変化に起因したピットの問題を解消し、更に該被膜に生じる反りと応力を低減できる、窒化物半導体薄膜形成に好適な窒化物半導体薄膜形成用基板を提供。

【解決手段】シリコン単結晶基体上に、異なる多孔質構造を有するシリコン層を組み合わせ設けたものを基板とし、更に、その上にシリコンエピタキシャル膜層を設けた窒化物半導体形成用基板。

(もっと読む)

シリコンウェーハの製造方法、エピタキシャルウェーハの製造方法、および固体撮像素子の製造方法

【課題】ゲッタリングシンクを短時間で容易に形成できるとともに、ゲッタリングシンクの形成時に重金属汚染の懸念がない固体撮像素子用エピタキシャルウェーハの製造方法を提供する。

【解決手段】多光子吸収工程によってゲッタリングシンク4を形成した後で、シリコンウェーハ2を鏡面研磨する(ポリッシング工程:図4(b)参照)。シリコンウェーハ2を鏡面研磨するポリッシング工程によって、前工程である多光子吸収工程においてレーザビームの照射により生じたシリコンウェーハ2の一面2aの微細な傷(アブレーション)は完全に除去される(図4(b)参照)。

(もっと読む)

III族窒化物半導体素子、エピタキシャル基板、及びIII族窒化物半導体素子を作製する方法

【課題】良好な表面モフォロジを有する窒化ガリウム系半導体膜を含むIII族窒化物半導体素子を提供する。

【解決手段】III族窒化物半導体光素子11aは、III族窒化物半導体支持体13、GaN系半導体領域15、活性層17及びGaN系半導体領域19を備える。III族窒化物半導体支持体13の主面13aは、基準軸Cxに直交する基準平面Scに対して傾斜する非極性を示しており、基準軸CxはIII族窒化物半導体のc軸方向に延びる。GaN系半導体領域15は半極性主面上13aに設けられる。GaN系半導体領域15のGaN系半導体層21は例えばn型GaN系半導体からなり、n型GaN系半導体にはシリコンが添加されている。GaN系半導体層23の酸素濃度が5×1016cm−3以上であるとき、GaN系半導体層23の主面上に引き続き成長される活性層17の結晶品質が良好になる。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法およびシリコンエピタキシャルウェーハ

【課題】N型の超低抵抗率(2mΩ・cm以下)のシリコン単結晶基板を用いた、ミスフィット転位の発生を抑制することができるシリコンエピタキシャルウェーハの製造方法とシリコンエピタキシャルウェーハを提供する。

【解決手段】少なくとも、チョクラルスキー法によって育成したシリコン単結晶棒を加工してシリコン単結晶基板を作製し、該シリコン単結晶基板の主表面上にシリコン薄膜を気相成長させるシリコンエピタキシャルウェーハの製造方法であって、前記チョクラルスキー法で前記シリコン単結晶棒を育成する際に、該シリコン単結晶棒に抵抗率が2mΩ・cm以下となるように燐をドープし、かつ前記シリコン薄膜の気相成長前に、前記シリコン単結晶基板に対して前記燐の拡散長が0.24μm以上となるように時間と温度を調整した熱処理を行うことを特徴とするシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

シリコンエピタキシャルウェーハおよびシリコンエピタキシャルウェーハの製造方法

【課題】シリコン薄膜にミスフィット転位が発生しにくい超低抵抗率のシリコンエピタキシャルウェーハとこれを低コストで製造する方法を提供する。

【解決手段】少なくとも、シリコン単結晶基板と、該シリコン単結晶基板の主表面上に気相成長によって形成されたシリコン薄膜からなるシリコンエピタキシャルウェーハであって、前記シリコン単結晶基板は、抵抗率が2mΩ・cm以下で、かつ燐及びゲルマニウムが、前記燐の濃度〔P〕と前記ゲルマニウムの濃度〔Ge〕の比〔Ge〕/〔P〕が、0.55≦〔Ge〕/〔P〕<1.5となるようにドープされたものであることを特徴とするシリコンエピタキシャルウェーハ。

(もっと読む)

窒化ガリウム系化合物半導体基板及びその製造方法、並びに半導体素子

【課題】半導体基板として良好な品質を持ち、且つその表面が高抵抗化されたGaN系化合物半導体基板を提供する。

【解決手段】GaN基板1は、半導体結晶をエピタキシャル成長させるための主面10aを有する基板であって、主面10aの少なくとも一部の領域12にHやHe、Arといった所定のイオンが注入されており、該少なくとも一部の領域12は主面10a全域の70%以上を占めており、該領域12の表面におけるシート抵抗値の平均は1×104Ω/□以上である。

(もっと読む)

エピタキシャル成長用内部改質基板及びそれを用いて作製される結晶成膜体、デバイス、バルク基板及びそれらの製造方法

【課題】窒化物半導体層のエピタキシャル成長に用いるサファイア基板において、効率良く基板の反り形状及び/又は反り量を精密に制御することができ、且つ、成膜中に生じる基板の反りを抑制、それを用いて作製される窒化物半導体層成膜体、窒化物半導体デバイス、窒化物半導体バルク基板及びそれらの製造方法を提供する。

【解決手段】サファイア基板の内部に、前記サファイア基板の研磨面側を通してパルスレーザを集光し、走査し、前記パルスレーザによる多光子吸収を利用して改質領域パターンを形成し、サファイア基板の反り形状及び/又は反り量を制御する。本発明により得られたサファイア基板を用いて窒化物半導体層を形成すると、成膜中の基板の反りを抑制し、基板の反り挙動を小さくすることができるため、膜の品質及び均一性が向上し、窒化物半導体デバイスの品質及び歩留まりを向上させることができる。

(もっと読む)

III族窒化物結晶の成長方法

【課題】溶液法により得られるIII族窒化物結晶基板を用いたHVPE(ハイドライド気相成長)法による大型のIII族窒化物結晶の成長方法を提供する。

【解決手段】アルカリ金属元素の濃度が1.0×1018cm-3未満の第1のIII族窒化物結晶10を準備する工程と、HVPE法により、1100℃より高い雰囲気温度で、第1のIII族窒結晶10の主面10m上に、第2のIII族窒化物結晶20を成長させる工程と、を備える。

(もっと読む)

窒化物系半導体基板及び半導体装置

【課題】充分な導電性を確保しつつ、高い熱伝導率と高い電子移動度を有する窒化物系半導体基板及び半導体装置を提供する。

【解決手段】直径25mm以上、かつ厚さ250μm以上の寸法を有する窒化物系半導体からなる基板であって、n型のキャリア濃度n[cm-3]が1.2×1018cm-3以上3×1019cm-3以下であり、かつ電子移動度μ[cm2/Vs]が、logeμ=17.7−0.288logenで表される値よりも大きく、かつlogeμ=18.5−0.288logenで表される値よりも小さい窒化物系半導体基板。また、その窒化物系半導体基板の上に窒化物系半導体をエピタキシャル成長させて半導体装置とする。

(もっと読む)

III族窒化物半導体電子デバイス、III族窒化物半導体電子デバイスを作製する方法、及びIII族窒化物半導体エピタキシャルウエハ

【課題】リーク電流を低減できる構造を有するIII族窒化物半導体電子デバイスを提供する。

【解決手段】積層体11は基板13及びIII族窒化物半導体エピタキシャル膜15を含む。基板13は、1×1018cm−3を越えるキャリア濃度を有するIII族窒化物半導体からなる。エピタキシャル構造物15はIII族窒化物半導体エピタキシャル膜17を含む。基板13の第1の面13aはc軸の方向に延びる軸Cxに対して5度より大きい角度θで傾斜している。法線ベクトルVN及びc軸ベクトルVCとは角度θを成す。III族窒化物半導体エピタキシャル膜17は第1の面13aの法線方向に順に配置された第1、第2及び第3の領域17a、17b、17cを含む。第3の領域17cの転位密度は第1の領域17aの転位密度よりも小さい。第2の領域17bの転位密度は基板13の転位密度よりも小さい。

(もっと読む)

21 - 40 / 63

[ Back to top ]