Fターム[5F045BB16]の内容

気相成長(金属層を除く) (114,827) | 目的 (9,309) | 電気的特性の向上・膜損傷の回避 (910)

Fターム[5F045BB16]に分類される特許

81 - 100 / 910

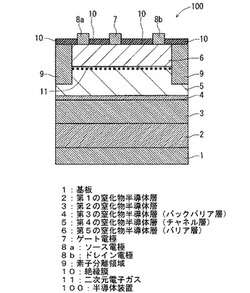

半導体装置およびその製造方法

【課題】電子移動度の低下が抑制され、かつ二次元電子ガスの閉じ込めが高められた半導体装置およびその製造方法を提供する。

【解決手段】AlaInbGa1-(a+b)N(0≦a,b≦1、0≦a+b≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが大きい第1の窒化物半導体層2、AlcIndGa1-(c+d)N(0≦c,d≦1、0≦c+d≦1)から成る第2の窒化物半導体層3、IneGa1-eN(0<e≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが小さいバックバリア層4、AlfIngGa1-(f+g)N(0≦f,g≦1、0≦f+g≦1)から成り、第2の窒化物半導体層3とバンドギャップが等しいチャネル層5、AlhIniGa1-(h+i)N(0≦h,i≦1、0≦h+i≦1)から成り、チャネル層5よりもバンドギャップが大きいバリア層6を、この順に基板1に積層する。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】形成されるシリコン酸化膜の誘電率、又は成膜レートを、成膜条件を変更することにより制御することができる基板処理装置や半導体装置の製造方法を提供する。

【解決手段】基板を処理する処理室と、非シロキサン材料ガスを処理室内へ供給する材料ガス供給部と、酸素含有ガスを処理室内へ供給する酸素含有ガス供給部と、処理室内へ供給されたガスを励起する励起部と、制御部とを備え、材料ガス供給部及び酸素含有ガス供給部から処理室内へ、それぞれ非シロキサン材料ガスと酸素含有ガスを供給する際に、非シロキサン材料ガスと酸素含有ガスの合計流量に対する酸素含有ガスの流量比を、非シロキサン材料ガス分子中のシリコン原子と酸素含有ガス分子中の酸素原子の合計数に対する酸素含有ガス分子中の酸素原子の比が、0.3以上で0.8以下とするとともに、処理室内へ供給されたガスを励起するよう基板処理装置を構成する。

(もっと読む)

半導体装置

【課題】窒化物半導体により、反転型のHEMTが構成された半導体装置において、半導体装置の形成を容易としつつ2DEGを効果的に形成する。

【解決手段】窒化物半導体からなる下地層15の(0001)面上に、窒化物半導体からなる電子供給層17、窒化物半導体からなる電子走行層19の順に積層され、電子走行層19における電子供給層17と反対の面上に、ゲート電極21、ソース電極23、及びドレイン電極25が設けられている。そして、電子走行層19における電子供給層17側に、二次元電子ガスが形成される。このような反転型のHEMTが構成された半導体装置10において、分極の正方向を[0001]方向とした場合、電子供給層17の自発分極とピエゾ分極の和P2が、電子走行層19の自発分極とピエゾ分極の和P1よりも大きくなっている。

(もっと読む)

プラズマCVD装置及びシリコン系薄膜の製造方法

【課題】欠陥が低く、高次シランの混入のない高品質なアモルファスシリコン薄膜を得ることができるプラズマCVD装置、及シリコン系薄膜の製造方法を提供する。

【解決手段】平行平板型プラズマCVD装置1には,放電電極3に凹部7が設けられ,該放電電極と接地電極10との間に,アースカバー8が設けられ,このアースカバーには放電電極に設けられている凹部に相対向するように,貫通孔9が設けられている。また、薄膜の製造に当たっては、前述の装置で、真空容器を減圧下に保持し、真空容器内に該放電電極に設けられている該凹部の壁面より少なくとも珪素を含む原料ガスを凹部内に供給し、該放電電極に高周波電力を印加して、該凹部中において該原料ガスをプラズマ化し、該凹部中にプラズマを局在化させ,該プラズマ化した原料ガス中に含まれるSiH3ラジカルを基板上に到達させ、成膜する事により、前記課題を解決出来る。

(もっと読む)

成膜方法、成膜装置および記憶媒体

【課題】DRAMキャパシタの誘電体膜に求められる高誘電率化および低リーク電流化を両立させることができる、酸化ジルコニウム膜を含む誘電体膜の成膜方法および成膜装置を提供すること。

【解決手段】 酸化ジルコニウム膜を含む誘電体膜を成膜する成膜方法は、シクロペンタジエニル環を構造中に含むZr化合物からなるジルコニウム原料と酸化剤とを供給して被処理基板上に酸化ジルコニウム膜を成膜する工程と、シクロペンタジエニル環を構造中に含むチタン化合物からなるチタン原料と酸化剤とを供給して前記酸化ジルコニウム膜の上に酸化チタン膜を成膜する工程とを有する。

(もっと読む)

窒化物半導体発光素子の製造方法

【課題】高性能の窒化物半導体発光素子を製造する方法を提供する。

【解決手段】基板上にn型窒化物半導体層を形成する工程と、n型窒化物半導体層上に発光層を形成する工程と、発光層上にp型窒化物半導体層を形成する工程と、p型窒化物半導体層を、酸素を含む雰囲気において、第1温度で熱処理する工程と、第1温度で熱処理したp型窒化物半導体層を、真空雰囲気において、第1温度よりも低い第2温度で熱処理する工程と、を含む窒化物半導体発光素子の製造方法である。

(もっと読む)

複合GaN基板およびその製造方法、ならびにIII族窒化物半導体デバイスおよびその製造方法

【課題】高特性かつ手頃な価格の複合GaN基板およびその製造方法ならびにIII族窒化物半導体デバイスおよびその製造方法を提供する。

【解決手段】本複合GaN基板1は、比抵抗が1Ωcm未満の導電性GaN基板10と、導電性GaN基板10上に配置された比抵抗が1×104Ωcm以上で厚さが5μm以上の半絶縁性GaN層20と、を含む。本III族窒化物半導体デバイス2は、上記の複合GaN基板1と、複合GaN基板1の半絶縁性GaN層20上に配置された少なくとも1層のIII族窒化物半導体層30と、を含む。

(もっと読む)

面発光型レーザ素子とその製造方法、面発光型レーザアレイ素子、光走査装置、ならびに画像形成装置

【課題】下部DBR反射鏡等を構成するAl組成の高いAlGaAs、AlAs等の層の側面からの酸化を防ぐ構造を有する面発光型レーザ技術の提供。

【解決手段】半導体基板の表面上に、下部反射鏡と活性層と電流狭窄層と上部反射鏡とをエピタキシャル成長により形成する半導体層形成工程(ステップS101)と、半導体層形成工程により形成された半導体膜の一部をエッチングすることによりメサ構造を形成するメサ構造形成工程(ステップS102)と、半導体層形成工程により形成された半導体膜を半導体基板の表面までエッチングすることにより素子分離溝を形成する素子分離溝形成工程(ステップS103)と、素子分離溝の壁面、メサ構造の上面および側面に半導体材料からなる再成長層を形成する再成長層形成工程(ステップS104)と、再成長層上に、絶縁体からなる保護膜を形成する保護膜形成工程(ステップS105)とを有する。

(もっと読む)

プラズマ処理方法、膜形成方法、半導体デバイスの製造方法及びプラズマ処理装置

【課題】得られる膜の品質を向上できると共にプラズマ処理が基板に及ぼす影響を低減できるプラズマ処理方法、膜形成方法、半導体デバイスの製造方法及びプラズマ処理装置を提供する。

【解決手段】本実施形態のプラズマ処理方法は、基板W上に吸着された第1層A1に対して、第1圧力P1下で第1プラズマ処理を施す工程と、第1プラズマ処理を施された第1層L1上に吸着された第2層A2に対して、第1圧力P1より低い第2圧力P2下で第2プラズマ処理を施す工程とを含む。

(もっと読む)

炭化珪素単結晶エピタキシャルウエハの製造方法

【課題】加工変質層の除去処理にかかる時間を減少させつつも、加工変質層に由来するエピタキシャル膜の欠陥の発生を抑制できる炭化珪素単結晶エピタキシャルウエハの製造方法を提供する。

【解決手段】炭化珪素単結晶エピタキシャルウエハの製造において、炭化珪素単結晶基板100を1600℃以上に加熱し、C/Si比が1.0以下となるように、原料ガスを供給し、エピタキシャル膜の成長速度を2.0μm/h以下にする。このとき、キャリアガスの流量を50slm以上にし、原料ガスとしてモノシランの流量を20sccm以下にし、成長装置の前記炭化珪素単結晶基板100が配置された空間の圧力を100mbar以上にすることにより、エピタキシャル膜の成長速度を2.0μm/h以下にすることができる。

(もっと読む)

窒化物半導体の積層構造およびその製造方法並びに窒化物半導体装置

【課題】窒化物半導体積層体の結晶欠陥密度が低減可能な窒化物半導体の積層構造およびその製造方法並びに窒化物半導体装置を提供する。

【解決手段】窒化物半導体の積層構造は、基板10、第1バッファ層12、第1結晶層14、第2バッファ層16、第2結晶層20とを備える。基板10には、段差部10dが形成されている。第1バッファ層12は、InAlGaNを含み、段差下面10bと段差側面10cとを覆う。第1結晶層14は、前記第1バッファ層12の上に設けられ、InAlGaNを含み、前記基板10の上面10aよりも上方に設けられた上面14aを有する。第2バッファ層16は、InAlGaNを含み、前記第1結晶層14の前記上面14aと前記基板10の前記上面10aとを連続して覆う。第2結晶層20は、前記第2バッファ層16を覆い、InAlGaNを含み、前記第1の面20aを有する。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの活性層に好適に用いられる非晶質酸化物の製造方法を提供する。

【解決手段】基板1上に、非晶質酸化物層2を形成する前に、基板1表面にオゾン雰囲気中で紫外線を照射したり、基板1表面にプラズマを照射したり、あるいは基板1表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物層2を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板1上に、非晶質酸化物層2を形成する後に、非晶質酸化物層2の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

半導体基板、半導体装置、および半導体基板の製造方法

【課題】GaN系半導体は、面方位が(111)のシリコン基板上にエピタキシャル成長される。GaNの格子定数と、とシリコン(111)面の格子定数の差が、約17%と大きいのでめ、成長されたGaNには1010cm−2を超える転位が導入される。転位により、GaNを用いたトランジスタのリーク電流が増大する。また、トランジスタの移動度が低下する。

【解決手段】シリコン基板と、シリコン基板の(150)面上に、エピタキシャル成長された窒化物半導体層と、を備える半導体基板を提供する。

(もっと読む)

エネルギー障壁を有するヘテロ接合トランジスタおよび関連する方法

【課題】チャネル内へのキャリアの閉じ込めを改善すること。

【解決手段】へテロ接合トランジスタは、III族窒化物を含むチャネル層14と、チャネル層の上のIII族窒化物を含む障壁層16と、チャネル層14が障壁層16とエネルギー障壁38との間にあるようにした、チャネル層14の上のインジウムを有するIII族窒化物の層を含むエネルギー障壁とを備えることができる。障壁層16は、チャネル層よりも大きなバンドギャップを有することができ、エネルギー障壁38のインジウム(In)の濃度はチャネル層14のインジウム(In)の濃度よりも高い可能性がある。

(もっと読む)

III族窒化物半導体電子デバイス、エピタキシャル基板、及びIII族窒化物半導体電子デバイスを作製する方法

【課題】半導体積層内の電流経路からゲート電極を隔てる半導体層を厚くできるIII族窒化物半導体電子デバイスを提供する。

【解決手段】第2の半導体層15は第1の半導体層13上に設けられる。ゲート電極17は第2の半導体層15の上に設けられる。第1の半導体層13は、AlXGa1−XN(0<X≦1)からなる半導体表面21aの上に設けられる。第2のIII族窒化物半導体材料のバンドギャップE15は第1のIII族窒化物半導体材料のバンドギャップE13より大きい。第1の半導体層13の第1のIII族窒化物半導体材料はAlXGa1−XNと異なり、第1の半導体層13は歪みを内包する。また、第2の半導体層15の厚さT15は、無歪みの第1のIII族窒化物半導体材料の組成と、第2のIII族窒化物半導体の組成により規定される臨界膜厚より大きい。また、第1の半導体層13は、歪みを内包すると共に、半導体表面21aのAlXGa1−XNの上において格子緩和している。

(もっと読む)

InNを含む半導体層の成膜方法および気相成長装置

【課題】結晶性、電気的特性、および光学特性等に優れたInNを含む半導体層を成膜する方法を提供する。

【解決手段】本発明のInNを含む半導体層の成膜方法は、プラズマで分解された水素原子と、In金属またはInを含む化合物からなるIn源とを反応させることによってIn水素化物を形成するステップと、プラズマで窒素を分解することによって原子状窒素を形成するステップと、In水素化物と原子状窒素とを反応させることによって、基板上にInNを含む半導体層を形成するステップとを含むことを特徴とする。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

半導体素子用のエピタキシャル基板、および半導体素子用エピタキシャル基板の製造方法

【課題】高耐電圧性を有するとともにp型不純物の拡散による結晶品質の劣化が好適に抑制された、半導体素子用のエピタキシャル基板を提供する。

【解決手段】(111)方位の単結晶シリコンである下地基板1の上に、前記下地基板の基板面に対し(0001)結晶面が略平行となるようにIII族窒化物層群を形成してなる半導体素子用のエピタキシャル基板10が、組成の相異なる第1単位層31と第2単位層32とを繰り返し交互に積層してなる組成変調層3と、組成変調層の上に形成され、Alを含むIII族窒化物からなる中間層5と、を含む単位構造体を複数積層してなるバッファ層8と、バッファ層の直上に形成されたチャネル層9aと、チャネル層の上に形成されたバリア層9bと、を備え、バッファ層に含まれる複数の前記中間層のうちの少なくとも1つにp型不純物が意図的に導入されてなり、隣接層に第1の層から拡散したp型不純物が存在する、ようにする。

(もっと読む)

パワー半導体素子

【課題】窒化物化合物半導体を用いたパワーダイオード、パワーMOSFET等のパワー

半導体素子について、クラックフリーで形成されて従来よりも厚い窒化物化合物半導体層

を使用して耐圧を向上することである。

【解決手段】シリコン基板1上に厚さ10μm以上の凸状に選択成長された窒化物化合物

半導体からなるキャリア移動層3と、キャリア移動層3上に形成された電極4とを有し、

1つのパワー半導体素子は1つのキャリア移動層3から構成されている。

(もっと読む)

窒化物半導体素子の製造方法

【課題】ドレインリーク電流を低減することが可能な窒化物半導体素子の製造方法を提供する。

【解決手段】ヘテロ電界効果トランジスタ1の製造方法は、ドリフト層20aを支持基板10上にエピタキシャル成長させる工程と、水素ガスをキャリアガスとして用いて、p型半導体層である電流ブロック層20bをドリフト層20a上に1000℃以上でエピタキシャル成長させる工程と、窒素ガス、アルゴンガス、ヘリウムガス及びネオンガスからなる群より選ばれる少なくとも一種のガスをキャリアガスとして用いて、コンタクト層20cを電流ブロック層20b上にエピタキシャル成長させる工程と、を備える。

(もっと読む)

81 - 100 / 910

[ Back to top ]