Fターム[5F045CA01]の内容

気相成長(金属層を除く) (114,827) | 半導体素子等への用途 (4,120) | バイポーラトランジスタ (218)

Fターム[5F045CA01]の下位に属するFターム

HBT(ヘテロバイポーラトランジスタ) (109)

Fターム[5F045CA01]に分類される特許

1 - 20 / 109

成膜方法および成膜装置

【課題】基板とそれを載置する冶具との間の貼り付きを防止する成膜方法および成膜装置を提供する。

【解決手段】成膜室であるチャンバ103内に配置された冶具であるサセプタ102上に基板101を載置し、サセプタ102を上部で支持する円筒部104aを備えた回転部104を回転させながら、ガス制御部140の制御によって、チャンバ103内へ原料ガス137を供給する。併せて、円筒部104aにパージガス151を供給し、パージガス151が基板101とサセプタ102の間から抜け出るようにすることによって、基板101の少なくとも一部がサセプタ102から浮いた状態で回転するようにし、基板101の上に所定の膜を形成する。

(もっと読む)

成膜装置および成膜方法

【課題】搬送室とチャンバの温度差にかかわらず、基板をサセプタ上の所定位置に載置することのできる成膜装置および成膜方法を提供する。

【解決手段】ロボットハンドで基板をチャンバの内部へ搬送し(S101)、基板支持部へ受け渡す(S102)。基板支持部を下降させて、サセプタの上に基板を載置する(S103)。基板を回転させながら温度測定を行う(S104)。放射温度計による測定結果と、エンコーダによる検出結果とを用いて、温度データと位置データを作成する(S105)。これらから基板の位置ずれ量を求めて(S106)、この位置ずれ量が許容値以下であるか否かを判定する(S107)。位置ずれ量が許容値より大きい場合には、搬送室内でロボットハンドの位置調整を行った後(S108)、次に成膜予定の基板をチャンバの内部へ搬送し、基板支持部を介してサセプタの上に載置する(S109)。

(もっと読む)

エピタキシャル成長装置

【課題】リフレクタからの熱線を調節してシリコン単結晶基板を面内均一に加熱し、膜厚が均一なエピタキシャル層を成長させることができる装置を提供することを目的とする。

【解決手段】サセプタの上下に各々配置され、放射状に円形に並べられた複数の棒状の単体ヒータを有するヒータと、上のヒータの上側及び前記下のヒータの下側に各々配置された上下のドーナツ状リフレクタとを備え、上下のドーナツ状リフレクタの少なくとも一つは、ヒータの熱放射を収束させる収束反射板部と熱放射を分散させる分散反射板部とを有し、収束反射板部は棒状の単体ヒータに沿って形成された円筒凹面を有し、かつ該円筒凹面はドーナツ状リフレクタの径方向で異なった曲率半径の断面の部分を有するものであるエピタキシャル成長装置。

(もっと読む)

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

キャリアライフタイムが改善された基板を製造する方法

【課題】得られるコーティングが0.5マイクロ秒〜1000マイクロ秒のキャリアライフタイムを有するように、シリコンカーバイドコーティングを基板上に堆積させる方法を提供する。

【解決手段】a.ジクロロシランガス、メチルハイドロジェンジクロロシランガス、ジメチルジクロロシランガス、及びそれらの混合物から選択されるクロロシランガスと、炭素含有ガスと、水素ガスとを含む混合ガスを、単結晶シリコンカーバイド基板を含有する反応チャンバ内に導入すること、及びb.1200℃より高いが1800℃より低い温度に基板を加熱すること、を含むが、但し、反応チャンバ内の圧力は10torr〜250torrの範囲に維持されるものとする。

(もっと読む)

薄膜処理方法

【課題】成膜処理の過程で形成される薄膜の処理方法を提供する。

【解決手段】反応室に配置されたサセプタ8の座ぐり部8aに基板7を載置し、反応室に反応ガスを導入して基板7の上にSiC膜301を形成する(第1の工程)。反応室にエッチングガスを導入し、基板7が取り除かれたサセプタ8を回転させながら、サセプタ8の上方からエッチングガスを流下させて、サセプタ8の座ぐり部8aからその周縁部8bに至る段差部8cに形成された反応ガスに起因するSiC膜301を除去する(第2の工程)。反応室にエッチングガスを導入し、サセプタ8の上に形成された反応ガスに起因するSiC膜301を除去する(第3の工程)。第1の工程と第2の工程を繰り返した後に第3の工程を行う。

(もっと読む)

成膜装置および成膜方法

【課題】反応ガスが滞留する空間を低減した成膜装置および成膜方法を提供する。

【解決手段】成膜装置100は、反応ガス4が供給されて成膜処理が行われるチャンバ1と、チャンバ1の内部に設けられた中空筒状のライナ2と、ライナ2の上方に設けられて反応ガスが透過するシャワープレート15とを有する。シャワープレート15がライナ2の上部開口部52を塞ぐ位置から上方に移動することにより、チャンバ1の壁に設けられた基板搬出入口47を介してチャンバ1の外部とライナ2の内部とが連通する。また、成膜装置100は、ライナ2の内部に設けられ、成膜処理が行われる基板7を支持して鉛直方向に移動させる基板支持部50と、基板搬出入口47を通じて反応室に出入するロボットハンド48とを有する。基板支持部50とロボットハンド48との間で基板7の受け渡しが行われる。

(もっと読む)

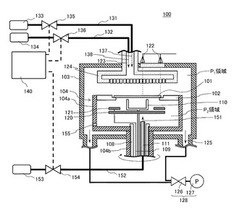

気相成長装置および気相成長方法

【課題】基板を加熱するヒータの劣化を抑えてヒータ寿命を低下させることのない気相成長装置および気相成長方法を提供する。

【解決手段】シリコンウェハ101を載置するサセプタ102を、回転部104の円筒部104aの上部で支持する。円筒部104aの内部のP2領域内には、シリコンウェハ101を下方側から加熱するヒータとして、インヒータ120とアウトヒータ121を配置する。そして、P2領域にはガス導入管111からパージガスを供給するとともに、シリコンウェハ101をサセプタ102上の所定位置から持ち上げ、回転部104の上方に配置するときには、パージガスの流量を増大させるようにする。

(もっと読む)

気相成長方法

【課題】エピタキシャル膜の形成に際し、半導体基板を支持するサセプタへの、原料ガスに起因する膜の付着を低減し、サセプタのエッチング処理の時間の低減する気相成長方法を提供する。

【解決手段】半導体基板であるシリコンウェハ101を支持するサセプタ102の表面の少なくとも一部をSiO2やSi3N4などの金属の酸化膜や窒化膜で被覆する。そして、サセプタ102上でシリコンウェハ101を加熱しながら、シリコンウェハ101上に原料ガスを供給し、サセプタ102上への原料ガスに起因する膜の付着を抑制して、シリコンウェハ101上にエピタキシャル膜を成長させるようにする。

(もっと読む)

エピタキシャルウエハおよびその製造方法、半導体装置およびその製造方法

【課題】本発明は、結晶欠陥が少なく、キャリア時定数が十分大きい高品質なエピタキシャルウエハの製造方法と、当該エピタキシャルウエハを用いた半導体装置の製造方法の提供を目的とする。

【解決手段】本発明のエピタキシャルウエハの製造方法は、(a)3×1018cm-3以下の不純物濃度を有するSiC基板12上に、1×1014cm-3以上1016cm-3台以下の不純物濃度を有するエピタキシャル層13をエピタキシャル成長により形成する工程と、(b)前記工程(a)により得られた構造のSiC基板12の側から、エピタキシャル層13のうち所定の厚みを残して、SiC基板12の全部とエピタキシャル層13の一部とを連続的に除去する工程とを備える。

(もっと読む)

窒化物半導体素子の製造方法

【課題】ドレインリーク電流を低減することが可能な窒化物半導体素子の製造方法を提供する。

【解決手段】ヘテロ電界効果トランジスタ1の製造方法は、ドリフト層20aを支持基板10上にエピタキシャル成長させる工程と、水素ガスをキャリアガスとして用いて、p型半導体層である電流ブロック層20bをドリフト層20a上に1000℃以上でエピタキシャル成長させる工程と、窒素ガス、アルゴンガス、ヘリウムガス及びネオンガスからなる群より選ばれる少なくとも一種のガスをキャリアガスとして用いて、コンタクト層20cを電流ブロック層20b上にエピタキシャル成長させる工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】炭化珪素の半導体層の表面に発生するステップバンチングを抑制する。

【解決手段】半導体装置の製造方法は、炭化珪素のエピタキシャル層14にドーパントを導入するドーパント導入工程と、PLD、FCVA法又はECRスパッタ法を利用してエピタキシャル層14の表面にカーボン膜24を形成するカーボン膜形成工程と、カーボン膜24が残存した状態でエピタキシャル層14をアニール処理するアニール処理工程とを備える。

(もっと読む)

半導体製造装置および半導体製造方法

【課題】本発明は、スループット、成膜均一性を低下させることなく、電極の接続面へのプロセスガスの回り込みを抑制し、半導体装置の高性能化や信頼性の向上、低コスト化を図ることが可能な半導体製造装置及び半導体製造方法を提供する。

【解決手段】本発明の半導体製造装置は、ウェーハwが導入される反応室11と、反応室11にプロセスガスを供給するガス供給機構12と、反応室11よりガスを排出するガス排出機構13と、ウェーハwを載置するウェーハ支持部材15と、ウェーハ支持部材15を載置するリング16と、リング16と接続され、ウェーハwを回転させるための回転駆動制御機構17と、リング16内に設置され、ウェーハwを所定の温度に加熱するために設けられるヒータ18と、ヒータ18と接続され、ねじ込み用凹部19aを有する電極部品19と、ねじ込み用凹部19aで電極部品19と接続されるねじ込み部21aを有する電極21と、を備える。

(もっと読む)

SiCエピタキシャルウェハ

【課題】三角欠陥及び積層欠陥が低減され、キャリア濃度及び膜厚の均一性が高く、ステップバンチングフリーのSiCエピタキシャルウェハを提供する。

【解決手段】本発明のSiCエピタキシャルウェハは、0.4°〜5°のオフ角で傾斜させた4H−SiC単結晶基板上にSiCエピタキシャル層を形成したSiCエピタキシャルウェハであって、前記SiCエピタキシャル層の表面の三角形状の欠陥密度が1個/cm2以下であることを特徴とする。

(もっと読む)

成膜装置および成膜方法

【課題】反応ガスの気流を基板上に効率よく集めて、エピタキシャル膜の成長速度を増大させることのできる成膜装置および成膜方法を提供する。

【解決手段】成膜装置100は、チャンバ1と、チャンバ1の上部に設けられて反応ガス25をチャンバ1内に供給する供給部4と、チャンバ1内に設けられた中空筒状のライナ2と、ライナ2内に設けられて半導体基板6が載置されるサセプタ7と、サセプタ7を支持する回転筒23とを有する。回転筒23の回転によってサセプタ7を回転させながら、半導体基板6上に所定の膜が成膜される。ライナ2は、サセプタ7の周縁部上部を包囲するとともに、サセプタ7と一緒に回転するよう構成されている。

(もっと読む)

気相成長方法

【課題】成長条件とを駆使し、基板上への成長膜厚を均一にする方法を提供する。

【解決手段】チャンバ120内に、支持台110上に載置された基板101が収容され、この基板101上に成膜するためのガスを供給する第1の流路及びガスを排気する第2の流路が接続された気相成長装置を用い、基板上に半導体層を気相成長する際に、成膜するための反応ガス及びキャリアガスの流量と濃度、チャンバ内の真空度、基板温度及び基板を回転する回転速度を制御して、半導体層の膜厚を均一にする。

(もっと読む)

シリコンウエハ及びその製造方法

【課題】ミスフィット転位や反りを低減できるシリコンウエハおよびその製造方法を提供する。

【解決手段】シリコン基板10と、ドナー濃度およびアクセプタ濃度間の差の絶対値が1×1018atoms/cm3以上で、かつ前記基板10上に設けられた第一のエピタキシャル層11と、ドナー濃度およびアクセプタ濃度間の差の絶対値が5×1017atoms/cm3以下で、かつ第一のエピタキシャル層11上に設けられ、該エピタキシャル層11と同じ導電型である第二のエピタキシャル層12と、を有し、第一のエピタキシャル層11に格子定数調整成分を添加して、シリコン単結晶の格子定数(aSi)に対する第一のエピタキシャル層11の格子定数(a1)の変化量((a1−aSi)/aSi)およびシリコン単結晶の格子定数に対する第二のエピタキシャル層12の格子定数(a2)の変化量((a2−aSi)/aSi)を臨界格子不整合度未満に調整する。

(もっと読む)

バイポーラ半導体素子

【課題】ドリフト層とドリフト層に隣接する層との界面の応力を低減して、順方向電圧を低く抑えることができるバイポーラ半導体素子を提供する。

【解決手段】このpinダイオード20は、n型SiCドリフト層23の膜厚の各範囲(300μm以下200μm超),(200μm以下100μm超),(100μm以下50μm超)に対応して、n型SiCバッファ層22の不純物濃度の各上限値(5×1017cm−3),(7×1017cm−3),(10×1017cm−3)が設定されている。これにより、n型SiCドリフト層23とn型SiCバッファ層22との界面の応力を低減でき、順方向電圧を低減できる。

(もっと読む)

微細凹凸表面を有したエピタキシャル基板とその製造方法

【課題】エピタキシャル基板と製造方法を提供する。

【解決手段】本発明のエピタキシャル基板は結晶性基板を備える。結晶性基板は微細な凹凸を備えるとともにパターニング不要のエピタキシャル表面を有する。本発明によるエピタキシャル基板は化合物半導体材料から、良好な品質のエピタキシャル層の成長を得るという利点を有する。さらに、本発明によるエピタキシャル基板の製造方法は低コストかつ製造時間短縮といった利点を有する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】性能を向上できるSiC半導体装置の製造方法を提供する。

【解決手段】SiC半導体装置の製造方法は、以下の工程を備える。少なくとも一部に不純物が注入された第1の表面を含むSiC半導体を準備する(ステップS1〜S3)。SiC半導体の第1の表面を洗浄することにより、第2の表面を形成する(ステップS4)。第2の表面上にSi元素を含む膜を形成する(ステップS5)。Si元素を含む膜を酸化することにより、SiC半導体装置を構成する酸化膜を形成する(ステップS6)。

(もっと読む)

1 - 20 / 109

[ Back to top ]