Fターム[5F045DA69]の内容

気相成長(金属層を除く) (114,827) | 半導体成長層の構造 (3,415) | 半導体成長層の物性 (649) | 応力(圧縮、引張り)に特徴 (93)

Fターム[5F045DA69]に分類される特許

1 - 20 / 93

半導体装置およびその製造方法

窒化物半導体基板

【課題】Si単結晶を下地基板として用いた場合の、リーク電流低減と電流コラプス改善が、効果的に達成された窒化物半導体基板を提供する。

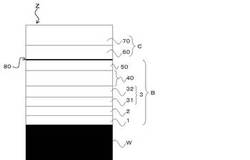

【解決手段】Si単結晶基板Wの一主面上に窒化物からなる複数のバッファ層Bを介して窒化物半導体の活性層Cが形成されている窒化物半導体基板であって、バッファ層Bは少なくとも活性層Cと接する層50の炭素濃度が1E+18atoms/cm3以上1E+20atoms/cm3以下であること、バッファ層Bと活性層Cの界面領域80において全転位密度に対するらせん転位密度の比が0.15以上0.3以下であること、さらにバッファ層Bと活性層Cの界面領域80における全転位密度が15E+9cm−2以下である窒化物半導体基板。

(もっと読む)

エピタキシャルウェーハとその製造方法

【課題】歪み層形成に供されるウェーハで転位発生に対して耐性が高いエピタキシャルウェーハを提供する。

【解決手段】シリコンエピタキシャル層表面の酸素濃度が1.0×1017〜12×1017atoms/cm3とされてなるエピタキシャルウェーハの製造方法であって、酸素濃度設定熱処理の処理温度Xと処理時間Yとが、処理温度Xが800℃〜1400℃の範囲、処理時間Yが180min以下で、かつ、

Y ≧ 1.21×1010 exp(−0.0176X)

の関係を満たすように設定される。

(もっと読む)

基板処理方法および基板処理装置

【課題】シリコン酸化膜の除去後、シリコンゲルマニウム膜の形成までのQタイムを長くするとともに、シリコンゲルマニウム膜の形成におけるプリベイクの温度を低くする。

【解決手段】基板処理装置1では、酸化膜除去部4にて基板9の一の主面上のシリコン酸化膜が除去された後、シリル化処理部6にてシリル化材料を付与して、当該主面に対してシリル化処理が施される。これにより、シリコン酸化膜の除去後、シリコンゲルマニウム膜の形成までのQタイムを長くするとともに、シリコンゲルマニウム膜の形成におけるプリベイクの温度を低くすることができる。

(もっと読む)

ヘテロエピタキシャル層を備えた半導体ウェハ及び前記ウェハの製造方法

【課題】バウの制御のためだけでなく、SiGeエピタキシャル層の品質を改善するために、特にSi基板上に堆積されたSiGe層のクロスハッチ及び表面ラフネスを低減するために、背面層によって形成された応力を用いる適切な解決策を提供する。

【解決手段】第1の面及び第2の面を有する基板10、前記基板の第1の面に堆積された完全に又は部分的に緩和されたヘテロエピタキシャル層20、及び前記基板の第2の面に堆積された応力相殺層30を有する、半導体ウェハ。

(もっと読む)

窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法

【課題】シリコン基板上に形成したクラックが少ない高品位の窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法を提供する。

【解決手段】実施形態によれば、シリコン基板の上に形成されたAlNバッファ層の上に形成された機能層を備える窒化物半導体素子が提供される。機能層は、交互に積層された、複数の機能部低濃度層と、複数の機能部高濃度層と、を含む。機能部低濃度層は、窒化物半導体を含み、Si濃度が5×1018cm−3未満である。機能部高濃度層は、Si濃度が5×1018cm−3以上である。複数の機能部高濃度層のそれぞれの厚さは、機能部低濃度層のそれぞれの厚さよりも薄い。複数の機能部高濃度層のそれぞれの厚さは、0.1ナノメートル以上50ナノメートル以下である。複数の機能部低濃度層のそれぞれの厚さは、500ナノメートル以下である。

(もっと読む)

半導体素子及びその製造方法

【課題】厚膜化が可能で、反りが小さく、かつリーク電流が小さい半導体素子を提供する。

【解決手段】基板と、基板の上方に形成された第1のバッファ領域と、第1のバッファ領域上に形成された第2のバッファ領域と、第2のバッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、第1のバッファ領域は、第1半導体層と、第2半導体層とが順に積層した複合層を少なくとも一層有し、第2のバッファ領域は、第3半導体層と、第4半導体層と、第5半導体層とが順に積層した複合層を少なくとも一層有し、第4半導体層の格子定数は、第3半導体層と第5半導体層の間の格子定数を有する半導体素子。

(もっと読む)

半導体装置

【課題】基板の反りを抑制しつつ、バッファ層及び化合物半導体の厚さを稼ぐことができ、素子耐圧を向上することができる半導体装置を提供する。

【解決手段】半導体装置は、基板2と、バッファ層3と、窒化物系化合物半導体4とを備える。バッファ層3は、AlN層とGaN層とを積層した第1のバッファ領域321,331と、GaN層を有する第2のバッファ領域322,332とを交互に積層して構成される。バッファ層3において窒化物系化合物半導体4側の第1のバッファ領域331とそれに隣接する第2のバッファ領域332との1組の全体のAl組成は基板側の1組のAl組成に対して大きく設定されている。

(もっと読む)

半導体薄膜の製造方法及び製造装置

【課題】欠陥等が無く均質化され同じ内部応力の半導体薄膜を、基板の両面に同時に結晶成長させることができ、しかも、製造工程が簡単で、歩留まりも高い半導体薄膜の製造方法及び製造装置を提供する。

【解決手段】本発明の半導体薄膜の製造方法は、基板3の表面3aに第1の半導体薄膜を、この基板3の裏面3bに第2の半導体薄膜を、同時に形成する半導体薄膜の製造方法であり、基板3の表面3aを赤外線ランプ15で加熱するとともに、この表面3aに第1の原料ガスg1を導入し、この表面3aに第1の半導体薄膜を成長させ、同時に、この基板3の裏面3bに第2の原料ガスg2を導入し、この裏面3bに第2の半導体薄膜を成長させる。

(もっと読む)

窒化物半導体素子および窒化物半導体パッケージ

【課題】GaN電子走行層の厚さを広い範囲で選択することができ、デバイス設計の自由度を高めることができる窒化物半導体素子、および耐圧および信頼性に優れる窒化物半導体素子パッケージを提供すること。

【解決手段】基板41上に、AlN層47、第1AlGaN層48(平均Al組成50%)および第2AlGaN層49(平均Al組成20%)からなるバッファ層44を形成する。バッファ層44上には、GaN電子走行層45およびAlGaN電子供給層46からなる素子動作層を形成する。これにより、HEMT素子3を構成する。

(もっと読む)

基板上に堆積された窒化ガリウムフィルムにおける応力の制御方法

【課題】シリコンおよび炭化ケイ素基板上に堆積されたGaNフィルムにおける応力の制御方法、およびこれによって生成されたGaNフィルムを提供する。

【解決手段】典型的な方法は、基板を供給すること、および供給の中断をまったく伴なわず、成長チャンバへの少なくとも1つの先駆物質の供給によって形成された、当初組成物から最終組成物までの実質的に連続したグレードの様々な組成物を有する基板上にグレーデッド窒化ガリウム層を堆積させることを含む。典型的な半導体フィルムは、基板と、供給の中断をまったく伴なわず、成長チャンバへの少なくとも1つの先駆物質の供給によって形成された、当初組成物から最終組成物までの実質的に連続したグレードの様々な組成物を有する基板上に堆積されたグレーデッド窒化ガリウム層とを含む。

(もっと読む)

へテロ接合トランジスタ及びその製造方法

【課題】チャネル層中のキャリア濃度を増すため、高いアルミニウム含有率を有した厚いAlGaN層は、成長中か冷却後にひびが入る傾向があり、これによってデバイスが破壊される。

【解決手段】基板上の第1のIII族窒化物層は第1の歪みを有する。GaN層のような第2のIII族窒化物層が、第1のIII族窒化物層上に設けられている。第2のIII族窒化物層は、第1のIII族窒化物層のバンドギャップよりも小さなバンドギャップを有し、かつ第1の歪みの大きさよりも大きい第2の歪みを有する。AlGaN層又はAlN層のような第3のIII族窒化物層がGaN層上に設けられている。第3のIII族窒化物層は、第2のIII族窒化物層のバンドギャップよりも大きなバンドギャップを有し、かつ第2の歪みと逆の歪みの型の第3の歪みを有する。ソースコンタクトとドレインコンタクトとゲートコンタクトを第3のIII族窒化物層上に設ける。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的短い製造時間で容易且つ確実に反りのない基板を得ることを可能とし、低コストで信頼性の高い高耐圧及び高出力の化合物半導体装置を実現する。

【解決手段】Si基板10上に、AlNからなる第1のバッファ層2と、AlGaNのAl組成比率が均一となるように形成された均一組成領域3aと、第2のバッファ層3の上面に近づくにつれてAlGaNのAl組成比率が徐々に高くなるように形成された傾斜組成領域3bとが積層されてなる第2のバッファ層3とが形成され、第2のバッファ層3上に電子走行層4及び電子供給層6等が形成されてAlGaN/GaN・HEMTが構成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】基板に化合物半導体を結晶成長する際の基板の反りを抑制する。

【解決手段】半導体装置の製造方法は、基板の一方の面にアモルファス半導体層を形成する工程と、基板の他方の面に化合物半導体層を形成する際の加熱処理により、アモルファス半導体層を結晶化させる工程と、を備える。

(もっと読む)

半導体基板

【課題】Si基板上にGaN結晶をエピタキシャル成長させた場合の基板の反り、またはGaN結晶の割れを抑制する。

【解決手段】ベース基板と第1結晶層と第2結晶層と機能層とを有し、ベース基板、第1結晶層、第2結晶層および機能層が、ベース基板、第1結晶層、第2結晶層、機能層の順に配置され、第1結晶層と第2結晶層とが格子整合または擬格子整合して接し、機能層の熱膨張係数が、ベース基板の熱膨張係数より大きく、第1結晶層の格子定数が、第2結晶層の格子定数より小さく、第1結晶層および第2結晶層が互いに接する第1界面と、機能層側に位置する第2結晶層の第2界面とを、同一視野に含んで断面TEM像を観察した場合、第1界面を含んで観察される第1モアレ画像の面積が、第2界面を含んで観察される第2モアレ画像の面積より小さい半導体基板を提供する。

(もっと読む)

電界効果トランジスタ

【課題】クラックを低減した窒化物半導体電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、基板101の上に形成された半導体層積層体と、半導体層積層体の上に形成されたソース電極107及びドレイン電極108と、ソース電極とドレイン電極との間に形成されたゲート電極109とを備えている。半導体層積層体は、第1の凹部102aを有する第1の窒化物半導体層102と、第1の凹部の底面上に形成された第2の窒化物半導体層105と、第1の凹部を除く領域の上及び第1の凹部の側面上に形成された第3の窒化物半導体層106とを有している。バンドギャップエネルギーの平均値が、第2の窒化物半導体層は第1の窒化物半導体層よりも大きく、第3の窒化物半導体層は第1の窒化物半導体層よりも大きく且つ第2の窒化物半導体層よりも小さい。

(もっと読む)

高品質の緩和シリコンゲルマニウム層の製造方法

【課題】半導体材料上のSi1−xGex層の堆積中、パーティクル生成を最小限化する方法を提供する。

【解決手段】Si前駆体と、分解温度がゲルマンより高いGe前駆体とを含む雰囲気中に基板を設けるステップ、および最終Ge含有量が約0.15より大きくかつパーティクル密度が約0.3パーティクル/cm2より小さいSi1−xGex層を前記基板上に堆積するステップを含む。

(もっと読む)

GaN系半導体エピタキシャル基板の製造方法

【課題】反りのない優れた結晶性を有するGaN系半導体をエピタキシャル成長させることができるGaN系半導体エピタキシャル基板の製造方法を提供する。

【解決手段】希土類ペロブスカイト基板上11に、AlNからなる低温保護層12を成長させ、この低温保護層12上に、Alの組成x1が0.40≦x1≦0.45のAlx1Ga1−x1Nからなる第1AlGaN系半導体層を成長させる。そして、前記第1AlGaN系半導体層上に、Alの組成x2が0≦x2≦0.45のAlx2Ga1−x2Nからなる第2AlGaN系半導体層以降の成長層を積層させて、組成勾配層13,14とする。

(もっと読む)

III族窒化物半導体からなるHEMT、およびその製造方法

【課題】Si基板を成長基板として用いたIII 族窒化物半導体からなるHEMTの製造方法において、ウェハの反りを低減すること。

【解決手段】Si基板10上に形成されたバッファ層11は、初期層110と厚さ4μm以上の複合層111が積層された構造である。初期層110は、60nm以上の第1のAlN層110a、60nm以上の第1のGaN層110bが積層された構造であり、複合層111は、第2のAlN層111aと、第2のAlN層111a上に形成された第2のGaN層111bとからなる積層構造を複数回繰り返した構造である。第2のAlN層111aに対する第2のAlN層111aの厚さの比は4〜5である。複合層111形成時のV/III 比は、初期層110形成時よりも高くしている。バッファ層11上には、電子走行層12と電子供給層13が形成されており、その総膜厚は1μm以上である。

(もっと読む)

半導体発光素子

【課題】半導体層における応力を緩和し低動作電圧で高発光効率の半導体発光素子を提供する。

【解決手段】窒化物半導体を含むn型半導体層と、窒化物半導体を含むp型半導体層と、n型半導体層とp型半導体層との間に設けられ、互いに積層され、GaNを含む複数の障壁層と、複数の障壁層のそれぞれの間に設けられ、第1In組成比のInGaNを含む井戸層と、を有する発光部と、n型半導体層と発光部との間に設けられ、互いに積層され、GaNを含む複数の第1層と、複数の第1層のそれぞれの間に設けられ、第1In組成比の0.6倍以上で第1In組成比よりも低い第2In組成比のInGaNを含む第2層と、を有する多層構造体と、多層構造体と発光部との間に設けられ、Aly1Ga1−y1N(0<y1≦0.01)を含む第3層を含むn側中間層と、を備えたことを特徴とする半導体発光素子が提供される。

(もっと読む)

1 - 20 / 93

[ Back to top ]