Fターム[5F045GH09]の内容

気相成長(金属層を除く) (114,827) | 機械加工プロセスとの組み合わせ (190) | 機械加工による後処理(膜形成が先) (106) | 研磨 (63)

Fターム[5F045GH09]の下位に属するFターム

化学的機械研磨(CMP) (20)

Fターム[5F045GH09]に分類される特許

1 - 20 / 43

ドープIII−Nバルク結晶及び自立型ドープIII−N基板

炭化珪素基板、半導体装置及び配線基板

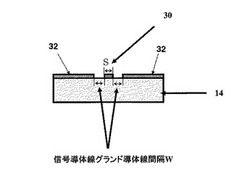

【課題】電子素子等のデバイスを実装するには、炭化珪素基板の高周波損失が大きく、実際には電子素子を炭化珪素基板に実装できなかった。

【解決手段】20GHzにおける高周波損失が2.0dB/mm以下の炭化珪素基板であれば、電子素子を実装して十分に動作させることができることを見出し、2.0dB/mm以上の高周波損失特性を有する炭化珪素基板を2000℃以上で加熱する。この熱処理により20GHzにおける高周波損失を2.0dB/mm以下にすることができた。また、ヒーターに窒素を流さないで、CVDにより炭化珪素基板を作製することによって高周波損失を2.0dB/mm以下にすることができた。

(もっと読む)

窒化物半導体基板の製造方法

【課題】低転位であり、特に、窒化物半導体基板に内在する応力を抑制させて、反りの少ない窒化物半導体基板の製造方法を提供することを目的とする。

【解決手段】サファイア基板の(0001)面上に、第1の窒化物半導体パターンを形成し、該第1の窒化物半導体パターンを成長核として第2の窒化物半導体層を成長させ、少なくとも前記サファイア基板を除去することを含む窒化物半導体基板の製造方法であって、第1の窒化物半導体パターンは、平面形状が三角形の複数の枠体によって形成され、該枠体の頂点のみを、隣接する枠体と共有するように規則的に配置されて構成される窒化物半導体基板の製造方法。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】エピタキシャル層表面の付着パーテイクルが少なく、平滑な面取り部の形状を持ち、かつ酸素析出特性にも優れた、先端CMOSに好適なエピタキシャルウェーハを、安定的にかつ低コストで製造することができる方法を提供することを目的とする。

【解決手段】シリコン単結晶基板上にエピタキシャル層を成長させることによりエピタキシャルウェーハを製造する方法において、前記シリコン単結晶基板上に、エピタキシャル層を成長させる工程と、該エピタキシャル層を成長させたシリコン単結晶基板を、650〜800℃の温度で1時間以上保持した後に850℃以上の温度に昇温して、前記エピタキシャル層の表面に保護酸化膜を形成する工程と、該保護酸化膜を形成したシリコン単結晶基板の面取り部を研磨する工程と、その後、前記保護酸化膜を除去して、仕上げ洗浄を行う工程とを含むエピタキシャルウェーハの製造方法。

(もっと読む)

窒化物系化合物半導体素子の製造方法

【課題】歩留まり良く、正確に切断する窒化物系化合物半導体チップの製造方法を提供する。

【解決手段】GaN基板上に窒化物系化合物半導体が積層されたウエハーをチップ状に分離する方法であって、前記GaN基板を厚み100μm以上210μm以下になるように研磨する工程と、前記ウエハーの窒化物系化合物半導体が積層された側に、前記ウエハーに対してカッターの中心軸の角度が60°より大きく75°より小さく、カッター押し込み深さが前記GaN基板の厚みの5%以下でカッターにより割り溝を形成する工程と、前記ウエハーを、窒化物系化合物半導体が積層された側から、またはGaN基板側から、前記割り溝の位置に沿って、ブレード押し込み深さが前記GaN基板の厚みの25%以上60%以下でブレードにより荷重衝撃を与えて割断する工程と、を具備することを特徴とする。

(もっと読む)

エピタキシャル被覆された半導体ウェハの製造方法

【課題】応力のないエピタキシャル被覆させた半導体ウェハを提供する。

【解決手段】少なくとも前面がポリシングされた半導体ウェハを準備し、枚葉式エピタキシャル反応器中のサセプタに裁置し、1000〜1200℃の温度で化学気相蒸着によりエピタキシャル層をポリシングされた前面に設けることにより被覆するエピタキシャル被覆させた半導体ウェハの製造方法において、エピタキシャル被覆が行われた後に、前記半導体ウェハを1200〜900℃の温度範囲で、1秒あたり5℃より低い速度で冷却する。

(もっと読む)

III族窒化物半導体基板およびIII族窒化物半導体基板の製造方法

【課題】III族窒化物半導体で構成される基板を生産する際の歩留まりを改善することを課題とする。

【解決手段】基板の表面から裏面まで貫通する貫通孔20を有するIII族窒化物半導体(AlxGa1−x−yInyN(0≦x≦1、0≦y≦1、0≦x+y≦1))で構成される基板30と、貫通孔20の内部に充填され、貫通孔20を塞ぐ、組成一様のIII族窒化物半導体で構成される充填材40と、を有するIII族窒化物半導体基板10を提供する。

(もっと読む)

独立(Al、Ga、In)Nおよびそれを形成するための分割方法

【課題】非常に優れた形態的特徴を有し、例えばマイクロエレクトロニクスおよび/またはオプトエレクトロニクスデバイスおよびデバイス前駆体構造体を製作するための基板として使用される(Al、Ga、In)N物品の製造方法を提供する。

【解決手段】エピタキシャルに適合できる犠牲型板12を設けるステップと、単結晶(Al、Ga、In)N材料16を型板12上に堆積して、犠牲型板12と(Al、Ga、In)N材料16との間の界面14を含む複合犠牲型板/(Al、Ga、In)N物品10を形成するステップと、複合犠牲型板/(Al、Ga、In)N物品10を界面修正して、犠牲型板12を(Al、Ga、In)N材料16から分割し、独立(Al、Ga、In)N物品10を生じるステップにより、独立(Al、Ga、In)N物品を製造する。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法およびシリコンエピタキシャルウェーハ

【課題】{110}面からの傾斜角度が小さくてもヘイズレベルが良好で、かつシリコン単結晶エピタキシャル層の層厚均一性も良好であり、更に表面欠陥の少ないシリコンエピタキシャルウェーハの製造方法を提供する。

【解決手段】シリコン単結晶基板の主表面上にシリコン単結晶エピタキシャル層を気相成長させるシリコンエピタキシャルウェーハの製造方法であって、前記シリコン単結晶基板として、主表面が{110}面または{110}面からのオフアングル角度が0.5度未満のものを用い、かつ前記気相成長工程では、前記シリコン単結晶基板温度を1170℃〜1190℃として気相成長することを特徴とするシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

GaN基板および発光デバイス

【課題】発光デバイスの発光の波長領域内における波長の光に関して低い吸収係数を有し、かつ、所定値以下の比抵抗を有し、その発光デバイスに好適なGaN基板を提供する。

【解決手段】GaN基板10は、波長が380nmの光および波長が1500nmの光に関する吸収係数が7cm-1以上であり、少なくとも波長が500nm以上780nm以下の光に関する吸収係数が7cm-1未満であり、比抵抗が0.02Ωcm以下である。ここで、波長が500nm以上780nm以下の光に関する吸収係数を7cm-1未満とすることができる。

(もっと読む)

窒化ガリウム系半導体基板の製造方法

【課題】貫通ピットの無い窒化ガリウム系半導体基板を安価に得ることができる窒化ガリウム系半導体基板の製造方法を提供する。

【解決手段】窒化ガリウム系半導体基板の製造方法であって、気相成長装置内に、表面にピット25を生じた窒化ガリウム系半導体層20を有する基板を準備する第1の工程と、前記気相成長装置内で、前記窒化ガリウム系半導体層20上に、非晶質又は多結晶のIII族窒化物のピット埋込層30を形成して前記ピット25を埋める第2の工程と、前記ピット埋込層30を研磨により除去して前記窒化ガリウム系半導体層20の表面を露出させる第3の工程と、を具備する。

(もっと読む)

窒化物半導体自立基板

【課題】基板上に成長したエピタキシャル成長層およびそれを用いたデバイス作製における歩留まりを向上させるために必要な外形形状を持つ窒化物半導体自立基板を提供する。

【解決手段】窒化物半導体からなる自立した単結晶基板を形成し、その単結晶基板を裏面から研磨して所定の厚さに形成する窒化物半導体自立基板において、単結晶基板の外周面に、その基板の表面側から角度θが70°以上〜130°以下となる傾斜面が形成されているものである。

(もっと読む)

結晶成長方法および結晶基板

【課題】結晶性を良好に維持するとともに、成長させる結晶の面積を大きくする結晶成長方法、結晶基板、および半導体デバイスを提供する。

【解決手段】結晶成長方法によれば、複数の種基板10を、種基板10の成長する面が{001}面となるように種基板10の側部11側にずらして配置する配置工程と、ハイドライド気相成長法により、複数の種基板10の各々の表面12上にAlxInyGa(1-x-y)N(0≦x≦1、0≦y≦1、x+y≦1)結晶20を成長させる成長工程とを備えている。そして、成長工程では、複数の種基板10の各々の表面12上に成長した結晶20の各々が一体化するように1100℃を超えて1300℃以下の温度で成長させることを特徴としている。

(もっと読む)

パワー系半導体装置

【課題】パワーMOSFET等のドリフト領域等に関して、スーパジャンクション構造を導入する方法として、トレンチフィル方式におけるPカラム領域埋め込み用トレンチの埋め込みエピタキシプロセスを種々検討したところ、エピタキシャル成長時の高熱長時間処理により、埋め込みエピタキシャル層外へ拡散してしまうという問題があることが明らかとなった。

【解決手段】本願発明は、N型カラムとP型カラムが交互に繰り返されるスーパジャンクション構造を有するシリコン系パワー半導体装置において、前記P型カラムには、ボロン拡散抑制効果を有する元素が添加されている。

(もっと読む)

窒化物半導体の成長方法

【課題】安価に、反りの少ない窒化物半導体を成長することができる窒化物半導体の成長方法を提供する。

【解決手段】本発明の窒化物半導体の成長方法は、気相成長法により、基板10上に、窒化物半導体の結晶からなる第1凹凸構造30を形成し、該第1凹凸構造30の凸部の上部から窒化物半導体を選択的に成長させることにより、前記第1凹凸構造30上に、窒化物半導体の結晶からなる第2凹凸構造32を形成することを特徴とする。

(もっと読む)

III族窒化物結晶の製造方法及びIII族窒化物結晶

【課題】(0001)面以外の任意に特定される主面を有する、クラックの少ないIII族窒化物結晶の製造方法を提供する。

【解決手段】2枚以上のシード基板を隣接して配置し、それらシード基板上にIII族窒化物結晶を成長させるIII族窒化物結晶の製造方法において、シード基板の境界線と成長させるIII族窒化物結晶の<0001>軸を主面に投影した直線とがなす角度をθとした場合、1以上の境界線が以下の(1)又は(2)を満たす。(1)0°<θ<90°である。(2)θ=0°である境界線(l)が2本以上存在し、隣り合う境界線(l)が同一直線上にない。

(もっと読む)

基板及びその製造方法

【課題】自重による基板素材の撓みを低減することができる基板及びその製造方法を提供する。

【解決手段】周縁部1bが支持された場合、自重による撓みを生じる基板素材の一面1aには、自重による基板素材の撓みを低減し、基板素材の熱膨張係数より大きい熱膨張係数を有する膜が形成されている。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】表面ラフネスが小さく、エピタキシャル膜の表面上のヘイズレベルが小さく、より微小サイズのLPDについても検出可能であるエピタキシャルウェーハを提供することができ、さらに、ピット状欠陥の発生が低減されたエピタキシャルウェーハを提供を提供することにある。

【解決手段】シリコン基板上にエピタキシャル膜を形成するエピ膜形成工程(図1(a))後、前記エピタキシャル膜の表面を酸化洗浄する酸化洗浄工程(図1(b))と、酸化洗浄工程後24時間以内に、前記エピタキシャル膜の表面を研磨するエピ後研磨工程(図1(c))とを行うことを特徴とする。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】酸化膜形成工程、酸化膜除去工程などを省略して製造コストを抑制しつつ、エピタキシャル層表面への欠陥(ピット)発生を低減したエピタキシャルウェーハを製造することができる方法を提供する。

【解決手段】シリコンウェーハ上にエピタキシャル層を形成するエピタキシャル層形成工程と、エピタキシャルウェーハの主面を研磨する研磨工程とを含むエピタキシャルウェーハの製造方法であって、エピタキシャル層形成工程後、研磨工程を行う直前まで、ウェーハを液体中で保管する保管工程を更に含むことを特徴とする、エピタキシャルウェーハの製造方法である。

(もっと読む)

GaN単結晶基板およびその製造方法、ならびにGaN系半導体デバイスおよびその製造方法

【課題】大口径で主面の面方位が(0001)および(000−1)以外で主面内におけるキャリア濃度の分布が実質的に均一であるGaN単結晶基板およびその製造方法を提供する。

【解決手段】本GaN単結晶基板20pは、主面20pmの面積が10cm2以上であり、主面20pmの面方位が(0001)面または(000−1)面20cに対して65°以上85°以下で傾斜しており、主面20pm内におけるキャリア濃度の分布が実質的に均一、たとえば主面20pm内において平均キャリア濃度に対するキャリア濃度のばらつきが±50%以内である。

(もっと読む)

1 - 20 / 43

[ Back to top ]