Fターム[5F045HA23]の内容

気相成長(金属層を除く) (114,827) | 他プロセスとの組合せ (2,158) | 連続処理(エッチング処理工程を除く) (442) | 一室連続処理 (208) | 成膜工程以外との組合せ (81)

Fターム[5F045HA23]に分類される特許

1 - 20 / 81

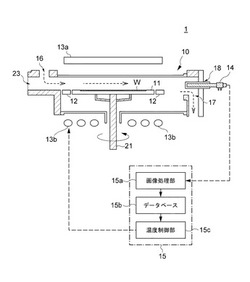

半導体ウェーハの製造方法及び半導体製造装置

【課題】ウェーハ搬入時にウェーハのエッジが反って非接触搬送部材と接触し、スクラッチ傷が発生することを防止する。

【解決手段】反応炉10のカメラ取り付け穴18にカメラ14を取り付け、反応炉10内のウェーハを撮影可能な状態とする。次に、予め所定のウェーハ投入温度に設定された反応炉10内にウェーハWを搬入し、サセプタ11上に載置する。このとき、ウェーハWのエッジが一時的に反り上がるので、この状態をカメラ14で撮影する。そして撮影した画像からウェーハWの反り量を求め、さらにこの反り量に基づいて非接触搬送部材と接触することがない反り量となる適正なウェーハ投入温度を求める。その後、ウェーハWと同一品種を処理する場合に、反応炉10内をこの適正なウェーハ投入温度に設定する。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法

【課題】エピタキシャル成長の際の裏面クモリ及びピンハローを抑制して、高品質なシリコンエピタキシャルウェーハを製造することができる方法を提供することを目的とする。

【解決手段】チャンバー内に配設されたサセプタのウェーハ載置面上にシリコン単結晶基板を載置して、該シリコン単結晶基板上にエピタキシャル成長させることによりシリコンエピタキシャルウェーハを製造する方法であって、前記シリコン単結晶基板を載置する前に、前記チャンバー内にシリコン原料ガスを流入させながら、50秒を超えて300秒以下の時間で、前記サセプタのウェーハ載置面上にポリシリコン膜を被覆し、その後前記サセプタのウェーハ載置面上に前記シリコン単結晶基板を載置してエピタキシャル成長させるシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】GaNを用いた窒化物半導体装置において、電流が流れる経路に、再結晶成長などによる界面が存在することがない状態で、十分な耐圧が得られるようにする。

【解決手段】GaNからなるチャネル層(第2半導体層)101と、チャネル層101の一方の面であるN極性面に形成された第1障壁層(第1半導体層)102と、チャネル層101の他方の面であるIII族極性面に形成された第2障壁層(第3半導体層)103とを備える。第1障壁層102および第2障壁層103は、例えば、AlGaNから構成されている。また、ドレイン電極(第1電極)104が、第1障壁層102の上に形成され、ゲート電極105が、ドレイン電極104に対向して第2障壁層103の上に形成されている。ソース電極(第2電極)106は、ゲート電極105と離間して第2障壁層103の上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】 半導体ウエハの表面に膜を成長させる技術であって、半導体装置を効率よく製造することが可能な技術を提供する。

【解決手段】 半導体装置の製造方法であって、チャンバ内に配置された半導体ウエハの表面に膜を成長させる動作と、チャンバ内に配置された半導体ウエハと前記膜とをエッチング可能なエッチングガスをチャンバ内に導入する動作とを実行可能な半導体製造装置のチャンバ内に半導体ウエハを搬入する搬入工程と、チャンバ内に前記エッチングガスを導入する第1エッチング工程と、チャンバ内の半導体ウエハの表面に膜を成長させる第1成膜工程と、チャンバから半導体ウエハを搬出するとともに、チャンバに別の半導体ウエハを搬入する入れ換え工程と、チャンバ内に前記エッチングガスを導入する第2エッチング工程と、チャンバ内の半導体ウエハの表面に膜を成長させる第2成膜工程を有する。

(もっと読む)

炭化珪素半導体素子の製造方法及び電子デバイスの製造方法

【課題】炭化珪素とその上に形成される絶縁膜との界面の品質及び当該絶縁膜の品質を改善して界面準位密度を低減することができる炭化珪素半導体素子の製造方法及び電子デバイスの製造方法を提供する。

【解決手段】炭化珪素基板1の主表面を、水素ガスを含むクリーニングガスで表面処理し、前記主表面を窒素含有ガスで表面処理し、前記主表面上に絶縁膜2を形成する。

(もっと読む)

通電加熱線の処理方法

【課題】熱伸びせず、耐久性に優れた通電加熱線、通電加熱線の製造方法及びこの通電加熱線を用いた真空処理装置を提供することにある。

【解決手段】本発明に係る通電加熱線(TaBN線20)は、窒化タンタル線からなる第1の層21と、第1の層21の表面を被覆し、例えばホウ化物からなる第2の層22を有する。すなわち、強度が高く変形が少ない窒化タンタル線の表面を、第2の層が被覆することによって、高温環境下での窒化タンタル線からの脱窒素を抑制でき、耐久性が非常に高い通電加熱線として利用できる。また、このようなTaBN線20を用いた真空処理装置は、コストの低減・生産性の向上を図れると同時に、基板成膜時の膜質安定化も期待できる。

(もっと読む)

立方晶炭化珪素膜の製造方法

【課題】結晶欠陥が少なく、かつ平坦性に優れた高品質の立方晶炭化珪素膜を容易に得ることができる立方晶炭化珪素膜の製造方法を提供する。

【解決手段】Si基板1の表面を炭化させて下地層2を形成し、次いで、Si基板1の下地層2上に原料ガスg2を供給しつつ、この原料ガス雰囲気にて立方晶炭化珪素層3をエピタキシャル成長させ、次いで、この立方晶炭化珪素層3の表面3aをクリーニングして異物を除去し、次いで、この立方晶炭化珪素層3上に再度、原料ガスg2を供給しつつ、この原料ガス雰囲気にて立方晶炭化珪素層4をエピタキシャル成長させる。

(もっと読む)

シリコン膜の形成方法およびその形成装置

【課題】ボイドの発生を抑制することができるシリコン膜の形成方法およびその形成装置を提供する。

【解決手段】シリコン膜の形成方法は、第1成膜工程と、エッチング工程と、第2成膜工程とを備えている。第1成膜工程では、被処理体の溝を埋め込むようにシリコン膜を成膜する。エッチング工程では、第1成膜工程で成膜されたシリコン膜をエッチングして前記溝の開口部を広げる。第2成膜工程では、エッチング工程で開口部が広げられた溝にシリコン膜を埋め込むように成膜する。これにより、表面に溝が形成された被処理体の溝にシリコン膜を形成する。

(もっと読む)

エピタキシャルウェーハの製造方法、エピタキシャルウェーハ及び撮像用デバイスの製造方法

【課題】欠陥のほとんどないシリコンエピタキシャル層を形成できるエピタキシャルウェーハの製造方法、当該方法により製造されたエピタキシャルウェーハ及び撮像用デバイスの製造方法を提供することを目的とする

【解決手段】前記シリコン基板に急速熱処理を施すことによって、少なくとも前記シリコン基板の表面から0.5μmの深さまでの領域に存在するRIE法により検出される欠陥を消滅させるRIE欠陥消滅工程と、前記RIE法により検出される欠陥を消滅させたシリコン基板の表面上に前記シリコンエピタキシャル層を形成する工程とを具備するエピタキシャルウェーハの製造方法。

(もっと読む)

半導体膜の作製方法

【課題】量産性に優れた薄膜トランジスタを提供する。また半導体装置の作製において有

用な半導体薄膜を提供する。

【解決手段】プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1

×1021/cm3で含む半導体膜を形成し、前記半導体膜の一部を除去して、活性層を

形成し、トップゲート型薄膜トランジスタまたはボトムゲート型薄膜トランジスタを作製

する。また、プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1

×1021/cm3で含む半導体膜を剥離層として用いた半導体装置を作製する。また、

プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1×1021/

cm3で含む半導体膜をゲッタリングサイトとして用いた半導体装置を作製する。

(もっと読む)

窒化物半導体構造とその製造方法および発光素子

【課題】CVDマスクとして用いられるSiO2層は熱的損傷を受けやすく、熱的損傷を受けると、その構成要素であるSiやOが窒化物半導体膜に悪影響をもたらし、発光効率の低下と発光効率という問題があった。この、SiO2層を用いたマスクパターンの熱的損傷に依る問題点を解決する構造,方法を提供する。

【解決手段】窒化物半導体構造は、第1の基板、第1の窒化物半導体膜及び第2の窒化物半導体膜を備えた窒化物半導体構造であって、前記第1の基板は、前記第1の窒化物半導体膜とは異なる材料からなり、前記第1の窒化物半導体膜は前記第1の基板上に成長され、前記第1の窒化物半導体膜上面は、凹部及び凸部が同一材料で形成されており、前記第2の窒化物半導体膜は、前記第1の窒化物半導体膜上面の前記凹部及び凸部上に成長する構造、及びその構造の製造方法により解決する。

(もっと読む)

半導体発光素子及びその製造方法

【課題】 凹凸を有する基板上に形成する膜の表面が平坦になるまでの成長時間を短縮することが可能な半導体発光素子を提供する。

【解決手段】 コランダム構造のc面基板の表面に複数の凸部が形成されている。この表面に、Ga及びNを含むIII−V族半導体からなり、基板表面よりも平坦な下地膜が配置されている。下地膜の上に、Ga及びNを含む発光構造が配置されている。下地膜のa軸方向とのなす角度が15°未満の方向を第1方向とし、それと直交する方向を第2方向とする。凸部は、第1方向及び第2方向に規則的に配列している。凸部の各々は、m軸方向とのなす角度が15°未満の第1の辺と、a軸方向とのなす角度が15°未満の第2の辺とを有する。第1方向に隣り合う2つの凸部の相互に対向する第1の辺は平行であり、第2方向に隣り合う2つの凸部の相互に対向する第2の辺は平行である。対向する第2の辺のm軸方向の間隔は、対向する第1の辺のa軸方向の間隔よりも広い。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】高いアスペクト比で狭い幅の溝に、シリコン酸化膜を埋め込むことの可能な、スループットの高い半導体製造方法を提供する。

【解決手段】半導体装置の製造方法において、基板を処理室内へ搬入する工程と、炭素及び水素を含むシリコン化合物ガスを処理室内へ供給して、処理室内を第1の圧力の状態にする工程と、処理室内を前記第1の圧力にした状態において、処理室内へ供給されたシリコン化合物ガスに紫外光を照射して、基板上にシリコン酸化膜を形成する工程と、処理室内を前記第1の圧力よりも低い第2の圧力の状態にする減圧処理工程とを行う。これにより、高アスペクト比で狭い幅の溝内に、緻密なシリコン酸化膜を形成することができる。

(もっと読む)

半導体デバイスの製造方法、半導体デバイス及び基板処理装置

【課題】高誘電率及び高温状態で安定したキャパシタ絶縁膜の形成を実現した半導体デバイスを提供する。

【解決手段】基板上にアモルファスであって第1の元素を含む第1の絶縁膜を形成する第1の工程と、第1の元素とは異なる第2の元素を第1の絶縁膜に添加してアモルファスである第2の絶縁膜を前記基板上に形成する第2の工程と、第2の絶縁膜を所定のアニール温度でアニーリングして第3の絶縁膜へと相転移させる第3の工程と、を有し、アニール温度に応じて前記第2の元素の添加濃度を制御する。

(もっと読む)

成膜装置のクリーニング方法、シリコン系薄膜の成膜方法、および薄膜光電変換素子の製造方法

【課題】シリコン系薄膜の成膜を行なうための成膜室が大気開放される際に生じるHFガスの量を抑制することができる、成膜装置のクリーニング方法およびシリコン系薄膜の成膜方法を提供する。

【解決手段】成膜室50内においてフッ素系ガスを用いてプラズマが発生させられる。フッ素系ガスを用いてプラズマが発生させられた後に、成膜室50内においてシリコン系材料が堆積させられる。シリコン系材料が堆積させられた後に、成膜室が大気開放される。

(もっと読む)

圧力制御機器、圧力制御方法および基板処理装置

【課題】複数の処理工程(プロセス)を連続して行う基板処理装置において、チャンバー内の処理ガス流量や処理ガス圧力の大幅な変動に対して短時間で連続的に応答可能な圧力制御を行う圧力制御機器、圧力制御方法および該圧力制御機器を備える基板処理装置を提供する。

【解決手段】処理ガスが供給される減圧状態の処理室で複数の処理工程を行う基板処理装置であって、処理室に処理ガスを供給する処理ガス供給機構と、処理室の内部を排気する排気機構と、排気機構の排気量を調節する排気バルブと、複数の処理工程それぞれに最適な処理ガス圧力を算出するための演算テーブルを複数有し、演算テーブルに基づいて排気バルブの開度を制御する演算制御機構と、を備える基板処理装置が提供される。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 成膜温度を低下させ、成膜速度を増大させる。

【解決手段】 基板を収容した処理室内にシリコン含有ガスとボロン含有ガスとを供給して基板上にシリコン含有及びボロン含有膜を形成するシリコン含有及びボロン含有膜形成工程と、大気圧未満の圧力に設定した処理室内に酸素含有ガスと水素含有ガスとを供給して基板上に形成したシリコン含有及びボロン含有膜をボロン及びシリコン含有酸化膜に改質するシリコン含有及びボロン含有膜改質工程と、を有する。

(もっと読む)

被処理体の処理方法、処理装置、薄膜形成方法、薄膜形成装置及びプログラム

【課題】被処理体に形成された自然酸化膜を除去することができる被処理体の処理方法、処理装置及びプログラムを提供する。

【解決手段】 熱処理装置1の制御部100は、自然酸化膜が形成された半導体ウエハWを収容した反応管2内を400℃に加熱する。反応管2内が400℃に加熱されると、制御部100は、処理ガス導入管17から、塩素を含む処理ガスを供給することにより処理ガスに含まれる塩素を活性化させる。この活性化された塩素が半導体ウエハWに供給されることにより、半導体ウエハWに形成された自然酸化膜が除去される。

(もっと読む)

エピタキシャル被覆されたシリコンウェハ及びエピタキシャル被覆されたシリコンウェハの製造方法

【課題】改善されたイメージ品質を有するエピタキシャル被覆されたシリコンウェハ並びにエピタキシャル被覆されたシリコンウェハの適切な製造方法の提供

【解決手段】丸められたエッジを備えたシリコンウェハのグループを準備する工程、前記シリコンウェハのエッジをポリシングする工程、前記シリコンウェハを洗浄する工程、欠陥及びエッジラフネスに関してシリコンウェハのグループのエッジ領域を調査し、前記シリコンウェハのグループから、10〜80μmの空間波長領域に関して1nm RMSよりも低い表面粗さを有するシリコンウェハを選択する工程、選択されたシリコンウェハを枚葉型エピタキシー反応器中で前処理し、その際、第1の工程で水素雰囲気中で1〜100slmの流量で処理を行い、更に第2の工程でエッチング媒体を0.5〜5slmの流量で前記水素雰囲気に添加し、ガス分配装置を用いて反応室中で分配する工程、前記シリコンウェハをエピタキシャル被覆する工程を有するエピタキシャル被覆されたシリコンウェハの製造方法

(もっと読む)

半導体デバイスの製造方法および基板処理装置

【課題】低温での成膜が可能であり、表面平坦性、凹部埋めこみ性、ステップカバレッジに優れ、成膜速度にも優れるシリコン酸化膜の形成工程を有する半導体デバイスの製造方法および基板処理装置を提供する。

【解決手段】処理室52内にシリコン原子を含む第1の原料ガスを供給し、ウエハ200上に数原子層のアモルファスシリコン膜を形成する工程と、第1の原料ガスの供給を停止し、第1の原料ガスを処理室52内から排出する工程と、処理室52内に酸素原子を含む第2の原料ガスを供給し、ウエハ1上に形成されたアモルファスシリコン膜と反応させてシリコン酸化膜を形成する工程と、第2の原料ガスの供給を停止し、処理室52内から第2の原料ガスを排出する工程と、を繰り返して各基板上に所定膜厚のシリコン酸化膜を形成する。

(もっと読む)

1 - 20 / 81

[ Back to top ]