Fターム[5F046EB07]の内容

半導体の露光(電子、イオン線露光を除く) (57,085) | 位置合わせマークの配置 (959) | スクライブライン上 (83)

Fターム[5F046EB07]に分類される特許

1 - 20 / 83

半導体装置の製造方法および半導体装置

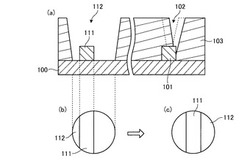

【課題】下層および上層に形成したデバイスパターン間のズレ量を現状で実施されている方法よりも高精度に計測可能な半導体装置の製造方法および半導体装置を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、パターン形成工程と、開口部形成工程とを含む。パターン形成工程では、第1層に位置ズレ計測用のパターン111と第1パターン101とを形成する。開口部形成工程では、前記第1層よりも上層に積層した第2層103に前記位置ズレ計測用のパターン111を露出させる開口部と第2パターン102とを形成する。

(もっと読む)

半導体装置の製造方法

【目的】SON構造上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置あわせをすることができる半導体装置の製造方法を提供すること。

【解決手段】シリコンウェハ1のダイシングライン4などの無効領域の内部にSON構造11のアライメントマーク9を形成し、このアライメントマーク9を赤色レーザ(透過型レーザ)の反射光16の変化で認識することで、図示しないSON構造23上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置合わせをすることができる。

(もっと読む)

半導体装置の製造方法

【課題】より視認が容易なアライメントマークを簡素な工程で形成することが可能な、半導体装置の製造方法を提供する。

【解決手段】半導体基板SUBの主表面上に、主表面に対して段差を有するパターンMKが形成される工程と、パターンMK上に、半導体材料を含む第1の半導体層PS1が形成される工程と、第1の半導体層PS1上に、半導体材料を含む第2の半導体層PS2が形成される工程と、第2の半導体層PS2上にレジストパターンRSが形成される工程とを備えている。レジストパターンRSが形成される工程において、パターンMKが位置合わせマークとして用いられる。

(もっと読む)

位置合わせ測定方法及び位置合わせ測定装置

【課題】位置合わせ測定の精度を向上する。

【解決手段】1つの実施形態によれば、位置合わせ測定方法では、測定光学系の測定領域内が2次元的に分割された複数の部分領域のそれぞれに位置合わせ測定用マークが位置するように前記位置合わせ測定用マークに対する前記測定領域の相対的な位置を順次にシフトさせながら前記位置合わせ測定用マークの位置合わせずれ量を予め測定して、前記測定光学系の特性ずれに関する装置要因誤差を前記複数の部分領域のそれぞれごとに求め、前記複数の部分領域ごとに求められた前記装置要因誤差に基づいて前記複数の部分領域のうち使用すべき部分領域を決定し、前記決定された前記使用すべき部分領域に前記位置合わせ測定用マークが位置するように前記位置合わせ測定用マークに対する前記測定領域の相対的な位置をシフトさせた状態で前記位置合わせ測定用マークの位置合わせずれ量を測定する。

(もっと読む)

フォトマスクおよび半導体装置の製造方法

【課題】 コスト上昇を招くことのない方法によってウェーハ上に形成される露光ショットの配列誤差を低減し、ショットエリアの大きさが異なる露光装置を混用しても上下のマスクパターンの重ね合わせ精度が向上できるフォトリソ工程を提供する。

【解決手段】 露光装置に露光ショットの配列誤差測定用マークを備えたフォトマスクを装着し、ウェーハ上に前記マークのレジストパターンを形成した後、前記マークを用いて露光ショット配列誤差に基づくズレに関する量を測定する。次に測定した量を上下パターンレイヤの重ね合わせ誤差と見なした時の誤差成分を算出し、さらにこの誤差成分から露光ショット配列誤差に関する誤差成分を算出する。次にこの結果を判定し、誤差成分値が所定の基準を満たさない場合は算出した露光ショット配列に関する誤差成分値を用いて露光装置のパラメータを補正し、基準を満たすようにする。

(もっと読む)

パターン位置およびオーバレイ測定方法および装置

【課題】撮像されたデバイス・パターンを使用して、ダブル・パターニング・プロセス等の、半導体製造技術における異なる層間のオーバレイを測定するシステムおよび方法を提供する。

【解決手段】パターン特徴の画像が走査型電子顕微鏡法により取得される(700)。画像内のパターン化層に対するパターン特徴の位置を使用してパターン化層の位置が決定される(704)。他のパターン特徴またはパターン化層に関するパターン化層の相対的位置が、決定されたパターン位置に基づいてベクトル形式で決定される(708)。相対的位置とデザインまたはシミュレーションからの基準値との比較に基づいてオーバレイ・エラーが決定される。オーバレイはパターン対称性を利用して高い精度および正確さで測定することができる(712)。

(もっと読む)

粗面を有するLEDを形成するための光学アライメント法

【課題】粗面を有する発光ダイオード(LED)加工時の改良された光学アライメント方法を提供する。

【解決手段】この方法では、二乗平均平方根(RMS)表面粗さσsを有する少なくとも一つの粗面化アライメントマークがウエハ上に形成される。粗面化アライメントマークは、ウエハアライメントマークが位置するLED10の表面をプラズマエッチングによって粗面化する際に形成される。また、この方法では、約2σsから約8σsの範囲の波長λAを有するアライメント光を利用して、少なくとも一つの粗面化ウエハアライメントマークが結像される。また、この方法では、検出画像がアライメント対照と比較されてウエハアライメントが確立される。ウエハアライメントが一旦確立すれば、p型コンタクト90p及びn型コンタクト90nをLEDの上面の適切な位置にそれぞれ形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】アライメントマークの配置制約を緩和し、アライメントマークを容易に配置しうるとともに、製品チップの収率低下を抑制しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたアライメントマーク上に、前記アライメントマークのマーク機能領域内にパターンのエッジを有し、前記アライメントマークが露光装置の画像検出器により前記アライメントマークとして認識されるのを阻害する阻害パターンを配置する。

(もっと読む)

アライメントデータ作成システム及び方法

【課題】アライメントマークが複数のショットに跨って形成されている場合、完成形であるアライメントマークをCADデータから作成するためにはユーザ自身の手作業が求められる。

【解決手段】1つのアライメントマークが複数のショットに跨って作成される場合に、各アライメントマークに関連する複数のショットのCADデータを相互の位置関係に応じて合成し、アライメントマークの完成形を含む合成CADデータを自動的に作成する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】製造工程が増加したり複雑化したりすることなく、SiC半導体基板とマスクとの位置合わせを高精度に行うことができるSiC半導体装置の製造方法を提供する。

【解決手段】アライメントマーク形成領域R1に、開口部の形状が、オフ方向に対して対称であり、かつオフ方向の最も下流側に位置する部分に頂点を有する多角形状とされており、アライメントマークとなるトレンチ12を形成するトレンチ形成工程と、トレンチ形成工程を行った後、SiC半導体基板10に対して、エピタキシャル層13を成長させるエピタキシャル層成長工程、または熱処理する熱処理工程の少なくともいずれか一方を行う工程と、エピタキシャル層成長工程または熱処理工程の少なくともいずれか一方の工程を行った後、アライメントマークを基準としたマスク合わせによってSiC半導体基板10にマスクを配置する工程と、を含むSiC半導体装置の製造方法とする。

(もっと読む)

基板位置決め方法

【課題】 基板のステージ載置後の相対位置を求めて簡単に精密な位置決めを行う。

【解決手段】 基板位置決め装置は、ステージ5とステージ移動機構51とカメラ6より構成され、カメラ6に基板Wの表面が撮像される。低倍率でアライメントマーク204を撮像した基板回転中心位置情報を用いるセンタリング処理によって基板Wの回転中心位置を位置補正する。次に、ステップS18において、低倍率で撮像したアライメントマーク205とスクライブライン領域203を用いた基板端部位置情報から基板Wの位置を計測し、その計測結果に基づいてステップS20において基板Wの回転角度補正を行う。つづいて、ステップS21において傾斜角度補正を行う。そして、ステップS22において、セットされた高倍率にてアライメントマーク204を撮像し、アライメントマーク204の重心位置を計算して基板の位置を補正して、基板の位置決めを行う。

(もっと読む)

半導体装置

【課題】詳細かつ正確な検査用マークの測定を容易に行なうことが可能な半導体装置を提供する。

【解決手段】半導体基板上に形成され、素子形成領域と、この素子形成領域を囲むように配置されたダイシングライン領域とを備える半導体装置であって、ダイシングライン領域では、異なるショットで形成された第1および第2の重ね合わせ検査マーク15が形成され、第1および第2の重ね合わせ検査マーク15は、第1および第2の重ね合わせ検査マークを識別するための補助マーク18を含む。

(もっと読む)

マーク位置検出装置及びマーク位置検出方法、それを用いた露光装置及びデバイスの製造方法

【課題】ウエハのアライメントを行う際に、精度の向上と共に処理時間の短縮を図る。

【解決手段】露光装置において基板に設けられたマークの位置を検出するマーク位置検出装置であって、解像度及び読み出し領域が変更可能な撮像素子と、マークから反射される光を撮像素子に導く光学系と、撮像素子の出力に基づいてマークの位置を検出する制御手段とを有し、該制御手段は、第1の解像度及び第1の読み出し領域に設定された撮像素子の出力に基づいて第1の位置検出S32を行い、該第1の位置検出S32の結果に基づいて第1の読み出し領域よりも狭範囲で、かつ第1の読み出し領域内にある第2の読み出し領域に設定し、第1の解像度よりも高解像な第2の解像度及び第2の読み出し領域に設定された撮像素子の出力に基づいて第2の位置検出S39を行う。

(もっと読む)

露光装置、露光方法およびデバイス製造方法

【課題】基板上のマークの位置をより短い時間で検出し、基板へのパターンの転写のために要する時間を削減する。

【解決手段】原版のパターンを基板の複数のショット領域に順に転写する。各ショット領域は、チップ領域102aとそれを取り囲むスクライブライン領域S1とを含む。露光装置は、走査方向に駆動されている基板における隣接する第1スクライブライン領域S1、第2スクライブライン領域S2を同時に観察し、前記第1スクライブライン領域、前記第2スクライブライン領域にそれぞれ配置されている第1マーク104a、第2マーク104bからの光を検出する検出器と、前記検出器から出力される検出信号を処理して前記第1マーク、前記第2マークの位置を決定する処理部とを備える。前記基板は、前記第1マークおよび前記第2マークの位置に基づいて位置決めされ、露光される。

(もっと読む)

デバイスの製造方法

【課題】デバイスの性能に影響を与えず、高精度の検出が可能なアライメントマークを形成することができるデバイスの製造方法の提供。

【解決手段】上層側の第1の膜が、下層側の第2の膜に対するエッチングに耐性を有する材料で構成される積層膜を形成する工程と、素子形成領域及びアライメントマーク形成領域の前記第1の膜をパターニングする工程と、少なくとも前記アライメントマーク形成領域の前記パターニングした第1の膜近傍を除く領域を、前記第2の膜に対するエッチングに耐性を有する材料で保護する工程と、前記パターニングした第1の膜をマスクとして、前記第2の膜を選択エッチングするエッチング工程と、を少なくとも有し、前記パターニングした第1の膜の周囲を掘下げることにより、前記第1の膜からなるアライメントマークの段差を増大させる。

(もっと読む)

露光方法、露光システム、及びデバイス製造方法

【課題】露光工程のスループットを高く維持して、アライメントを高精度に行う。

【解決手段】複数のウエハマークが形成されたウエハを露光する露光システムにおいて、計測対象のウエハマークに対応させてウエハW2上に複数の基準パターンを形成する簡易型露光装置4と、ウエハW2上の計測対象の複数のウエハマークとこれに対応する基準パターンとの位置ずれ量を計測するマーク検出装置10と、その位置ずれ量の計測結果に基づいてウエハW2の位置合わせを行って、ウエハW2上の複数のショット領域を露光する露光装置12と、を備える。

(もっと読む)

マーカの形成方法、マーカを有する基板及びデバイス製造方法

【課題】 改良されたマーカの形態、特にアラインメント及びオーバレイマーカ、及び基板上にこれらのマーカを形成する方法を提供する。

【解決手段】 第一に、プロダクトフィーチャと同等のピッチP1を有する2つの化学的に異質のフィーチャタイプのパターンを形成する。次にこのパターンを、パターンより大きいピッチP2を有する所望のマーカの形態のレジスト11によってマスキングする。最後に、2つのフィーチャタイプの一方を、開放領域内で選択的にエッチングする。その結果は、長い波長の放射で読み取るのに適切な大きいピッチP2を有するマーカであるが、フィーチャの縁部は、プロダクトフィーチャと同等のピッチP1を有する露光ステップで画定される。

(もっと読む)

リソグラフィ装置およびデバイス製造方法

【課題】 良好なアライメント再現性を提供すること。

【解決手段】 デバイスを製造するための方法には、基板を提供する工程であって、基板が複数の露光フィールドを備え、個々の露光フィールドが1つまたは複数のターゲット部分および少なくとも1つのマーク構造を備え、マーク構造が露光フィールドのための位置マークとして配置される工程と、対応する個々の露光フィールドのためのアライメント情報を得るために個々の露光フィールドのマークをスキャンし、かつ、測定する工程と、対応する個々の露光フィールドのためのアライメント情報から個々の露光フィールドの絶対位置を決定する工程と、露光フィールドおよび少なくとも1つの他の露光フィールドの互いに対する相対パラメータに関する追加情報を使用して、少なくとも1つの他の露光フィールドに対する個々の露光フィールドの相対位置を決定する工程と、複数の露光フィールドの各々に対して、絶対位置および決定された相対位置を結合して改良型絶対位置にする工程が含まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体ウェハ上における同層のショット間の位置の合わせずれ量を高精度で測定及び検出できるようにする。

【解決手段】半導体装置は、ウェハ状の半導体基板における、第1の露光でパターニングされる少なくとも1つのチップ領域1の周縁部に、第2の露光によって二重露光されてなり、第1の露光及び第2の露光における縦方向又は横方向の互いの位置の合わせずれ量を電気的に測定する検査用評価素子5abを有している。検査用評価素子5abは、第1の露光によって形成される第1の配線パターン5aと、第2の露光によって形成される第2の配線パターン5bとから形成されている。

(もっと読む)

マスクレス露光装置およびマスクレス露光方法

【課題】 本発明は、MEMS、半導体等の製造に用いるマスクレス露光装置およびマスクレス露光方法に関し、投影パターンの大きさに応じて投影倍率を可変にした場合であっても精度よく投影パターンを形成することを目的とする。

【解決手段】 基板を支持するステージと、前記基板に投影する所望の投影パターンを外部信号の入力により生成する空間光変調部と、対物レンズを備え前記投影パターンを前記基板に投影する投影光学系と、前記対物レンズを介して前記基板に形成された位置合わせマークを検出する観察光学系とを有するマスクレス露光装置であって、前記投影光学系は、投影倍率を変更可能に前記対物レンズが構成されてなるとともに、前記投影倍率を変更する毎に、前記位置合わせマークを予め設定した指標又は予め特定した前記投影パターンの中心位置に対して位置合わせする機構を有することを特徴とする。

(もっと読む)

1 - 20 / 83

[ Back to top ]