Fターム[5F048AB02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 用途 (4,368) | マスタースライス、ゲートアレイ (76)

Fターム[5F048AB02]に分類される特許

1 - 20 / 76

半導体集積回路

半導体装置

半導体装置

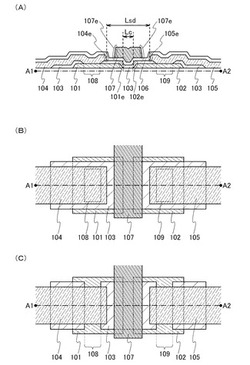

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

電界効果トランジスタ及びその製造方法、並びに半導体装置

【課題】横型二重拡散構造を有する電界効果トランジスタの高集積化を可能とする半導体装置を提供する。

【解決手段】半導体装置1Nは、ゲート電極17の幅方向両側のうちの一方の側で延在するP型ボディ領域20Pと、他方の側で延在するN型ボディ領域20Nと、その一方の側に形成されてP型ボディ領域20Pと接合するP型不純物拡散領域32Pと、その他方の側でP型不純物拡散領域32Pと対向する位置に形成されてN型ボディ領域20Nと接合するN型不純物拡散領域32Nと、その一方の側に形成されてP型ボディ領域30Nと接合するN型不純物拡散領域31Nと、その他方の側でN型不純物拡散領域31Nと対向する位置に形成されてN型ボディ領域20Nと接合するP型不純物拡散領域31Pとを備える。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

半導体装置

【課題】半導体装置においてチップサイズに影響を与えないデカップリング容量を得る。

【解決手段】半導体装置は、基板1、10と、高濃度拡散層領域11と、第1ウェル4と、第2ウェル3とを具備している。基板1、10は第1導電型である。高濃度拡散層領域11は基板1、10上に形成され、第1導電型である。第1ウェル4は基板1、10上に形成され、高濃度拡散領域11の一方側に設けられ、第1導電型である。第2ウェル3は基板1、10上に形成され、高濃度拡散領域11の他方側に設けられ、第1導電型と逆導電型となる第2導電型である。第2ウェル3と高濃度拡散領域11との間、及び、第2ウェル3と基板1、10との間でデカップリング容量が形成される。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】半導体装置において、所望の数のトランジスタをハンドリングすること。

【解決手段】半導体装置は、半導体基板内に形成された第1導電型の第1から第4の拡散層と、半導体基板内に形成された第2導電型の第5から第8の拡散層と、第1と第2の拡散層の間及び第5と第6の拡散層の間の上方に形成された第1の電極と、第3と第4の拡散層の間及び第7と第8の拡散層の間の上方に形成された第2の電極と、第6の拡散層と第7の拡散層との間の上方に形成された絶縁膜及び第3の電極を備える。第3の電極は、第1電位に接続されている。

(もっと読む)

半導体装置及びそのレイアウト作成方法

【課題】半導体装置及びその製造方法において、ゲート電極部の幅及びゲート電極部からの突き出し長のばらつきを低減する。

【解決手段】半導体装置は、ゲート電極部及び突き出し部を有する実パターン431と、実パターン431に並んで配置されるダミーパターン433とを含む複数のラインパターンを備える。2つのダミーパターン433と、これらに挟まれ且つ実パターン432を含むラインパターンとにより、同一間隔を空けて並走するラインパターン並走部が構成される。ラインパターン並走部の各ラインパターンは、同一の幅を有すると共に、互いに実質的に面一なライン終端部414を有する。各ライン終端部414の延長線上に、同一の終端部間距離403を空けて、ライン終端部均一化ダミーパターン420が形成される。ライン終端部均一化ダミーパターン420は、ラインパターンと同一幅で且つ同一間隔に形成された複数のライン状のパターンを含む。

(もっと読む)

スタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法

【課題】複数のスタンダードセルを有する半導体装置のチップ面積をさらに小さくする。

【解決手段】半導体装置SD1は第1および第2スタンダードセルSC1,SC2を備える。第1スタンダードセルSC1は、拡散領域An11、拡散領域An11に対向する機能素子領域FE1、および金属層MT11を有する。第2スタンダードセルSC2は、拡散領域An11に連続する拡散領域An21、拡散領域An21に対向する機能素子領域FE2、ならびに拡散領域An21および機能素子領域FE2の間に形成された拡散領域CR21を有する。金属層MT11および機能素子領域FE2は、拡散領域An11、拡散領域An21、および拡散領域CR21通して電気的に接続される。

(もっと読む)

半導体集積回路の設計方法

【課題】フォトリソグラフィ工程で生じる光近接効果に起因するゲート長のばらつきとゲートの寄生容量のばらつきを抑制し、標準セルの実際の特性を反映させたライブラリを設計可能とし、これにより設計マージンを小さくして高性能な半導体集積回路を提供する。

【解決手段】標準セルSc1を配列して半導体集積回路を設計する方法において、標準セルSc1を構成するゲートパターン5の端部に、該ゲートパターン5と垂直な方向にダミーパターン3を配置し、該ダミーパターン3の配置により、ゲートパターン5の端部での該ゲートパターンの占有密度の低下を補う。

(もっと読む)

絶縁層の下の埋め込み裏面制御ゲートを有するSeOI基板上のデータパスセル

【課題】基本データパスセルに基づいてSeOI(絶縁体上半導体)基板上に製造された半導体デバイスに関する。

【解決手段】本発明は、第1の態様によれば、絶縁層によってバルク基板から分離された半導体材料の薄層を備えた、絶縁体上半導体の基板上に製造された集積回路内で用いるために特にそれ自体の環境に適合されたデータパスセルであって、セルは電界効果トランジスタのアレイを備え、各トランジスタは薄層内に、ソース領域(S7)と、ドレイン領域(D7)と、ソースおよびドレイン領域によって境界付けられたチャネル領域(C7)とを有し、チャネル領域の上に形成された表面ゲート制御領域(GA7)をさらに含むセルにおいて、少なくとも1つのトランジスタ(T7)は、チャネル領域の下のバルク基板内に形成された裏面ゲート制御領域(GN2)を有し、裏面ゲート領域はトランジスタの性能特性を変更するようにバイアスすることが可能であることを特徴とするセルに関する。

(もっと読む)

絶縁膜下の埋め込みバック・コントロール・ゲートを有するSeOI上の同型のトランジスタからなる回路

【課題】リソグラフィーパターン転写に存在する変動性によって発生する問題の解決、STIを使用せず、構造を厳密化して空間を節約すること、転写されるべきより規則的かつ緻密な構造の提供。

【解決手段】SeOI基板上に形成された半導体デバイスであり、電界効果トランジスタから形成された行の形で配置されパターンのアレイを備え、電界効果トランジスタのチャンネル領域の上方に形成されたフロント・コントロール・ゲート領域を備え、各行に含まれるソース領域およびドレイン領域も同じ寸法を有し、かつ所定の寸法を有するフロント・コントロール・ゲート領域だけ隔てられ、パターンに含まれる少なくとも1つのトランジスタT1〜T4がチャンネル領域の下方に存在するベース基板内に形成されたバック・コントロール・ゲート領域を有し、トランジスタのしきい電圧をシフトさせて、バック・コントロール・ゲート領域がバイアスされることを可能とする。

(もっと読む)

半導体集積回路および半導体集積回路設計方法

【課題】チップサイズを縮小化すること。

【解決手段】第1領域に形成される活性領域1と第2領域に形成されるウェル領域2とトランジスタゲート電極3とダミーゲート電極5と、コンタクト8とを備えている。活性領域1とトランジスタゲート電極3とは、トランジスタを形成している。トランジスタゲート電極3とダミーゲート電極5とは、互いに平行である複数の直線にそれぞれ沿うように形成されている。ダミーゲート電極5は、その第2領域とその第1領域との両方に配置されるように形成されている。コンタクト8は、その第2領域に形成され、ウェル領域2に同電位である配線層6にダミーゲート電極5を電気的に接続している。このような装置は、活性領域1とウェル領域2とが配置される領域のレイアウトサイズを小さくすることができ、その結果、チップサイズを縮小化することができる。

(もっと読む)

半導体集積回路装置

【課題】近年のCMOS型LSIの設計においてはリーク電力の削減が非常に大きな課題となっている。リーク電力を削減する手段としてはトランジスタの閾値電圧を複数使用し、速度の必要な場所には閾値電圧の低いトランジスタを、不要な場所には閾値電圧の高いトランジスタを使用する方法が広く用いられている。しかしながら先端プロセスほど閾値電圧制御だけではリーク電力が十分に抑制できず、様々なリーク電力削減手法が必要となってきている。

【解決手段】本願の一つの発明は、CMOSまたはCMIS型LSIにおいて、一部の論理ゲートを構成するPチャネルFETおよびNチャネルFETの両側のゲート電極形状を近接効果を利用して平面的に湾曲させることによって、実効的なゲート長を長くするものである。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置のレイアウト方法

【課題】半導体装置の面積を大きくすることなくデカップリング容量を確保する。

【解決手段】機能ブロック12がPMOS領域14とNMOS領域16とに分割され、PMOS領域14には複数のP型のMOS−FET18、NMOS領域16には複数のN型のMOS−FET20が配置され、P型のMOS−FET18とN型のMOS−FET20とがそれぞれ対向して配置されており、P型のMOS−FET18及びN型のMOS−FET20が配置されていないPMOS領域14の空領域にデカップリング容量としてP型のMOS容量22を、NMOS領域16の空領域にN型のMOS容量24を、空領域の形状に応じた形状で形成して配置する。

(もっと読む)

半導体集積回路

【課題】順方向基板バイアス電圧をかけたときの、Vthの異なるトランジスタの速度の向上率をほぼ均等にすることのできる半導体集積回路を提供する。

【解決手段】低VthのPMOSトランジスタが形成されるNウェル領域(WN)11へは、基板バイアス供給部VP1から基板バイアスVbsP1を供給し、高VthのPMOSトランジスタが形成されるNウェル領域(WN)12−1、12−2、12−3へは、基板バイアス供給部VP2から基板バイアスVbsP2を供給する。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びレイアウト設計プログラム

【課題】チップサイズが小さくなるように、半導体集積回路を設計できるレイアウト設計装置を提供する。

【解決手段】ネットリスト及び遅延情報に基づいて、タイミング解析を行うタイミング解析部103と、タイミング解析にタイミングエラーが生じる場合、タイミングエラーに関連している調整対象セルを抽出する調整対象抽出部104と、第1セル枠は調整対象セルの境界線であり、第2セル枠の外側に第1拡散領域を有する複数の補強フィルセルを格納する補強フィルセルライブラリ105と、第2セル枠は複数の補強フィルセルの各々の境界線であり、調整対象セルに隣接する通常フィルセルと同じ大きさの第1補強フィルセルを、複数の補強フィルセルから抽出し、第1セル枠と第2セル枠とが隣接配置するように通常フィルセルを第1補強フィルセルに置き換え、トランジスタと第1拡散領域とを接続するセル置換部106とを具備する。

(もっと読む)

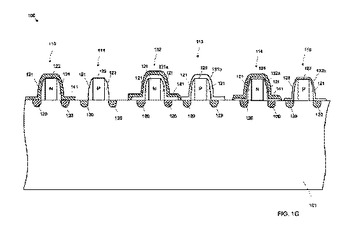

ストレス低減層を有する集積回路装置

集積回路装置が開示され、集積回路装置はNMOSゲート薄膜スタック(122)を覆う張力ストレス層(141)を有するデュアルストレスライナーNMOSデバイス(110)と、PMOSゲート薄膜スタック(123)を覆う圧縮ストレス層(142)を有するデュアルストレスライナーPMOSデバイス(111)と、張力ストレス層(141)とNMOSゲート薄膜スタック(124)との間に延在するストレス低減層(131a)を有する低減ストレスのデュアルストレスライナーNMOSデバイス(112)と、圧縮ストレス層(142)とPMOSゲート薄膜スタック(125)との間に延在するストレス低減層(131b)を有する低減ストレスのデュアルストレスライナーPMOSデバイス(113)とを含む。発明の実施形態において、追加の低減ストレスのデュアルストレスライナーNMOSデバイス(114)と低減ストレスのPMOSデバイス(115)とは、ストレス低減層(132a,132b)の厚みおよび/または材料特性を変更することによって形成される。  (もっと読む)

(もっと読む)

標準セル、標準セルライブラリおよび半導体集積回路

【課題】ゲートもしくはダミーゲートのゲート長が不規則な標準セルにおいて、特性のばらつきを抑制する。

【解決手段】本発明の標準セルでは、他のトランジスタと異なるゲート長を有するトランジスタの両隣のトランジスタのうち少なくとも一方のトランジスタは常にオフ状態とする。これにより、ゲート仕上がり寸法がばらついても標準セルの動作には影響を与えないので、標準セルの特性のばらつきを抑制することができる。

(もっと読む)

1 - 20 / 76

[ Back to top ]