Fターム[5F048BA07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 多層基板(2層) (997) | 基板と直上の層が異型 (194)

Fターム[5F048BA07]に分類される特許

1 - 20 / 194

半導体装置

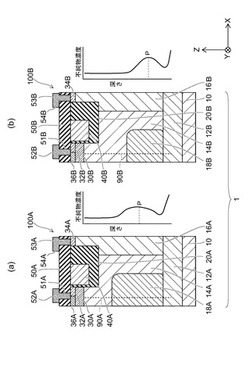

【課題】横型DMOSの素子面積の増大を抑制し高耐圧化をはかる。

【解決手段】第1の半導体素子100Aは、第1半導体層12Aと、第2半導体層14Aと、第2半導体層に隣接する第3半導体層16Aと、第1絶縁層20Aと、第2半導体層の表面に選択的に設けられた第1ベース領域30Aと、第1ベース領域の表面に選択的に設けられた第1ソース領域32Aと、第1絶縁層の内部に設けられた第1ゲート電極40Aと、第1ベース領域の下に設けられ、第1半導体層の表面から第1ベース領域の側に延在する第1ドリフト層18Aと、第1ソース領域32Aに対向し、第1絶縁層20Aを挟んで第3半導体層16Aの表面に設けられた第1ドレイン領域34Aを有す。第1ドリフト層18Aの不純物元素の濃度は、第1半導体層12Aの不純物元素の濃度よりも低い。第1ドリフト層の不純物元素の濃度は、第2半導体層14Aの不純物元素の濃度よりも高い。

(もっと読む)

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するドライバトランジスタ(Dr1)が配置される活性領域(Ac)の下部に、絶縁層(BOX)を介して、素子分離領域(STI)により囲まれたn型のバックゲート領域(nBG)を設け、ドライバトランジスタ(Dr1)のゲート電極(G)と接続する。また、n型のバックゲート領域(nBG)の下部に配置され、少なくともその一部が、素子分離領域(STI)より深い位置に延在するp型ウエル領域(Pwell)を設け、接地電位(VSS)に固定する。かかる構成によれば、トランジスタの閾値電位(Vth)をトランジスタがオン状態の時には高く、逆に、オフ状態の時には低くなるように制御し、また、p型ウエル領域(Pwell)とn型のバックゲート領域(nBG)との間のPN接合も順バイアスさせないよう制御することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置、半導体ウエハ、及びこれらの製造方法

【課題】トランジスタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】SOI基板101は、P型半導体層102の上にN型半導体層104が形成された半導体基板12、その上に形成されたBOX層106、及びBOX層上に形成されたSOI層108を有する。第1素子分離絶縁層110bは、SOI基板101に埋め込まれ、下端16がP型半導体層102に達し、第1素子領域(NFET領域30)と第2素子領域(PFET領域40)とを分離する。P型トランジスタ130bは、第1素子領域40に位置し、チャネル領域120bを有し、N型トランジスタ130aは、NFET領域30に位置し、チャネル領域120aを有する。第1バックゲートコンタクト134bは、第1素子領域40に位置する第2導電型層層104に、第2バックゲートコンタクト134aは、第2素子領域30に位置する第2導電型層104に接続される。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置

【課題】ブートストラップ方式のドライブ回路を有する半導体装置において、ブートストラップダイオードの順バイアス時にp-基板側に流れるホールによるリーク電流を抑制することができる半導体装置を提供することにある。

【解決手段】ブートストラップダイオードDb下にSON構造の空洞3を形成し、ブートストラップダイオードDbとグランド電位(GND)となるGNDp領域4との間のn-エピ層2にその空洞3に達するフローティングp領域5を形成することで、外部のブートストラップコンデンサC1充電時のp-基板1へのホールによるリーク電流を抑えることができる。

(もっと読む)

半導体装置

【課題】たとえばDC−DCコンバータ等の電源または電力変換機器のスイッチング等に使用されるパワーMOSFET等の絶縁ゲートを有するパワー系能動素子は、スイッチングの高速化に伴い、ゲート容量を極力小さくする必要がある。このためには、チャネルとならない部分のゲート電極を取り去り、スプリットゲートとする手法が有効とされている。しかし、Nチャネル型パワーMOSFETを例に取り説明すると、その反作用として、チャネルを形成するP型ボディ領域の端部に電界が集中するため、パンチスルー耐圧が低下する等の問題が発生する。

【解決手段】本願の一つの発明は、プレーナ−バーティカル型パワーMOSFET等の絶縁ゲートを有するパワー系能動素子を有する半導体装置に於いて、各アクティブセル内のスプリットゲート間にトレンチ内に延在するフィールドプレート、すなわち、トレンチフィールドプレートを設けたものである。

(もっと読む)

電界効果トランジスタ及びその製造方法、並びに半導体装置

【課題】横型二重拡散構造を有する電界効果トランジスタの高集積化を可能とする半導体装置を提供する。

【解決手段】半導体装置1Nは、ゲート電極17の幅方向両側のうちの一方の側で延在するP型ボディ領域20Pと、他方の側で延在するN型ボディ領域20Nと、その一方の側に形成されてP型ボディ領域20Pと接合するP型不純物拡散領域32Pと、その他方の側でP型不純物拡散領域32Pと対向する位置に形成されてN型ボディ領域20Nと接合するN型不純物拡散領域32Nと、その一方の側に形成されてP型ボディ領域30Nと接合するN型不純物拡散領域31Nと、その他方の側でN型不純物拡散領域31Nと対向する位置に形成されてN型ボディ領域20Nと接合するP型不純物拡散領域31Pとを備える。

(もっと読む)

半導体装置

【課題】不要な寄生素子の影響を排除できる低容量の過渡電圧保護素子を提供する。

【解決手段】半導体基板上に第1のエピタキシャル層210を形成し、第1のエピタキシャル層の表面近傍に埋め込み層220を形成し、埋め込み層上に第2のエピタキシャル層211を形成し、第2のエピタキシャル層内に第1のディープ拡散層250を形成し、第1のディープ拡散層内にツェナーダイオードを形成し、ツェナーダイオードから離れた位置に第1のPNダイオードを形成し、ツェナーダイオードは第1の分離層240により分離されており、第1のPNダイオードは第2の分離層241で分離されており、ツェナーダイオードと第1のPNダイオードが埋め込み層を経由して逆方向に直列接続されることにより、不要な寄生素子の影響を排除でき、かつ低容量の過渡電圧保護素子を実現する。

(もっと読む)

半導体装置

【課題】オン抵抗の低減を実現できる、高耐圧のLDMOSトランジスタを有する半導体装置を提供する。

【解決手段】半導体基板上に配置された第2導電型の第1半導体領域と、第1半導体領域の上面の一部に埋め込まれた第1導電型の第2半導体領域と、第2半導体領域の上面の一部に埋め込まれた第2導電型のソース領域と、第2半導体領域と離間して第1半導体領域の上面の一部に埋め込まれた第2の導電型のドレイン領域と、ソース領域とドレイン領域間で第2半導体領域上に配置されたゲート電極と、第2半導体領域とドレイン領域間で第1半導体領域上に配置された絶縁膜と、絶縁膜上に配置されてゲート電極とドレイン領域間の電圧を分圧する分圧素子と、分圧素子とドレイン領域との間に接続された電荷移動制限素子とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

半導体装置

【課題】逆耐圧を高くしてもオン抵抗が高くなることのない半導体装置を提供する。

【解決手段】n型半導体層116と、n+型半導体層116よりも低濃度のn型不純物を含有するn型のドリフト層112と、ドリフト層112の表面に形成した、拡散深さが深いボディ部分118aと、拡散深さが浅いチャネル部分118bとからなるp型のボディ領域118と、ボディ領域118の表面に形成したn+型のソース領域120と、チャネル部分118bの上にゲート絶縁層122を介して形成したゲート電極124とを備える半導体装置であって、平面的に見てボディ領域118と重ならない領域に位置するドリフト層112には、ドリフト層112よりも高濃度のn型不純物を含有するn型の低抵抗領域144aがn+型半導体層116と接するように形成されている半導体装置100。

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

横型素子を有する半導体装置

【課題】高速スイッチング動作を行う場合でも、アバランシェブレークダウンを抑制でき、スイッチング損失低減や素子破壊を抑制することが可能な構成とする。

【解決手段】横型FWD7などの横型素子において、SRFP21の全抵抗Rの抵抗値を90kΩ〜90MΩ、好ましくは270kΩ〜27MΩ、より好ましくは900kΩ〜9MΩとすることにより、2ndピーク時のアノード電流IAなどの電流が大きくなることを抑制できる。これにより、高速スイッチング動作を行う場合でもアバランシェブレークダウンを抑制でき、横型FWD7のスイッチング損失低減や素子破壊を抑制することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】工程が簡単で、よりラッチアップに強いCMOS構造を得る。

【解決手段】1×1018cm−3から1×1019cm−3の高不純物濃度の半導体基板2を用い、CMOS構造のP型ウェル4とN型ウェル5の境界に設けられた溝分離部13の先端部分がその高不純物濃度領域に達する(エピタキシャル層3を貫通して半導体基板2の領域に至る)ように深く形成することにより、従来のように溝分離部13よりも更に深い領域(溝分離部13の下側)を電子が通過することなく、従来のようにウェル領域内にN+埋め込み層やP+埋め込み層を基板深く埋め込む必要もなく、簡便な方法で、よりラッチアップに強いCMOS構造を得ることができ、コスト性能の両方に優れた半導体装置1を得ることができる。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置

【課題】半導体基板に向かって流れ込む回生電流又は寄生バイポーラトランジスタのオン電流を、チップサイズを増大させることなく低減できるLDMOSトランジスタの実現が課題となる。

【解決手段】N+型ドレイン層13等が形成されたN型エピタキシャル層5からなるN型層5aを、N型エピタキシャル層5の表面からN+型埋め込み層2まで延在するP型ドレイン分離層6で取り囲む。P型ドレイン分離層6とP型素子分離層3に囲まれたN型エピタキシャル層5からなるN型層5bにその表面から内部に延在するP型コレクタ層7を形成する。これにより第1導電型のドレイン分離層6をエミッタ、前記第2導電型の分離層5bをベース、前記コレクタ層7をコレクタとする寄生バイポーラトランジスタを形成しサージ電流を接地ラインに流す。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

半導体集積回路のESD保護素子およびそのESD保護回路

【課題】電源電圧以下の維持電圧Vhでも良好なESD保護を行う。

【解決手段】半導体集積回路のESD保護回路11は、電位端子とグランド電位間に、スナップバック動作を持つ第1のESD保護素子1としてのggMOSトランジスタと、スナップバック動作を持つESD保護素子1のスナップバック動作電圧Vt1に対して、低いブレークダウン電圧Vrを持ち、かつ高い破壊電圧Vt2を持つ第2のESD保護素子2としてのダイオードとが並列に接続されている。

(もっと読む)

1 - 20 / 194

[ Back to top ]