Fターム[5F048BA09]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 基板中に絶縁層 (137)

Fターム[5F048BA09]に分類される特許

121 - 137 / 137

結晶方向の異なるシリコン層を備えたシリコン−オン−インシュレータ半導体デバイスと、シリコン−オン−インシュレータの半導体デバイスを形成する方法

第1の結晶方位を有する基板12と、この基板12を覆う絶縁層40を含む半導体デバイスが提供される。この絶縁層を覆って、複数のシリコン層16、30が形成される。第1シリコン層16は、第1の結晶方位を有するシリコンを含み、第2シリコン層30は、第2の結晶方位を有するシリコンを含む。加えて、基板12と、この基板12を覆うシリコン層16と、基板12とシリコン層16と間に設けられた第1絶縁層14を含むシリコン−オン−インシュレータ構造を提供する半導体デバイスを形成する方法が提供されている。シリコン層16および第1絶縁層14の一部を取り除くことでシリコン−オン−インシュレータ構造の第1領域を形成し、基板層12の一部24をさらす。選択的エピタキシャルシリコン30は、開口部に成長される。開口部22で成長されたシリコン30に第2絶縁層40が形成され、開口部22で成長されたシリコン30と基板12との間に絶縁層40が提供される。  (もっと読む)

(もっと読む)

高出力半導体デバイスのための半導体構造体の作成方法

高出力半導体デバイスのための基材配置物は、SiCウエハの表面上に付着させたSi層を有するSiCウエハを包含する。Si第1層、SiO2中間層およびSi第3層を有するSOI構造体が、そのSi第3層を、SiCウエハ上に付着させたSiに接着して、単一構造体を形成する。SOIのSi第1層およびSiO2中間層を除去して、純粋なSi第3層を残し、この上にさまざまな半導体デバイスを製作することができる。Si第3層および付着Si層を、1種以上の半導体デバイスをSiCウエハ上に製作することができるように基材配置物の一部にわたり除去してもよい一方、他の半導体デバイスを純粋なSi第3層上に対応させてもよい。 (もっと読む)

半導体装置およびその製造方法

【課題】SOS基板を用いた半導体装置に形成するnMOS素子のオン電流を増加させる手段を提供する。

【解決手段】サファイア基板に単結晶シリコン層を積層したSOS基板の単結晶シリコン層に形成したnMOS素子のチャンネル領域とサファイア基板との間に絶縁膜層を形成し、絶縁膜層上の単結晶シリコン層の応力状態を引張応力状態にする。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチゲート構造を有する横型のパワー半導体装置において、アバランシェ降伏がバルク領域で起こるようにすること。

【解決手段】n+ソース領域6aとn-拡張ドレイン領域2との間のチャネル領域を、均一な濃度のpエピタキシャル層21で構成し、n-拡張ドレイン領域2とpエピタキシャル層21とのpn接合付近に不連続な濃度分布を生じさせる。そして、n-拡張ドレイン領域2とpエピタキシャル層21の濃度を最適化して、n-拡張ドレイン領域2とpエピタキシャル層21との接合界面でポテンシャルが密となり、一方、ゲート酸化膜7とn-拡張ドレイン領域2との界面でポテンシャルが疎となるようにすることによって、バルク領域でブレークダウンが起こるようにする。

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 SOI基板を用いることなく、SOI構造とバルク構造とを同一基板上に形成する。

【解決手段】 第1半導体層5および第2半導体層6を半導体基板1上のSOI形成領域E1に順次選択的に形成し、第2半導体層6が覆われるようにしてSOI形成領域R1およびバルク領域R2上に酸化防止膜8を形成し、第1半導体層5の端部の一部を露出させる開口部9を酸化防止膜8および犠牲酸化膜7に形成し、開口部9を介してエッチングガスまたはエッチング液を第1半導体層5に接触させることにより、第1半導体層5をエッチング除去し、半導体基板1および第2半導体層6の熱酸化を行うことにより、半導体基板1と第2半導体層6との間の空洞部10に酸化膜11を形成する。

(もっと読む)

高移動性バルク・シリコンPFET

【課題】 従来のPFETに比べて減少されたシリコン面積および電力消費での高速のスイッチング速度をもつ改良されたPFETと、改良されたPFETと同時に製造されることができるNFETとの両方を提供すること。

【解決手段】 電界効果トランジスタ(100)及び電界効果トランジスタを製造する方法である。電界効果トランジスタは、ゲート誘電体層(155)の上面(170)に形成されたゲート電極(165)と、単結晶シリコン・チャネル領域(110)の上面(160)のゲート誘電体層と、Ge含有層(135)の上面の単結晶シリコン・チャネル領域と、単結晶シリコン基板(150)の上面のGe含有層と、単結晶シリコン基板の上面における第1誘電体層(215A)と第2誘電体層(215B)との間のGe含有層とを含む。

(もっと読む)

部分SOI基板およびその製造方法

【課題】

活性層とバルク層との連続部分にエピタキシャル成長させる必要がなく、ボイドも発生しない部分SOI基板およびその製造方法を提供する。

【解決手段】

水素ガスの雰囲気で、シリコン酸化膜14の一部に窓部14aが形成されたSIMOX基板10を高温アニールする。その際、埋め込み酸化膜13のうち、活性層11とバルク層12とを連続させる一部の領域が、埋め込み酸化膜13に含まれた酸素の熱拡散によって消滅し、部分SOI構造が形成される。その結果、部分SOI構造の形成時、活性層11とバルク層12とが連続した部分にエピタキシャル成長を行う必要がない。しかも、貼り合わせ方式による部分SOI構造でないので、部分SOI基板20の内部にボイドも発生しない。

(もっと読む)

半導体装置

【課題】 同一基板上にゲート絶縁膜の耐圧の異なる複数の電界効果型トランジスタを設ける際に、これを簡便なプロセスで作製する。

【解決手段】 シリコン基板101上に高耐圧トランジスタ102および低耐圧トランジスタ104が形成された半導体装置100において、高耐圧トランジスタ102のポリシリコンゲート電極膜117のゲート不純物濃度を低耐圧トランジスタ104のゲート不純物濃度よりも小さくする。

(もっと読む)

半導体装置

【課題】 SOI基板上に、完全空乏型の高速MOSトランジスタと、高耐圧型MOSトランジスタとを混載した高精度なアナログICが形成された半導体装置を安価に提供すること。

【解決手段】 ブリーダ抵抗はSOI基板上の単結晶シリコンデバイス形成層で形成し、それぞれのブリーダ抵抗の上面には、高速MOSトランジスタのゲート絶縁膜及びゲート電極により抵抗値固定用電極を形成し、下部に位置するブリーダ抵抗と同電位になるようにした。

(もっと読む)

歪みSOI基板

【課題】 本発明は電子やホールの移動度が良好で、シリコンとSiGe層の界面でのミスフィット転位による貫通転位が少ない歪みSOI基板を提供する。

【解決手段】 本発明の歪みSOI基板は、シリコン基板の上に、埋め込み絶縁膜層、歪み誘起絶縁膜層、歪みシリコン層が順次形成された歪みSOI基板である。好ましくは、歪み誘起絶縁膜層と歪みシリコン層の、室温から1000℃までの平均熱膨張係数の差が、0.5×10-6/℃より大きい歪みSOI基板を使用することにより、電子やホールの移動度が良好で、かつリーク特性の良好なデバイスが得られる。

(もっと読む)

特徴の異なる結晶性半導体領域を有する基板の形成技術

第1結晶性半導体領域104a内に誘電領域111を形成することによって、単一基板上に異なるタイプの結晶性半導体領域が与えられる。その後、この誘電領域111上には、第2結晶領域152aがウェハ接合技術によって位置決めされる。好ましい実施形態では、誘電領域とともに、第1結晶領域にアイソレーション構造が形成されてもよい。特に、結晶方向の異なる結晶性半導体領域が形成されてもよく、高度なフレキシビリティと、現在利用されているCMOSプロセスとの互換性が維持される。  (もっと読む)

(もっと読む)

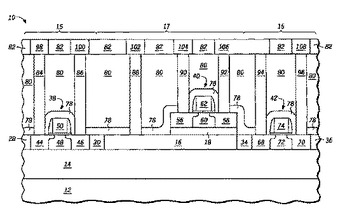

複数の半導体層を備えた半導体デバイス

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

半導体装置

【課題】同一なチップ内でNチャネルおよびPチャネルの両チャネルが高い耐圧特性を有する高耐圧MOSトランジスタを実現でき得るデバイス構造の製造方法を提供する。

【解決手段】本発明は、Nch型L−DMOS101 とPch型L−DMOS102と論理部103 から成る半導体装置であり、Nch型L−DMOS101 は、N型ドリフト領域12、Pウエル19、P型高濃度拡散層20、ソース拡散層21、ドレイン拡散層22、ソースコンタクト14、ドレインコンタクト16、ソース電極配線15、ドレイン電極17、ゲート電極18の各主要素から成り、SOI領域であるN型ドリフト領域12に形成されたこのNch型L−DMOS101のソース電極14と、領域11と、を電気的に導通して同電位になるように構成するデバイス構造である。

(もっと読む)

ローカルSOIを備えた半導体装置を形成するための方法

半導体・オン・インシュレータ・トランジスタ45が、バルクのシリコン基板12から形成される。活性領域は基板12上に画定され、単結晶である酸素リッチ型シリコン層は活性領域の頂部面に形成される。この酸素リッチ型シリコン層の上に、シリコンのエピタキシャル層が成長する。シリコンのエピタキシャル層が形成された後に、酸素リッチ型シリコン層が、該エピタキシャル層の少なくとも一部を単結晶シリコンとして残した状態にてシリコン酸化物24に変換される。これは、高温水蒸気をエピタキシャル層に適用することにより実施される。得られたものがトランジスタ45を形成するのに有用なシリコン・オン・インシュレータ構造体10であり、該トランジスタにおいて、ゲート誘電体26が残りの単結晶シリコン上に存在し、該ゲート28はゲート誘電体26上に存在し、かつ、ゲート28の下側にある残りの単結晶シリコン内にチャネル36が存在する。  (もっと読む)

(もっと読む)

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

バンド設計超格子を有する半導体装置を製作する方法

複数の積層された層群を有する超格子を形成するステップによって、半導体装置を製作する方法である。また当該方法は、前記超格子を通って、前記積層された層群と平行な方向に、電荷キャリアの輸送が生じる領域を形成するステップを有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。前記エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取りこまれた、少なくとも一つの非半導体分子層を有し、前記超格子は、超格子が存在しない場合に比べて、前記平行な方向において大きな電荷キャリア移動度を有する。また前記超格子は、共通のエネルギーバンド構造を有しても良い。

(もっと読む)

(もっと読む)

半導体装置、画像表示装置、半導体装置の製造方法、及び画像表示装置の製造方法

【課題】 CMOS−TFTを構成するp型及びn型TFTの各しきい値電圧を独立に効率良く(最小限のフォトリソグラフィーで)高精度に制御する。

【解決手段】 CMOS−TFTを製造するに際して、しきい値電圧(Vthp ,Vthn )制御として極低濃度にp型不純物(B:ボロン)の非選択的添加(p型及びn型TFTの双方に添加)及び選択的添加(n型TFTのみに添加)を連続的に行なう。具体的には、当初図4(a)のようにId −Vg 特性がp型及びn型TFT共に負シフトした状態から、非選択的添加により図4(b)のようにp型及びn型TFT共に正シフトさせてVthp を先ず仕様値とし、続いて選択的添加によりn型TFTのみ正シフトさせてVthn を仕様値に調整する。

(もっと読む)

121 - 137 / 137

[ Back to top ]