Fターム[5F048BB06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 多結晶Si (4,558) | N型ドープ多結晶Si (1,205)

Fターム[5F048BB06]に分類される特許

201 - 220 / 1,205

半導体装置およびその製造方法

【課題】複数の閾値を有し、ダストや不純物の局所的なばらつきによる歩留りの低下や、信頼性の低下を抑えることが可能な半導体装置とその製造方法を提供する。

【解決手段】半導体基板(Sub.)に形成された第1導電型のMOSFETと第2導電型のMOSFETを有し、前記第1導電型のMOSFETは、第1導電型の不純物を含む第1のゲート電極15aと、第2導電型の不純物を含む第2のゲート電極15bとを備え、前記第2導電型のMOSFETは、第1導電型の不純物を含む第3のゲート電極15cと、第2導電型の不純物を含む第4のゲート電極15dとを備える。

(もっと読む)

半導体構造体およびその形成方法(内部応力を有する半導体ナノワイヤ)

【課題】高性能の相補型金属半導体(CMOS)回路の為の高いオン電流をもたらす半導体ナノワイヤ・デバイスを提供する。

【解決手段】両方の端部に半導体パッド33A、37Aを有する半導体ナノワイヤ32が、基板上にサスペンドされる。半導体ナノワイヤが応力発生ライナ部によって長手方向の応力を受けている間、半導体ナノワイヤの中間部の上にゲート誘電体36及びゲート電極38が形成される。ゲート誘電体及びゲート電極の形成によって半導体ナノワイヤの歪み状態が固定されるため、半導体ナノワイヤの中間部は、応力発生ライナの除去後に長手方向の固有の内部応力を受ける。半導体パッド内にソース及びドレイン領域33B,37Bが形成され、半導体ナノワイヤ・トランジスタが得られる。ソース及びドレイン・パッドの上に、中間工程(MOL)誘電体層を直接形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタとp型MISトランジスタとにおいてサイドウォール幅が同一である場合、n型MISトランジスタの高信頼性とp型MISトランジスタの高性能化を両立させることは難しい。

【解決手段】半導体装置は、n型MISトランジスタとp型MISトランジスタとを備えている。n型MISトランジスタは、半導体基板10における第1の活性領域10a上に順次形成された第1のゲート絶縁膜13a及び第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール16aとを備えている。p型MISトランジスタは、半導体基板10における第2の活性領域10b上に順次形成された第2のゲート絶縁膜13b及び第2のゲート電極14bと、第2のゲート電極14bの側面上に形成された第2のサイドウォール16bとを備えている。第2のサイドウォール16bは、第1のサイドウォール16aに比べてサイドウォール幅が小さい。

(もっと読む)

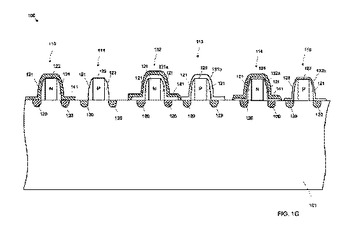

ストレス低減層を有する集積回路装置

集積回路装置が開示され、集積回路装置はNMOSゲート薄膜スタック(122)を覆う張力ストレス層(141)を有するデュアルストレスライナーNMOSデバイス(110)と、PMOSゲート薄膜スタック(123)を覆う圧縮ストレス層(142)を有するデュアルストレスライナーPMOSデバイス(111)と、張力ストレス層(141)とNMOSゲート薄膜スタック(124)との間に延在するストレス低減層(131a)を有する低減ストレスのデュアルストレスライナーNMOSデバイス(112)と、圧縮ストレス層(142)とPMOSゲート薄膜スタック(125)との間に延在するストレス低減層(131b)を有する低減ストレスのデュアルストレスライナーPMOSデバイス(113)とを含む。発明の実施形態において、追加の低減ストレスのデュアルストレスライナーNMOSデバイス(114)と低減ストレスのPMOSデバイス(115)とは、ストレス低減層(132a,132b)の厚みおよび/または材料特性を変更することによって形成される。  (もっと読む)

(もっと読む)

半導体素子およびその製造方法

【課題】チャンネル長および延長ソース/ドレイン領域のドーピング条件によって閾値電圧を調製できる半導体素子の提供。

【解決手段】SOI構造の半導体層の上に形成された高Vt素子と、前記半導体層の上に形成され、高Vt素子よりも低い閾値電圧を有する低Vt素子とを有し、高Vt素子と低Vt素子とはMOSFET素子であって、延長ソース領域と延長ドレイン領域との間の部分であるチャンネルを有し、高Vt素子は低Vt素子よりもチャンネル長が長いSOI構造の半導体素子。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁層上の半導体層に形成された部分空乏型のトランジスターにおいて、高いON/OFF比と、安定動作を同時に実現できるようにした半導体装置及びその製造方法を提供する。

【解決手段】BOX層1上のSOI層2に形成された部分空乏型のトランジスター10と、ダイオード20とを備え、トランジスター10は、SOI層2上に絶縁膜13を介して形成されたゲート電極14と、ゲート電極14の両側下のSOI層2に形成されたN型のソース15a又はドレイン15bとを有し、ダイオード20は、SOI層2の浅い部分に形成されたP型不純物層21と、SOI層2の深い部分に形成されたN型不純物層22と、を有する。P型不純物層21と、N型不純物層22は深さ方向に積層されており、P型不純物層21の側面とN型不純物層22の側面はそれぞれトランジスター10のボディ領域2に接している。

(もっと読む)

半導体装置の製造方法

【課題】

製造工程を簡略化しつつ、特性の優れた第1のMOSトランジスタと第2のMOSトランジスタとを製造する半導体装置の製造方法を提供する。

【解決手段】

半導体基板に、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域を画定する素子分離領域を形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域に第1導電型の不純物をイオン注入し、第1導電型のウェルを形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域上に絶縁ゲート電極を形成し、第2のMOSトランジスタのドレイン領域を覆うマスクを介して、半導体基板法線方向から傾いた複数方向から第1導電型の不純物をイオン注入し、第1のMOSトランジスタ領域の前記絶縁ゲート電極下方に対称的なチャネルドーズ領域、第2のMOSトランジスタ領域の前記絶縁ゲート電極下方に非対称なチャネルドーズ領域を形成し、半導体装置を製造する。

(もっと読む)

半導体装置

【課題】FD型トランジスタで構成された電気回路において、電気回路に電力を供給する電源のスイッチングトランジスタを基板電圧で制御することができる半導体装置を提供する。

【解決手段】半導体装置は、基板上の第1のFinに形成された第1のトランジスタを含む電気回路と、半導体基板上の第2のFinに形成され、電気回路と電源供給線との間に接続された第2のトランジスタを含む電源回路と、基板に基板電圧を印加するための基板コンタクトとを備え、第1のFinの幅は、第1のトランジスタのチャネル部に形成される最大空乏層幅の2倍以下であり、第2のFinの幅は、第2のトランジスタのチャネル部に形成される最大空乏層幅の2倍よりも大きい。

(もっと読む)

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

ソース/ドレイン延長部、ハローポケット及びゲート誘電体厚さの異なる構成を有する同極性の電界効果トランジスタの構成及び製造

【課題】 一群の高性能同極性絶縁ゲート電界効果トランジスタ(100,108,112,116,120及び124又は102,110,114、118,112及び126)が、アナログ及び/又はデジタル適用例用の広く多様なトランジスタを提供する半導体製造プラットフォームに適した横方向ソース/ドレイン延長部、ハローポケット、及びゲート誘電体厚さの選択可能な異なる構成を有している。

【解決手段】 各トランジスタは、一対のソース/ドレインゾーン、ゲート誘電体層、及びゲート電極を有している。各ソース/ドレインゾーンは主要部分及び一層軽度にドープした横方向延長部を有している。該トランジスタの内の一つのソース/ドレインゾーンの内の一つの横方向延長部が該トランジスタの別のもののソース/ドレインゾーンの内の一つの横方向延長部よりも一層高度にドープされており又は/及びそれよりも上部半導体表面下側により少ない深さに延在している。

(もっと読む)

複数の局所的濃度最大によって画定されたソース/ドレイン延長部を有する電界効果トランジスタの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(100W)は、半導体ボディのボディ物質(180)のチャンネルゾーン(244)によって横方向に分離されているソース(980)及びドレイン(242)を有している。

【解決手段】 ゲート電極(262)が該チャンネルゾーンの上方でゲート誘電体層(260)の上側に位置している。該ボディ物質の一層高度にドープしたポケット部分(250)が、通常、該ソースのみにほぼ沿って延在しており、従って該IGFETは非対称的装置である。該ソースを画定する半導体ドーパントはソース延長部を画定する場合に複数の局所的濃度最大に到達する。2つのこの様な局所的濃度最大に到達する半導体ドーパントで該ソース延長部を画定する場合に関与する手順は、3個の絶縁ゲート電界効果トランジスタ用の相互に異なる特性のソース/ドレイン延長部を2つのソース/ドレイン延長部ドーピング操作のみで画定することを可能とする。

(もっと読む)

半導体装置及びその製造方法

【課題】N型MIS−FETとP型MIS−FETとを含む半導体装置において、N型トランジスタ及びP型トランジスタに対してそれぞれ最適な応力を印加できるようにする。

【解決手段】素子分離領域である第1絶縁領域101に、周囲に引っ張り応力を与える第2絶縁領域107と、周囲に圧縮応力を与える第3絶縁領域108とが形成されている。第2絶縁領域107及び第3絶縁領域108は、N型MIS−FET50に対しては第1の活性領域103の周辺に電子の移動方向に対して垂直な方向及び平行な方向にそれぞれ引っ張り応力を与えるように配置される。P型MIS−FET60に対しては第2の活性領域104の周辺に正孔の移動方向に対して平行な方向に圧縮応力を与える一方、正孔の移動方向に対して垂直な方向に引っ張り応力を与えるように配置されている。

(もっと読む)

非対称的チャンネルゾーン及び異なる構成としたソース/ドレイン延長部を有する非対称的電界効果トランジスタの構成及び製造

【課題】 非対称的絶縁ゲート電界効果トランジスタ(100又は102)は半導体ボディのボディ物質(180又は182)のチャンネルゾーン(244又は284)によって横方向に分離されたソース(240又は280)及びドレイン(242又は282)を有している。

【解決手段】 ゲート電極(262又は302)が該チャンネルゾーンの上方でゲート誘電体層(260又は300)の上側に位置している。該ボディ物質の一層高度にドープしたポケット部分(250又は290)がほぼ該ソースのみに沿って延在している。該ソースは、主要ソース部分(240M又は280M)と、一層軽度にドープした横方向ソース延長部(240E又は280E)とを有している。該ドレインは、主要ドレイン部分(242M又は282M)と、一層軽度にドープした横方向ドレイン延長部(242E又は282E)とを有している。該ドレイン延長部は該ソース延長部よりも一層軽度にドープされている。これら2つの延長部を画定する半導体ドーパントの最大濃度は、該ソース延長部におけるよりも該ドレイン延長部において一層深くに発生する。付加的に又は代替的に、該ドレイン延長部は該ソース延長部よりも該ゲート電極下側を更に横方向に延在する。これらの特徴はスレッシュホールド電圧が動作時間に関して高度に安定であることを可能とする。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

延長型ドレイン電界効果トランジスタを有する半導体構成体の構成及び製造

【課題】 拡張型ドレイン絶縁ゲート電界効果トランジスタ(104又は106)が、第1ウエル領域(184A又は186A)の一部によって構成されているチャンネル(322又は362)ゾーンによって横方向に分離されている第1及び第2ソース/ドレインゾーン(324及び184B又は364及び186B/136B)を包含している。

【解決手段】 ゲート誘電体層(344又は384)が該チャンネルゾーンの上側に存在している。該第1ソース/ドレインゾーンは、通常は、ソースである。通常はドレインである該第2S/Dゾーンは、少なくとも部分的には第2ウエル領域(184B又は186B)で構成されている。該半導体ボディのウエル分離部分(136A又は212U/136B)が該ウエル領域の間を延在しており且つ各ウエル領域よりも一層軽度にドープされている。該ウエル領域の構成は、該半導体ボディのIGFETの部分における最大電界をして上部半導体表面の十分に下側、典型的には該ウエル領域同士が互いに最も近い箇所におけるか又はその近くで発生させる。該IGFETの動作特性は動作時間と共に安定である。

(もっと読む)

ソース/ドレイン延長部又は/及びハローポケットと組み合わせて空のウエルを使用した電界効果トランジスタの構成及び製造

【課題】 混合信号適用例を含むアナログ及びデジタル適用例用のIGFETを与える半導体製造プラットフォームに適した対称的及び非対称的の両方の絶縁ゲート電界効果トランジスタ(「IGFET」)が、高性能を達成する上で空のウエル領域を使用する。

【解決手段】 各空のウエルの上部近くにおいては半導体ウエルドーパントが比較的少量である。各IGFET(100,102,112,114,124又は236)は、空のウエル(180,182,192,194,204又は206)のボディ物質のチャンネルゾーンによって横方向に分離された一対のソース/ドレインゾーンを有している。ゲート電極が該チャンネルゾーン上方でゲート誘電体層の上側に位置している。各ソース/ドレインゾーン(240,242,280,282,520,522,550,552,720.722、752又は752)が主要部分(240M,242M,280M,282M,520M,522M,550M,552M,720M,722M,752M又は752M)及び一層軽度にドープした横方向延長部(240E,242E,280E,282E,520E,522E,550E,552E,720E,722E,752E又は752E)を有している。代替的に又は付加的に、該ボディ物質の一層高度にドープしたポケット部分(250又は290)が該ソース/ドレインゾーンの内の一方に沿って延在する。存在する場合には、該ポケット部分は典型的に該IGFETを非対称的装置とさせる。

(もっと読む)

L形状スペーサを使用した非対称的電界効果トランジスタの製造及び構成体

【課題】 非対称的電界効果トランジスタ(102)の製造は、半導体ボディのボディ物質のチャンネルゾーン(284)の上方でそれからゲート誘電体層(300)によって垂直方向に分離されているゲート電極(302)を画定することとなる。

【解決手段】 該ゲート電極をドーパント阻止用シールドとして使用して、半導体ドーパントを該ボディ物質内に導入させて、一層高度にドープしたポケット部分(290)を画定する。該ゲート電極に沿ってスペーサ(304T)を設ける。該スペーサは、(i)該ゲート電極に沿って位置されている誘電体部分、(ii)該半導体ボディに沿って位置されている誘電体部分、及び(iii)該他の2つのスペーサ部分の間の空間をほぼ占有するフィラー部分(SC)、を包含している。該ゲート電極及び該スペーサをドーパント阻止用シールドとして使用して、半導体ドーパントを該半導体ボディ内に導入させて、一対のソース/ドレイン部分(280M及び282M)を画定する。該フィラースペーサ部分を除去して該スペーサをL形状(304)へ変換させる。一対の電気的コンタクト(310及び312)を夫々該主要ソース/ドレイン部分に対して形成する。

(もっと読む)

液晶表示装置

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

電界効果トランジスタのソース延長部及びドレイン延長部が異なるドーパントで画定される半導体構成体の構成及び製造

【課題】 半導体ボディの上部表面に沿って設けられた絶縁ゲート電界効果トランジスタ(100)は、チャンネルゾーン(244)によって横方向に分離された一対のソース/ドレインゾーン(240及び242)を有している。

【解決手段】 ゲート電極(262)が該チャンネルゾーン上方でゲート誘電体層(260)の上側に存在している。各ソース/ドレインゾーンは、主要部分(204M又は242M)及び該主要部分と横方向に連続的であり且つ該ゲート電極下側を横方向に延在する一層軽度にドープした横方向延長部(240E又は242E)を包含している。該横方向延長部は、該チャンネルゾーンを上部半導体表面に沿って終端させており、異なる原子量の一対の半導体ドーパントによって夫々ほぼ画定される。該トランジスタが非対称的装置であり、該ソース/ドレインゾーンはソース及びドレインを構成する。該ソースの横方向延長部は該ドレインの横方向延長部よりも一層軽度にドープされており且つ一層高い原子量のドーパントで画定される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】チャネル間の相互影響を抑制しつつ、少なくとも3F2のレイアウトを実現する。

【解決手段】半導体記憶装置1は、Y方向に垂直な2側面のうちの一方の側面12aの領域13aに第1のチャネルCH1、他方の側面12bのうちY方向に見て領域13aと重ならない領域13bに第2のチャネルCH2がそれぞれ設けられるとともに、これらの側面12a,12bの他の領域が酸化されて絶縁酸化膜とされたシリコンピラー11と、それぞれゲート絶縁膜14a,14bを介して側面12a,12bを覆う2本のワード線WLとを備え、第1のチャネルCH1と第2のチャネルCH2とが、上記絶縁酸化膜によって絶縁分離されている。

(もっと読む)

201 - 220 / 1,205

[ Back to top ]