Fターム[5F048BB06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 多結晶Si (4,558) | N型ドープ多結晶Si (1,205)

Fターム[5F048BB06]に分類される特許

161 - 180 / 1,205

半導体装置

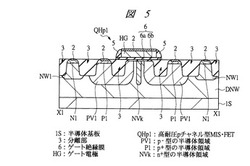

【課題】高耐圧の電界効果トランジスタを有する半導体装置のキンク現象を抑制または防止する。

【解決手段】高耐圧pMISQHp1のチャネル領域のゲート幅方向の両端の溝型の分離部3と半導体基板1Sとの境界領域に、高耐圧pMISQHp1のソースおよびドレイン用のp+型の半導体領域P1,P1とは逆の導電型のn+型の半導体領域NVkを、高耐圧pMISQHp1の電界緩和機能を持つp−型の半導体領域PV1,PV1(特にドレイン側)に接しないように、そのp−型の半導体領域PV1,PV1から離れた位置に配置した。このn+型の半導体領域NVkは、溝型の分離部3よりも深い位置まで延在されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】アンチヒューズ素子が導通状態の際に形成される導電パスの電気抵抗を低くし、また、抵抗値のばらつきを抑制することができる半導体装置を提供する。

【解決手段】アンチヒューズ素子4を備えた半導体装置1であって、前記アンチヒューズ素子4は、半導体基板5に設けられたウェル41と、前記ウェル41上に設けられた絶縁膜42と、前記絶縁膜42上に設けられ、前記ウェル41と同じ導電型のポリシリコン膜43と、前記ウェル41内の一面41a側に設けられた、前記ウェル41と同じ導電型の不純物導入領域46とを備え、前記不純物導入領域46の不純物濃度が、前記ウェルの不純物濃度よりも高く、前記不純物導入領域46は、前記ポリシリコン膜43の前記ウェル41上に位置する端部と前記絶縁膜42を介して対向する部分を備えていることを特徴とする。

(もっと読む)

半導体装置

【課題】

活性領域と素子分離領域を別個の対象として応力を制御し,半導体装置の性能を向上する。

【解決手段】

半導体装置は、p−MOS領域を有する半導体基板と、半導体基板表面部に形成され、p−MOS領域内にp−MOS活性領域を画定する素子分離領域と、p−MOS活性領域を横断して,半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、p−MOSゲート電極構造を覆って、p−MOS活性領域上方に選択的に形成された圧縮応力膜と、p−MOS領域の素子分離領域上方に選択的に形成され,圧縮応力膜の応力を解放している応力解放領域と、を有し、p−MOSチャネル領域にゲート長方向の圧縮応力とゲート幅方向の引張応力を印加する。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数を十分に制御することができ、閾値電圧の変動を抑制した半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10に第1導電型チャネルMOSFETを備える。第1導電型チャネルMOSFETは、例えばPチャネルMOSFETであって、半導体基板10の上に設けられたゲート絶縁膜21と、ゲート電極65とからなる。ゲート電極65は、ゲート絶縁膜21の上に設けられた金属ゲート電極20と、金属ゲート電極20の上に設けられた金属酸化膜24と、金属酸化膜24の上に設けられた金属ゲート電極26と、を含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】同一半導体チップ内に形成されたNチャネルパワーTDMOSトランジスタとPチャネルパワーTDMOSトランジスタの双方のオン電流に対するオン抵抗の低減を図る。

【解決手段】NチャネルパワーTDMOSトランジスタ用トレンチ4の長辺側とPチャネルTDMOSトランジスタ用トレンチ4の長辺側を45°傾けて形成する。これによりNチャネル側のトレンチ4の長辺側の側壁を(100)面とし、Pチャネル側のトレンチ4の長辺側の側壁を(110)面として、Nチャネル側の電流担体である電子及びPチャネル側の電流担体である正孔の移動度を高くする。移動度を高くすることによりチャネル部分の導電率を高める。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗値のバラツキが小さく良好な特性を示す抵抗素子を有し、高速に動作可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板11内に形成された素子分離領域12と、第1の活性領域13Aと、第2の活性領域13Bと、第1の活性領域13A上に形成され、第1導電型不純物が導入されたシリコンからなる第1導電型ゲート電極16Aを有する第1導電型MISトランジスタと、第2の活性領域13B上に形成され、第2導電型不純物が導入されたシリコンからなる第2導電型ゲート電極16Bを有する第2導電型MISトランジスタと、素子分離領域12上に形成され、p型不純物が導入されたシリコンからなり、n型ゲート電極16A及びp型ゲート電極16Bよりも抵抗値の大きいp型抵抗体16Dとを備えている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】高誘電率ゲート絶縁膜として機能するHf含有絶縁膜4a,4b上にメタルゲート電極であるゲート電極GE1,GE2が形成され、ゲート電極GE1,GE2は、金属膜7a,7b,7cの積層膜からなる金属膜7とその上のシリコン膜8との積層構造を有している。金属膜7の最下層の金属膜7aは、窒化チタン膜、窒化タンタル膜、窒化タングステン膜、炭化チタン膜、炭化タンタル膜または窒化タングステン膜からなり、金属膜7bは、ハフニウム膜、ジルコニウム膜またはアルミニウム膜からなり、金属膜7cは、金属膜7aと同種の材料からなる膜である。

(もっと読む)

半導体集積回路装置

【課題】アンテナスイッチのスイッチング用トランジスタにSOI MOSFETを用いながら、高調波歪を大幅に低減する。

【解決手段】アンテナスイッチの受信分路スルーMOSFETグループ13を構成するトランジスタ44〜48のドレイン−ゲート間の片方に静電容量素子54〜58を付加することにより、ソース−ゲート間とドレイン−ゲート間の電圧振幅が同じでなくなる。その結果、ソース−ドレイン間寄生容量の電圧依存は、電圧の極性に対して非対称となる。この非対称性は、同様の非対称性を有する信号歪を発生させるので、それを基板容量の電圧依存による2次高調波と同等の振幅と逆の位相を持つように設定することにより、2次高調波歪を打ち消すことができ、2次高調波歪を低減することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】各々ばらつきの少ない異なる閾値電圧を有する複数のトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板2上に形成された高誘電率材料を母材料とするゲート絶縁膜11、ゲート電極12、およびゲート絶縁膜11に接するように形成されたSiNを主成分とする絶縁材料からなるオフセットスペーサ13、を有する低閾値電圧MISFET10と、半導体基板2上に形成された高誘電率材料からなるゲート絶縁膜21、ゲート電極22、およびゲート絶縁膜21に接するように形成されたSiNを主成分とする絶縁材料からなるオフセットスペーサ23、を有する高閾値電圧MISFET20と、を有し、オフセットスペーサ23は、オフセットスペーサ13よりも、単位体積当たりのSi−H結合とN−H結合の存在比、単位体積当たりのClの量、および単位体積当たりのHの量の少なくともいずれか1つが大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の信頼性を向上させる。特に、nチャネル型のMOSFETにおけるVthのローカルばらつきAvtを低減させる。

【解決手段】co−impla技術を用い、nチャネル型のMOSFETのエクステンション領域9aに窒素をシリコン基板1の主面に対して垂直もしくは垂直に近い角度(0〜3度)で打ち込むことにより、窒素が打ち込まれて形成された欠陥トラップ層もしくはアモルファス層がアニ−ル後のシリコン基板1表面近傍への不純物のパイルアップを軽減するため、チャネル表面近傍のドーパントの濃度が低減し、シリコン基板1表面近傍における不純物プロファイルの揺らぎ成分が軽減される。その結果、チャネル表面近傍の不純物揺らぎ起因のローカルばらつきを抑制することができる。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】第1の逆スタガ型薄膜トランジスタ及び第2の逆スタガ型薄膜トランジスタにより構成されるEDMOS回路を有する論理回路部を有し、第1の逆スタガ型薄膜トランジスタは、第1のゲート電極、ゲート絶縁層、第1の半導体層、第1の一対の不純物半導体層、及び第1の一対の配線を有し、第1の半導体層は、ドナーとなる不純物元素を含む微結晶半導体層と、混合領域と、非晶質半導体を含む層とが積層され、第2の逆スタガ型薄膜トランジスタは、第2のゲート電極、ゲート絶縁層、第2の半導体層、第2の一対の不純物半導体層、及び第2の一対の配線を有し、第2の半導体層は、微結晶半導体層と、非晶質半導体層とが積層されている表示装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】同一の工程で、同一半導体基板上に異なる構造のトランジスタを形成する半導体装置の提供。

【解決手段】半導体基板上に第一及び第二のゲート電極40,41を形成する工程と、第一のゲート電極の側壁面に第一の絶縁層122を形成するとともに、第二のゲート電極のゲート幅方向両側の半導体基板上にエピタキシャル成長層9aを形成する工程と、第二のゲート電極の側壁面に第二の絶縁層を形成する工程と、第一の絶縁層及び第二の絶縁層を覆うように第三の絶縁層を形成する工程と、第二の絶縁層を覆う第三の絶縁層を除去する工程と、第一のゲート電極のゲート幅方向両側の半導体基板及びエピタキシャル成長層にそれぞれ不純物を拡散させて、第一及び第二の不純物拡散領域6,8を形成する工程と、第一及び第二の不純物拡散領域にコンタクトプラグ12,15を接続させる工程と、を具備してなることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エミッタ電極の膜厚が均一であり、このために素子特性のばらつきが少ない特性が良好な半導体装置を提供する。

【解決手段】Si基板1上のN−hill層11と、N−hill層11を囲む素子分離領域であるシャロートレンチアイソレーション6に開口されたオープン領域21と、を備えたHCBT100を含む半導体装置において、オープン領域21上に面方位のないアモルファスSi膜30,31を形成する。アモルファスシリコン膜30、31を、N−hill層11がアモルファスシリコン膜30、31から露出する厚みにまでエッチングして電極とする。

(もっと読む)

半導体装置

【課題】10GHz程度以上のクロック周波数での動作が可能な高速半導体装置の提供。

【解決手段】n−MOSFET100n、p−MOSFET100pを有し、n−MOSFETのチャンネルを形成する第1の領域の表面が(100)面から±10°以内の面または(110)面から±10°以内の面のを有し、p−MOSFETのチャンネルを形成する第2の領域の表面が((110)面から±10°以内の面または(100)面から±10°以内の面のを有し、第1及び第2の領域の各々から各々の両端の前記ソース電極、ドレイン電極の各々までの抵抗を4Ω・μm以下とし、かつ第1の領域と第1のゲート絶縁層との界面及び第2の領域と第2のゲート絶縁層との界面を、各領域のソースからドレインに向かう方向での長さ2nmにおけるピーク・トゥ・バレイが0.3nm以下であるような平坦度とした半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】導電型に応じて容易に構成を変えることが可能なFinトランジスタ及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に設けられた凸状の半導体からなるトランジスタ活性領域104と、トランジスタ活性領域104の一部の側面上及び上面上に設けられたゲート絶縁膜105aと、ゲート絶縁膜105aを間に挟んでトランジスタ活性領域104の側面及び上面の一部上に設けられたゲート電極350とを備えている。ゲート電極350のうち、トランジスタ活性領域104の側面上に設けられた部分の構成とトランジスタ活性領域104の上面上に設けられた部分の構成とは互いに異なっている。

(もっと読む)

半導体装置及びその製造方法、固体撮像素子

【課題】生産性良く、歩留まり良く製造することを可能にする構造の半導体装置を提供する。

【解決手段】n型の不純物が導入された電極層15と、その上の不純物が導入されていない電極層17との積層構造であるゲート電極21を含む、縦型のNMOSトランジスタと、電極層15とその上の電極層16との積層構造であるゲート電極22,23を含む、平面型のNMOSトランジスタと、電極層15とその上のp型の不純物が導入された電極層17との積層構造であり、p型の電極であるゲート電極24を含む、平面型のPMOSトランジスタと、縦型のNMOSトランジスタの下に形成された、フォトダイオード等の他の回路素子とを含む半導体装置を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 抵抗素子の抵抗値の選択範囲を拡大し、且つ抵抗層形成後にシリサイドブロックを形成せずに該抵抗層のシリサイド化を防止することを可能にする。

【解決手段】 半導体領域11上に絶縁膜15を形成し、絶縁膜15を介して半導体領域11に不純物のイオン注入12を行う。これにより、絶縁膜15の下に抵抗層13が形成されるとともに、抵抗層13に隣接して電極領域14が形成される。その後、電極領域14の表面にシリサイド膜17を形成する。このとき、絶縁膜15は、抵抗層13がシリサイド化されることを防止するシリサイドブロックとして機能する。イオン注入12として、同一半導体基板上に形成されるMOSトランジスタのソース/ドレイン領域への不純物注入工程を利用し得る。

(もっと読む)

161 - 180 / 1,205

[ Back to top ]