Fターム[5F048BB06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 多結晶Si (4,558) | N型ドープ多結晶Si (1,205)

Fターム[5F048BB06]に分類される特許

81 - 100 / 1,205

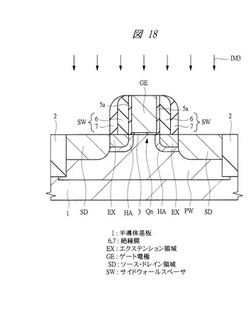

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】イオン注入により半導体基板1にエクステンション領域EXを形成してから、ゲート電極GEの側壁上にサイドウォールスペーサSWを形成し、その後、イオン注入により半導体基板1にソース・ドレイン領域SDを形成する。サイドウォールスペーサSWを形成するには、半導体基板1上にゲート電極GEを覆うように絶縁膜6を形成してから、この絶縁膜6を異方性エッチングし、その後、半導体基板1上にゲート電極GEを覆うように絶縁膜7を形成してから、この絶縁膜7を異方性エッチングすることで、ゲート電極GEの側壁上に残存する絶縁膜6,7からなるサイドウォールスペーサSWを形成する。絶縁膜6のエッチング工程では、絶縁膜6をアンダーエッチングまたはジャストエッチングし、絶縁膜7のエッチング工程では、絶縁膜7をオーバーエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において工程数の削減を図ること。

【解決手段】領域HVp、LVn、LLnに第1〜第3のゲート電極36a〜36cを形成する工程と、領域LVnを覆い、かつ、領域HVpと領域LLnを露出するマスクパターン40を形成する工程と、マスクパターン40をマスクにしたイオン注入でp型ソースドレインエクステンション41とp型ポケット領域42を形成する工程と、マスクパターン40をマスクにしたイオン注入でn型ソースドレインエクステンション45を形成する工程と、領域HVpと領域LLnを覆い、かつ、第2の領域LVnを露出するマスクパターン52を形成する工程と、マスクパターン52をマスクにしてインジウムをシリコン基板1にイオン注入し、p型ポケット領域54を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】イオン注入で所定の元素をゲート電極に導入して、異なる仕事関数を有するゲート電極のMOSトランジスタを形成する際に、製造工程の増加を抑制して低コストの半導体装置を提供する。

【解決手段】半導体装置の製造方法では、導電膜上5a,5bにおいて、第1の領域1aから第2の領域1bまでを覆う第1のマスク6b、第2の領域の上方にスペース部7b、及び第2の領域1bから第3の領域1cまでを覆う第2のマスク6cを有するマスクパターンを設ける。スペース部内、並びに第1及び第2のマスクの第1の側面にサイドウォール膜7aを設ける。第1の側面に接するサイドウォール膜の下に位置する導電膜の領域内に不純物を注入する。サイドウォール膜をマスクに用いて異方性エッチングを行うことによりゲート絶縁膜及びゲート電極を形成してMOSトランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置およびその製造方法

【課題】周辺回路の抵抗素子の抵抗部の厚さに依らずにメモリセルトランジスタの浮遊ゲートの厚さを自由に設定することのできる半導体装置、およびその製造方法を提供すること。

【解決手段】基板上の抵抗素子およびスタックド・ゲート型のメモリセルトランジスタを含む半導体装置を提供する。前記抵抗素子は、抵抗として機能しない非導通層、および前記非導通層上に第1の絶縁膜を介して形成された抵抗として機能する導通層を含む。前記メモリセルトランジスタは、第1の浮遊ゲートを含む浮遊ゲートを有する。前記非導通層と前記第1の浮遊ゲートは、同じ材料からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38上に第1ストッパ膜39及び第2ストッパ膜40を形成する工程と、第1領域2を覆う第1マスク60をマスクとし、第1ストッパ膜をストッパとして、第2領域4内の第2ストッパ膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の第2ストッパ膜をサイドエッチングする工程と、第2ストッパ膜とエッチング特性が異なる第2応力膜42を形成する工程と、第2領域を覆い、第1領域側の端面が第2ストッパ膜上に位置する第2マスクとし、第2ストッパ膜をストッパとして、第2応力膜の一部が第1応力膜の一部及び第2ストッパ膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

MOSトランジスタおよびその製造方法、半導体集積回路装置

【課題】MOSトランジスタのチャネル領域に、基板上に形成した応力膜からより効率的に応力を印加する半導体装置の構造及びその製造方法を提供する。

【解決手段】MOSトランジスタは、n型またはp型のソース・ドレイン領域21e〜hと、素子分離領域21Iからチャネル領域に向かって延在し、ソース・ドレイン領域21e〜hを覆って形成された、引張応力、圧縮応力のいずれかである応力膜27A、27Bを備える。応力膜27A,27Bは、ゲート電極23A,23Bの側壁面に沿って、ただし側壁面からは隙間32A〜Dを介して形成される。ソース・ドレイン領域21e〜hがn型である場合、応力膜の応力は引張応力であり、ソース・ドレイン領域21e〜hがp型である場合、応力膜の応力は圧縮応力である。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】規則的に配列した複数の微細な開口部OPを有するフィルタFLを通過したイオンビーム22をレンズ26で収束して半導体ウエハ1Wに照射することにより、チャネルドープイオン注入を行なう。この際、フィルタFLには、イオンビーム22と同じ極性の電圧を印加する。フィルタFLの開口部OPの中央部に向かって入射した不純物イオンは、そのまま直進して開口部OPを通過することができるが、フィルタFLの開口部OPの中央部以外の領域に向かって入射する不純物イオンは、フィルタFLによる電場によって進行方向が曲げられて、開口部OPを通過することができない。このため、半導体ウエハ1Wに注入された不純物イオンは、規則的な配列を有したものとなり、MISFETのしきい値電圧のばらつきを抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】高耐電圧により大電流化が可能で、オン抵抗が低く高速動作が可能で、高集積化と省エネルギーが可能で、素子間分離の容易な、電気熱変換素子駆動用の半導体装置を提供する。

【解決手段】電気熱変換素子とそれに通電するためのスイッチング素子とがp型半導体基体1に集積化されている。スイッチング素子は、半導体基体1の表面に設けられたn型ウェル領域2と、それに隣接して設けられチャネル領域を提供するp型ベース領域6と、その表面側に設けられたn型ソース領域7と、n型ウェル領域2の表面側に設けられたn型ドレイン領域8,9と、チャネル領域上にゲート絶縁膜を介して設けられたゲート電極4とを有する絶縁ゲート型電界効果トランジスタである。ベース領域6は、ドレイン領域8,9を横方向に分離するように設けられた、ウェル領域2より不純物濃度の高い半導体からなる。

(もっと読む)

半導体装置の製造方法

【課題】p型MOSトランジスタの半導体埋め込み領域形成に付随する不具合が抑制される技術を提供する。

【解決手段】半導体装置の製造方法は、n型、p型MOSトランジスタの配置される第1、第2活性領域にまたがりシリコンでゲート電極を形成する工程と、第1活性領域とその近傍のゲート電極へのn型不純物注入工程と、第2活性領域及びその近傍のゲート電極を露出するマスクの形成工程と、マスク開口内の第2活性領域及びゲート電極をエッチングする凹部形成工程と、凹部表面の自然酸化膜を除去しこれに伴い開口が後退する工程と、凹部表面をハロゲンガスでクリーニングする工程と、凹部への半導体埋め込み領域形成工程とを有し、クリーニング工程時に後退した開口内にゲート電極上n型領域が露出していないように、ゲート電極上n型領域の第2活性領域側の端とマスク開口の第1活性領域側の縁とが離される。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの特性を劣化させることなくポリシリコン抵抗素子を製造できる半導体装置の製造方法を提供する。

【解決手段】半導体基板30の抵抗素子形成領域に抵抗素子となるポリシリコン膜35aを形成するとともに、トランジスタ形成領域にポリシリコンゲート35b及び高濃度不純物領域40を形成する。その後、全面に絶縁膜41を形成した後、トランジスタ形成領域をフォトレジスト膜42で覆い、ポリシリコン膜35aに導電性不純物をイオン注入する。次いで、フォトレジスト膜42をアッシングにより除去する。このとき、トランジスタは絶縁膜41に覆われているため、アッシングによるダメージが回避される。また、抵抗素子領域に導入された導電性不純物が大気中のO及びHと反応して酸が発生しても、ポリシリコンゲート及び高濃度不純物領域40が酸により溶解することが回避される。

(もっと読む)

半導体薄膜基板および半導体薄膜基板を用いた半導体装置の作製方法

【課題】一層の半導体層から膜厚の異なる半導体層を有する半導体薄膜基板を提供することを目的の一とする。または、半導体薄膜基板を適用した半導体装置を提供することを目的の一とする。

【解決手段】基板上に半導体層を形成し、半導体層を加工して第1の島状半導体層および第2の島状半導体層を形成し、第1の島状半導体層にレーザー照射を行うことにより第1の島状半導体層を溶融させ、第1の島状半導体層から第2の島状半導体層より膜厚が厚い第3の島状半導体層を形成する、半導体薄膜基板の作製方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】電源配線の電位の変動に起因するボディ領域の電位の変動を抑制し得る半導体装置を得る。

【解決手段】シリコン層4の上面内には、パーシャルトレンチ型の素子分離絶縁膜5が選択的に形成されている。電源配線21は、素子分離絶縁膜5の上方に形成されている。電源配線21の下方において、素子分離絶縁膜5には、絶縁層3の上面に達する完全分離部分23が形成されている。換言すれば、半導体装置は、電源配線21の下方において、シリコン層4の上面から絶縁層3の上面に達して形成された完全分離型の素子分離絶縁膜を備えている。

(もっと読む)

半導体装置の製造方法

【課題】工程数が多く、煩雑になる問題を解決する半導体装置の製造方法を提供する。

【解決手段】半導体基板1に第1絶縁膜2を形成し、第1領域Aに第1導電型の第1ウエル層31を形成し、第1領域A以外の第1絶縁膜2上に第1半導体膜3を形成し、第1ウエル層31にトランジスタを形成し、第1半導体膜3及び第1領域Aの第1絶縁膜2の上に、トランジスタのビットコンタクトを兼ねる第2半導体膜7を形成する工程、第2半導体膜7上に、第2領域用B1のマスク8を積層してから、第1または第2導電型ドーパントを注入して第2ウエル層32を形成し、次いで、第2領域B1の少なくとも第2半導体膜7に、ドーパントを注入する工程、第2半導体膜7上に導電膜を積層してから、第1、第2半導体膜3,7及び導電膜を部分的にエッチングして、第1領域Aにトランジスタのビット配線層を、第2領域B1,B2に別の配線層を形成する工程、を具備する。

(もっと読む)

半導体基板の作製方法及び半導体装置の作製方法

【課題】平坦性の高い表面を有する単結晶半導体層を備えた半導体基板の作製方法を提供することを目的の一とする。平坦性の高い単結晶半導体層を備えた半導体基板を用いて信頼性の高い半導体装置を作製することを目的の一とする。

【解決手段】半導体基板の作製工程において、単結晶半導体基板に希ガスイオン照射工程、レーザー照射工程および水素イオン照射工程を行うことで、単結晶半導体基板の所定の深さに大きな結晶欠陥を含有した薄い脆化領域を形成し、剥離加熱工程を行うことで脆化領域より表面側の単結晶半導体層をベース基板に転載する。

(もっと読む)

81 - 100 / 1,205

[ Back to top ]