Fターム[5F048BC20]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 複数MOSの相互のS・D領域が異なるもの (1,340) | 濃度が異なるもの (151)

Fターム[5F048BC20]に分類される特許

101 - 120 / 151

半導体装置および半導体装置の製造方法

【課題】リーク電流を低減した省電力型の半導体装置を提供する。

【解決手段】複数の素子形成領域と、前記複数の素子形成領域にわたって形成されるゲート電極と、前記ゲート電極により導通状態または非導通状態とされる、前記素子形成領域の第1の領域および第2の領域とを有し、前記ゲート電極は、第1の方向に延伸する部分が第1の素子形成領域上に、該第1の方向と異なる第2の方向に延伸する部分が第2の素子形成領域上にそれぞれ形成され、前記第1の素子形成領域の前記第1の領域と前記第2の領域のうち、非導通状態で低電圧となる低電圧領域の近傍には、該低電圧領域と異なる導電型のポケット領域が形成されていることを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】所望する性能を有する付加される電圧が互いに異なる3種類またはそれ以上のMISFETを内蔵する半導体装置を製造コストの増加を抑えて形成することのできる技術を提供する。

【解決手段】例えば1.2V系nMIS、1.8V系nMISおよび3.3V系nMISの3種類のnMISを同一の半導体基板1に形成する場合、基準となる1.2V系nMISでは最適性能が得られるように、ゲート絶縁膜の厚さ、ゲート電極7のゲート長およびn型拡張領域11の深さ等の構成部分の構成条件を最適化する。1.8V系nMISおよび3.3V系nMISではゲート絶縁膜の製造工程を同じとし、さらにn型拡張領域9の製造工程を同じとすることによって製造工程を減らし、他方でゲート電極7のゲート長を調整することにより、これらnMISにおいて所望する性能を得る。

(もっと読む)

半導体装置及びその製造方法

【課題】 CMOS型半導体装置に関して、低濃度ソース・ドレイン拡散層の形成に、イオン注入を用いず、熱処理を用いて逆導電型不純物を含有する絶縁膜から低濃度の逆導電型不純物を熱拡散させる場合、熱拡散源として、PSG膜とBSG膜とが必要であり、プロセスが複雑となっていた。

【解決手段】 PSG膜もしくはBSG膜のいずれかのみを熱拡散源として熱処理を行うことにより、容易に浅い低濃度ソース・ドレイン拡散領域を形成することが可能な半導体装置およびその製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】熱処理による基板とゲート絶縁膜形成膜との界面へのフッ素の導入工程の際に、フッ素の外方拡散が起こることを防止する。

【解決手段】半導体基板100上における素子形成領域にゲート絶縁膜形成膜102、103を形成した後、ゲート絶縁膜形成膜102、103上にゲート電極形成膜104を形成する。その後、ゲート電極形成膜104上にフッ素を含有する絶縁膜105を形成する。その後、熱処理により、半導体基板100とゲート絶縁膜形成膜102、103との界面に、フッ素を含有する絶縁膜105に含有されるフッ素を拡散させて導入する。

(もっと読む)

半導体装置及びその製造方法

【課題】容易に動作耐圧を向上させることができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】ドレイン側及びソース側にオフセット拡散層9、10を有するトランジスタにおいて、P型ソース領域8とソース側オフセット拡散層9の一部と空間的に重なる位置にN型の不純物拡散層30を形成する。これにより、ソース側オフセット拡散層9の一部である補償領域31の不純物が補償され、補償領域31の不純物濃度はドレイン側オフセット拡散層10よりも低濃度となる、これにより、オン抵抗が増大し、結果としてトランジスタの動作耐圧を向上させることができる。

(もっと読む)

半導体装置

【課題】本発明は、Si/SiGe基板を用いて構成されるMOSトランジスタのキャリアの移動度を向上させるために、基板上の有効な方向に応力がかかるようにすることを特徴とする。

【解決手段】Si及びSiGeの積層構造を有する半導体基板10と、半導体基板上にゲート絶縁膜を介して形成されたゲート電極15と、ゲート電極下の半導体基板表面に形成されたチャネル領域と、チャネル領域を挟むように半導体基板表面に形成されたソース・ドレイン領域17とを具備し、チャネル領域下のGe濃度とソース・ドレイン領域のGe濃度が異なる。

(もっと読む)

半導体装置及びその製造方法

【課題】面積のさらなる縮小化の可能な半導体装置及びその製造方法を提供する。

【解決手段】第2のMISトランジスタTr2の閾値制御層36を第1のMISトランジスタTr1の閾値制御層26と同条件で形成する。第2のMISトランジスタTr2のLDD拡散領域34を第3のMISトランジスタTr3のLDD拡散領域44と同条件で形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】複数のフィン型FETを含む半導体装置において、微細化しつつ複数のフィン型FETを所望の電流駆動能力を有するようにする。

【解決手段】半導体装置100は、シリコン基板102と、シリコン基板102上に形成された第1のフィン型シリコン層106および第2のフィン型シリコン層108をそれぞれ含む第1のフィン型FET170および第2のフィン型FET178とを含む。第1のフィン型シリコン層106は、第2のフィン型シリコン層108よりも高さが低い。

(もっと読む)

半導体装置

【課題】半導体装置の微細化の進展に拘わらず、ESD耐量を高く保つことができる半導体装置を提供する。

【解決手段】n型ドレイン層15に隣接し且つドレイン電極20によりドレイン層15と電気的に短絡されるように形成され静電放電時にESD保護素子の一部として機能するp型の半導体層17が形成される。p型半導体層17とドレイン層15とは、動作電流の方向とは交差する方向に並ぶように配列される。

(もっと読む)

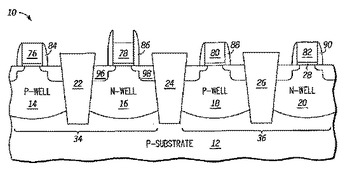

低減されたゲートドーピングを用いる半導体構造体及び同構造体を形成する方法

半導体構造体10は記憶領域34と論理領域36とを有する基板12を含む。第一のp型デバイスは記憶領域34に形成され、第二のp型デバイスは論理領域36に形成される。第一のp型デバイスの半導体ゲートの少なくとも一部は第二のp型デバイスの半導体ゲートの少なくとも一部よりもより低いp型ドーパント濃度を有する。第一及び第二のp型デバイスの半導体ゲートの各々は、ゼロではないp型ドーパント濃度を有する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】同一の半導体基板上に、コアトランジスタとI/Oトランジスタとを有し、I/Oトランジスタのゲート長の縮小が可能な構造を有する半導体装置及びその製造方法を提供する。

【解決手段】

同一の半導体基板(100)上に、コアトランジスタとI/Oトランジスタとを有する半導体装置であって、コアトランジスタは、ゲート絶縁膜(102a)と、ゲート電極(103a)と、サイドウォール(105a)と、エクステンション拡散層(104a)と、ソース・ドレイン拡散層(106a)とを備える。I/Oトランジスタは、ゲート絶縁膜(102b)と、ゲート電極(103b)と、サイドウォール(105b)と、ソースドレイン拡散層(106b)とを備える。I/Oトランジスタにおけるゲート絶縁膜(102b)の直下に位置するチャネル領域とソース・ドレイン拡散層(106b)とは、サイドウォール(105b)の直下の領域においてオフセットしている。

(もっと読む)

半導体装置、半導体装置の製造方法、並びに電気光学装置

【課題】LDD又はGOLD構造を有し、微細化に対応できるとともに歩留まりを向上させることができ、工程を簡略化できる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体膜上の全面にレジストを形成し、第1遮光部91aと、第1透光部91bと、第1遮光部91aと第1透光部91bとの間に配置された半遮光部91cとを備えたハーフトーンレクチル91と、露光時に少なくとも第1遮光部91aおよび半遮光部91cの一部が配置されるべき位置に位置合わせされる第2遮光部92aと第2遮光部92aに隣接して配置された第2透光部92bとを備えたバイナリレクチル92とを用いてレジストを露光することによってソース側高濃度領域及びドレイン側高濃度領域に対応するレジストの膜厚を、ソース側低濃度領域、ドレイン側低濃度領域及びチャネル領域に対応するレジストの膜厚より薄く形成するレジスト形成工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】 オフセット型のトランジスタを含む半導体装置であって、信頼性が向上した半導体装置の製造方法を提供すること。

【解決手段】 半導体層10に、第1素子形成領域10HV、第1素子分離絶縁層20、第2素子形成領域10LVに、第2素子分離絶縁層22を形成する工程と、第1素子形成領域10HVに、第1トランジスタ100を、第2素子形成領域10LVに、チャネルの導電型が同一である第2トランジスタ200の形成工程と、第1素子形成領域10HVに、チャネル領域108、ソース・ドレイン領域110、122、オフセット絶縁層24、第1ウエル12とガードリング形成領域120aを含む不純物領域122の形成工程と、第1ウエル12、第2ウェル14の上方にゲート絶縁層102、202、ゲート電極104、204の形成工程と、第2ウエル14に、ソース・ドレイン領域212,210を形成する。

(もっと読む)

ESD保護回路及びESD保護回路製造方法

【課題】 半導体集積回路におけるESD保護回路のソース/ドレインのレイアウト面積をさほど広く取ることなく、拡散抵抗を高くする。

【解決手段】 本発明のESD保護回路は、複数の保護トランジスタを直列又は並列に配置して形成される半導体集積回路のESD保護回路において、複数の保護トランジスタ間に設けられる拡散領域にて、拡散領域を構成する部材からなる拡散部材部位と、拡散領域を構成する部材以外の部材からなる拡散部材外部位とが、交互に櫛状に配置されることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ショートチャネル効果を抑制すると共にキャリア移動度の向上を図る半導体装置およびその製造方法を提供する。

【解決手段】シリコン基板11中、ソース領域11Sおよびドレイン領域11Dに対応してトレンチ11−1A,11−1Bを形成し、トレンチ11−1A,11−1Bをp型の不純物元素を含むSiGe混晶層19A,19Bによりエピタキシャルに充填する際に、トレンチ11−1A,11−1Bの側壁面19bをファセットにより画成し、さらに第2側壁絶縁膜18A,18Bの底面の下側のシリコン基板11の表面にSiGe混晶層19A,19Bからなる延出部19Aa,19Baを形成し、ソースエクステンション領域11EAおよびドレインエクステンション領域11EBに接触させる。

(もっと読む)

フィンFETCMOSとその製造方法及びそれを備えるメモリ素子

【課題】フィンFETCMOSとその製造方法及びそれを備えるメモリ素子を提供する。

【解決手段】基板上に備えられたn型トランジスタ、n型トランジスタ上に積層された層間絶縁層、及び層間絶縁層上に備えられたp型トランジスタ、を備えるが、n型及びp型トランジスタは、共通のゲート絶縁膜とフィンゲートとを有することを特徴とするCMOS素子である。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体膜のチャネル領域の端部におけるゲート絶縁膜の段切れや薄膜化により生じる半導体膜とゲート電極とのショートやリーク電流を抑制する半導体装置および当該半導体装置の作製方法の提供を課題とする。

【解決手段】基板上に連続して設けられた半導体膜と、半導体膜の上方にゲート絶縁膜を介して設けられた導電膜と、導電膜と重ならない半導体膜に形成されたソース領域及びドレイン領域と、導電膜の下方に位置する半導体膜であってソース領域とドレイン領域の間に形成されたチャネル領域とを有する複数の薄膜トランジスタと、導電膜と重ならない半導体膜であってソース領域及びドレイン領域と隣接して設けられた不純物領域とを有し、導電膜をチャネル領域及びチャネル領域に隣接する半導体膜上に設ける構成とする。

(もっと読む)

薄膜トランジスタ及びこれを利用した有機電界発光表示装置の製造方法

【課題】工程短縮及び工程費用の減少が可能なCMOS薄膜トランジスタ及びそれを用いたOELD装置の製造方法を提供する。

【解決手段】第1及び第2TFT領域を有する基板を提供する段階と、基板上にゲート電極を形成する段階と、ゲート電極を含んだ基板全面上にゲート絶縁膜を形成する段階と、ゲート絶縁膜の所定領域上にマスクを利用して半導体層を形成する段階と、ゲート電極を利用してマスクを背面露光する段階と、背面露光されたマスクを利用して第1及び第2TFT領域の半導体層にn型不純物イオンを注入してチャネル領域及びソース/ドレイン領域を形成する段階と、背面露光されたマスクの両側面を灰化する段階と、灰化されたマスクを利用して、第1及び第2TFT領域の半導体層に低濃度不純物イオンを注入してLDD領域を形成する段階、及び第2TFT領域の半導体層にp型不純物イオンを注入してソース/ドレイン領域を形成する段階と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 微細化してもリーク電流の増大及び不純物領域の抵抗の上昇を防止できるツェナーダイオード構造及びその製造方法を提供する。

【解決手段】 ツェナーダイオードは、pn接合を生じるように形成されたn型半導体層2並びにp型半導体層3及び4と、n型半導体層2とp型半導体層3及び4とのpn接合部を覆う絶縁膜5と、n型半導体層2と電気的に接続するカソード電極配線6aと、p型半導体層4と電気的に接続するアノード電極配線6bとを備えている。p型半導体層3及び4からなるp型半導体領域は、第1の拡散深さ及び第1のピーク濃度を持つ第1のp型不純物濃度分布と第1の拡散深さよりも浅い第2の拡散深さ及び第1のピーク濃度よりも高い第2のピーク濃度を持つ第2のp型不純物濃度分布とを重ね合わせた不純物濃度分布を有する。第1のp型不純物濃度分布のpn接合部での濃度は第2のp型不純物濃度分布のpn接合部での濃度よりも高い。

(もっと読む)

半導体装置およびその製造方法

【課題】 STIによりフィールド絶縁膜を形成した半導体基板に、比較的ゲート酸化膜が厚くゲート長が長い高耐圧駆動MOSトランジスタを形成する時、STIに起因して熱応力に変化が生じて、半導体基板に欠陥が生じることを防止する。

【解決手段】 高耐圧駆動MOSトランジスタのゲート酸化膜102は、パイロ酸化により酸化成長させたSi酸化膜と、SiH4ガスの熱分解による減圧気相成長により成長させたSi酸化膜で構成される2層膜を、N2OもしくはNOガス中での急速加熱により酸化すると共に、微量に窒素を含むSi酸化膜を順次成長させたSi酸化膜系の絶縁膜で構成する。

(もっと読む)

101 - 120 / 151

[ Back to top ]