Fターム[5F048BC20]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 複数MOSの相互のS・D領域が異なるもの (1,340) | 濃度が異なるもの (151)

Fターム[5F048BC20]に分類される特許

21 - 40 / 151

半導体装置及びその製造方法

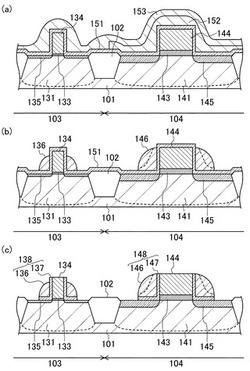

【課題】素子分離領域のエッチングを生じさせることなく、基板上にサイドウォール幅が異なる複数のトランジスタを精度良く形成できるようにする。

【解決手段】

半導体装置の製造方法において、まず第1のゲート電極134及び第2のゲート電極144を覆うように、第1の絶縁膜151及び第2の絶縁膜152を順次形成する。この後、第2の絶縁膜152における第1の領域103の上に形成された部分を除去する。この後、基板101の上に第3の絶縁膜153を形成する。この後、第2の絶縁膜152及び第3の絶縁膜153を選択的に除去することにより、第1のゲート電極134の側面上に第3の絶縁膜153からなる第1の外側サイドウォール136を形成し、第2のゲート電極144の側面上に第2の絶縁膜152及び第3の絶縁膜153からなる第2の外側サイドウォール146を形成する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】集積回路のコア部のロジックトランジスタ(MOSFET、MISFET)は、世代が進むごとに動作電圧をスケーリングすることで微細化が可能である。しかし、高耐圧部のトランジスタ(MOSFET、MISFET)は比較的高い電源電圧で動作するために縮小化が困難であり、同様に電源セル内の静電気放電(ESD)保護回路は、静電気(外来サージ)から半導体集積回路内の素子を保護するために耐圧が高いことが必須であり、電荷を逃がすために大面積である必要がある。従って、集積回路の微細化のためには、微細化が可能なトランジスタ構造が必須である。

【解決手段】本願発明は、ソース側にのみハロー領域を有するソースドレイン非対称構造の一対のMISFETから構成されたCMISインバータをESD保護回路部に有する半導体集積回路装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域とコンタクトプラグの接続部分の電気抵抗が低減され、かつ短チャネル効果の発生が抑えられたトランジスタを有する、n型およびp型トランジスタを含む半導体装置、およびその半導体装置の製造方法を提供すること。

【解決手段】不純物高濃度領域を有する半導体装置を提供する。前記不純物高濃度領域は、第1のソース・ドレイン領域内の前記第1のソース・ドレイン領域と前記第1のコンタクトプラグとの界面近傍に形成される。前記不純物高濃度領域の前記第1のコンタクトプラグの底面の長手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅の少なくとも一方は、前記第1のコンタクトプラグの前記底面の短手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物の偏析に起因する、ドレイン領域と空乏層との間のリーク電流の発生を抑制することが可能な半導体素子を含む半導体装置を提供する。

【解決手段】本半導体装置は、主表面を有する半導体基板SUBと、主表面上に形成された、論理回路を構成するコアトランジスタと、入出力回路を構成するI/Oトランジスタとを備える。主表面からI/On型トランジスタのn型不純物領域NRの最下部までの距離は、主表面からコアn型トランジスタのn型不純物領域NRの最下部までの距離より長い。主表面からI/Op型トランジスタのp型不純物領域PRの最下部までの距離は、主表面からコアp型トランジスタのp型不純物領域の最下部までの距離より長い。主表面からI/On型トランジスタのn型不純物領域の最下部までの距離は、主表面からI/Op型トランジスタのp型不純物領域の最下部までの距離より長い。

(もっと読む)

半導体装置の製造方法

【課題】1つのチップ内に、高駆動性が求められるpMISFET及び高信頼性が求められるpMISFETの両方を形成してCMOSトランジスタの品質向上をはかる。

【解決手段】Siチャネルを有する第1のpMISFET領域121、Siチャネルを有する第2のpMISFET領域122、及びSiチャネルを有するnMISFET領域123を備えた半導体装置であって、第1のpMISFET領域121に、Siチャネルを挟んで該Siチャネルに第1の圧縮歪みを与える第1のSiGe層321が埋め込み形成され、第2のpMISFET領域122に、Siチャネルを挟んで該Siチャネルに第1の圧縮歪みとは大きさの異なる第2の圧縮歪みを与える第2のSiGe層322が埋め込み形成されている。

(もっと読む)

半導体装置、およびその製造方法

【課題】従来に比して高いESD耐量性能を有するESD保護回路を備えた半導体装置、およびその製造方法を提供する。

【解決手段】内部回路に用いられる第1の半導体素子と、静電気による内部回路の破壊を抑制するESD保護回路として用いられる第2の半導体素子とを備える半導体装置の製造方法であって、基板に第1の半導体素子および第2の半導体素子各々についての端子領域層を形成する端子領域層形成ステップと、基板上の前記第2の半導体素子の端子領域層を除く領域について結晶欠陥を形成させる処理を施す欠陥形成ステップと、金属膜を第1の半導体素子および第2の半導体素子各々の端子領域層表面に形成する金属膜形成ステップと、金属膜と、第1の半導体素子および第2の半導体素子各々の端子領域層とをシリサイド化するシリサイド化ステップとを含む、半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において工程数の削減を図ること。

【解決手段】領域HVp、LVn、LLnに第1〜第3のゲート電極36a〜36cを形成する工程と、領域LVnを覆い、かつ、領域HVpと領域LLnを露出するマスクパターン40を形成する工程と、マスクパターン40をマスクにしたイオン注入でp型ソースドレインエクステンション41とp型ポケット領域42を形成する工程と、マスクパターン40をマスクにしたイオン注入でn型ソースドレインエクステンション45を形成する工程と、領域HVpと領域LLnを覆い、かつ、第2の領域LVnを露出するマスクパターン52を形成する工程と、マスクパターン52をマスクにしてインジウムをシリコン基板1にイオン注入し、p型ポケット領域54を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】非対称構造のソースおよびドレイン領域を有するMOSトランジスタを容易に形成する。これにより、高性能の半導体装置を容易に製造する。

【解決手段】第1のマスク層の互いに対向する両側面上に、2つの第2のマスク層を形成する。導電層上の、第1及び第2のマスク層が形成されていない部分の上に、第3のマスク層を形成する。第2及び第3のマスク層をマスクに用いて、導電層に対して異方性エッチングを行った後、不純物を注入することによって、1つの第1不純物拡散層を形成する。第2のマスク層をマスクに用いて異方性エッチングを行い第2のマスク層の下に、2つのゲート電極を形成する。第1不純物拡散層と共にゲート電極を挟む半導体基板の2つの領域に不純物を注入することによって、2つの第2不純物拡散層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】フィールドストップ領域のキャリア濃度が低減することを防止することができる半導体装置の製造方法を提供すること。

【解決手段】ドリフト領域1となる半導体基板のおもて面の表面に、半導体装置100のおもて面素子構造を形成する。ついで、ドリフト領域1の裏面を研削する。ついで、ドリフト領域1の裏面の一部に、P(リン)をイオン注入する(第1注入工程)。ついで、炉アニールを行い、第1注入工程においてドリフト領域1の裏面に注入したPを活性化する。これにより、ダイオード120のn+型領域10が形成される。ついで、ドリフト領域1の裏面の全体に、Se(セレン)をイオン注入する(第2注入工程)。第2注入工程は、第1注入工程が行われた後に行う。ついで、炉アニールを行い、第2注入工程においてドリフト領域1の裏面に注入したSeを活性化する。これにより、フィールドストップ領域11が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】動作電圧やしきい値電圧が相異なり、高誘電率ゲート絶縁膜/メタルゲート電極構造を有するP型MISFETを共通の基板上に混載可能にする。

【解決手段】半導体装置は、半導体基板100と、半導体基板100のうち第1のTr領域内に位置する領域に形成された第1の活性領域103aと、半導体基板100のうち第2のTr領域内に位置する領域に形成された第2の活性領域103bと、第1の活性領域103a上に形成された第1のP型MISFET150aと、第2の活性領域103b上に形成された第2のP型MISFET150bとを備えている。第1のP型MISFET150aは、ゲルマニウムを含有する半導体で構成された第1の半導体層104と、シリコンで構成された第2の半導体層105とを備えている。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】ドレイン耐圧を向上させる半導体装置及びその製造方法を提供すること。

【解決手段】基板100表面内に第1、第2拡散層206を形成する工程と、前記基板上に第1トランジスタを形成する工程と、前記ゲート電極の第1側壁及び第2側壁にそれぞれ第1、第2絶縁膜202を形成することにより、前記第1、第2拡散層の表面の一部の領域を被覆する工程と、この第2拡散層上に第3絶縁膜203を形成する工程と、前記第1〜第3絶縁膜、ゲート電極201、及び前記基板表面をそれぞれ第4絶縁膜204で被覆する工程と、前記ゲート電極の表面、及び第3絶縁膜に対して前記第2絶縁膜と前記第3絶縁膜との間の第1領域と相対する第2領域における前記第2拡散層の表面を露出しつつ、前記第1領域における前記第2拡散層の表面が露出しないよう前記第4絶縁膜を除去する工程とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便な製造方法によって製造された良好なTFT特性を有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、絶縁基板11と、絶縁基板11に支持されたチャネル領域33A、ソース領域34Aおよびドレイン領域35Aを含む半導体層30Aと、チャネル領域33Aの導電性を制御するゲート電極51とを有する。半導体層30Aは、チャネル領域33Aとソース領域34Aとの間に形成された第1低濃度領域31A、および、チャネル領域33Aとドレイン領域35Aとの間に形成された第2低濃度領域32Aとを有する。チャネル領域33A、第1および第2低濃度領域31Aおよび32Aは、ソースおよびドレイン領域34Aおよび35Aの不純物濃度より低い第1不純物濃度を有する。ゲート電極51は、第1および第2低濃度領域31Aおよび32Aの全部を覆うように形成されている。

(もっと読む)

MISFET及びその製造方法

【課題】 LDD領域の長さを精度良く調整可能で、高周波動作に適用できる非対称な横方向二重拡散型MISFETを提供する。

【解決手段】 第1導電型のウェル1の上方にゲート絶縁膜3を介してゲート電極5を形成する工程、ウェル1に第2導電型の不純物イオン注入によりドレイン領域7を形成する工程、ウェル1の上方にゲート電極5が形成されるゲート電極領域とドレイン領域7を少なくとも覆い、ゲート電極領域とドレイン領域の間が開口したマスクパターン層を形成する工程、マスクパターン層をマスクとして自己整合的に、マスクパターン層で覆われていない領域に第2導電型の不純物イオン注入によりドレイン領域より低濃度のLDD拡散領域6を形成する工程、及び、ウェル1のゲート電極5を挟んでドレイン領域7の反対側の領域に第2導電型の不純物イオン注入によりLDD拡散領域より高濃度のソース領域を形成する工程を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】注入マスクの低減が図られる半導体装置の製造方法と、そのような半導体装置を提供する。

【解決手段】レジストマスク31と他のレジストマスクを注入マスクとして、NMOS領域RNにボロンを注入することにより、アクセストランジスタおよびドライブトランジスタのハロ領域となるp型不純物領域が形成される。さらに他のレジストマスクを注入マスクとして、PMOS領域RPにリンまたは砒素を注入することにより、ロードトランジスタのハロ領域となるn型不純物領域が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタにおけるシリコン混晶層からなるソースドレイン領域を、不純物の拡散による不具合を防止しながらチャネル領域に近づけることができるようにする。

【解決手段】半導体装置は、半導体基板10からなるn型の活性領域の上に、ゲート絶縁膜12を介在させて形成されたゲート電極13と、活性領域におけるゲート電極13の両側方の領域に形成されたp型ソースドレイン領域20と、活性領域における各p型ソースドレイン領域20の側面からそれぞれゲート電極13の下側に向かって形成されたn型ポケット領域18とを有している。p型ソースドレイン領域20は、シリコンとIV族元素との混晶層からなり、混晶層は、ゲート長方向におけるゲート電極側の側面がゲート電極側に突き出す凸部20aを有している。凸部20aの先端は、ポケット領域18によって覆われている。

(もっと読む)

半導体装置

【課題】ロジック系CMOSトランジスタおよびパワー系DMOSトランジスタのそれぞれが最適な構造を有する半導体装置を提供する。

【解決手段】第1半導体領域2の表面側に設けられた第1ソース領域3、ドレイン領域4と、第1ゲート13と、第1ゲートの両側面に形成された第1サイドウォール15と、第1LDD領域17とを有する第1のMOSトランジスタと、第2半導体領域22の表面側に設けられた第2ソース領域23、ドレイン領域24と、第2ゲート33と、第2ゲートの第2ドレイン側の側面に形成され、第1サイドウォールよりも広い第2サイドウォール41と、第2サイドウォール直下に形成されたドリフト領域43と、第2ゲートの第2ソース側の側面に形成され、第1サイドウォールよりも狭い第3サイドウォール35と、第3サイドウォール直下に形成された第2LDD領域37とを有する第2のMOSトランジスタを備えた半導体装置を提供する。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】製造効率を向上すると共に、内部回路の保護を的確に行うことを容易に可能にする。

【解決手段】ESD保護素子101の高濃度不純物領域121SH,120DH,122SHを、ゲート電極111G,112Gの下方に形成しない。高濃度不純物領域121SH,120DH,122SHを、半導体基板100の面(xy面)にて、少なくとも低濃度不純物領域121SL,121DL,122DL,122SLを介してゲート電極111G,112Gの側部に位置するように形成する。また、高濃度不純物領域121SH,120DH,122SHを、低濃度不純物領域121SL,121DL,122DL,122SLおよび不純物領域121SM,120DM,122SMよりも深い位置まで形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造コストが低減し、電界効果トランジスタの短チャネル効果が抑制された半導体装置を提供する。

【解決手段】第1導電型のソース領域と、第1導電型のドレイン領域と、が表面に選択的に形成された第2導電型のウェル領域と、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ソース領域に接続された第1の主電極と、前記ドレイン領域に接続された第2の主電極と、を備え、前記ソース領域の最も曲率が高い部分または前記ドレイン領域の最も曲率が高い部分と同じ深さの前記ウェル領域の位置を基準した場合、前記ウェル領域の深さ方向の前記第2導電型の不純物濃度分布のプロファイルは、前記基準からプラスマイナス0.15ミクロンの範囲に不純物濃度分布のピークを有することを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧で、特性の優れた半導体装置を提供する。

【解決手段】素子分離領域STIと、ウェルPWと、活性領域を横断するゲート電極Gと、ゲート電極の一方の側からゲート電極下方に入り込んで形成された低濃度ドレイン領域LDDと、ゲート電極の他方の側からゲート電極下方に入り込み、低濃度ドレイン領域とオーバーラップし、低濃度ドレイン領域より浅い、チャネル領域CHと、ゲート電極の他方の側に形成されたソース領域Snと、ゲート領域の一方の側に、ゲート電極から離間したドレイン領域Dnと、を有し、ゲート電極と高濃度ドレイン領域Dnとの間の中間領域の実効不純物濃度は、オーバーラップ領域の不純物濃度より高い。

(もっと読む)

21 - 40 / 151

[ Back to top ]