Fターム[5F048BF02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 材料 (4,535) | Al (631)

Fターム[5F048BF02]に分類される特許

101 - 120 / 631

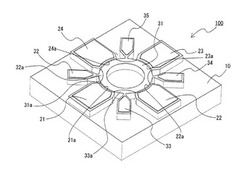

MEMS及びMEMSの製造方法

【課題】回路構成の設計自由度の高いMEMS及びMEMSの製造方法を提供する。

【解決手段】基板10と、基板10の一方の面側に設けられる第1半導体部21と、基板10の一方の面側に設けられる振動子31と、を備えるMEMSにおいて、第1半導体部21の側面側に設けられ、かつ基板表面に対して略垂直な第1面21aと、振動子31の側面側に設けられ、かつ基板表面に平行な方向において第1面21aと対向する第2面31aが設けられると共に、第2面31a側の表層部分は第1面21a側をゲート電極として電圧が印加された際にチャネルとなることで、第1半導体部21における第1面21aを含む部分と振動子31における第2面31aを含む部分とで電界効果トランジスタが構成されることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧の異なるトランジスタが同一半導体基板上に混載されている場合においても、それらのトランジスタの性能が向上するようにストレスライナ膜を構成することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に混載された低耐圧トランジスタおよび高耐圧トランジスタ上に形成するストレスライナ膜11、12は、互いに膜質を異ならせることができる。ここで、ストレスライナ膜11は、低耐圧トランジスタの性能が効果的に改善され、高耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。また、ストレスライナ膜11は、高耐圧トランジスタの性能が効果的に改善され、低耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。

(もっと読む)

表示装置

【課題】高速動作が可能な絶縁ゲート型FETによる駆動回路で表示装置を形成し、さらに、単位画素当たりの画素電極の面積を小さくしても十分な保持容量が得られるアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】単結晶半導体を活性層とした絶縁ゲート型電界効果トランジスタによるアクティブマトリクス回路を備えた半導体装置において、前記絶縁ゲート型電界効果トランジスタ上に有機樹脂絶縁層を形成し、該有機樹脂絶縁層上に形成された遮光層と、該遮光層に密接して形成された誘電体層と、前記絶縁ゲート型電界効果トランジスタに接続された光反射性電極とから保持容量を形成する。

(もっと読む)

グラフェン・ベースの三次元集積回路デバイス

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が小さい半導体装置である。

(もっと読む)

半導体装置製造方法及び積層半導体装置

【課題】複数の基板を貼り合わせる積層半導体装置を効率よく製造できる方法を提供する。

【解決手段】複数の基板を貼り合わせて積層半導体装置を製造する半導体装置製造方法であって、回路が形成された複数の基板のうちの一の基板に凹部を形成する凹部形成ステップと、一の基板を複数の基板のうちの他の基板に重ね合わせる重ね合わせステップと、重ね合わせステップの後に、一の基板の凹部に導電性材料を導入することにより、一の基板の回路と他の基板の回路との間の電気的な導通路を形成する導通形成ステップとを備える半導体装置製造方法が提供される。

(もっと読む)

液晶パネル用基板、液晶パネル、電子機器及び投射型表示装置

【課題】半導体を基板とする液晶パネルは、ウェル領域があるため、漏れ光がトランジスタ部分のみでなくそこから離れた半導体基板を通過しただけで光リーク電流が流れることがある。この光リーク電流が、ガラス基板上にスイッチング素子としてのTFTを配置した液晶パネルに比べて多くなるという欠点がある。

【解決手段】反射電極となる画素電極(14)と、画素電極への電圧印加を制御するスイッチング素子とを有する画素単位が基板上にマトリックス状に配置されてなる液晶パネル用基板において、両素電極とスイッチング素子の端子電極を構成する導電層(6a)との間に、両者を接続するためのコンタクトホールを形成し、このコンタクトホールの形成箇所を囲む開口を有し、隣接する複数の画素電極の間の領域には開口を有さない遮光層を、画素電極と導電層との間に設けることにより、画素電極どうしの隙間から漏込む光による弊害を防ぐ。

(もっと読む)

薄膜集積回路の作製方法

【課題】シリコンウェハからなるICチップは厚いため商品容器自体に搭載する場合、表

面に凹凸が生じ、デザイン性が低下してしまった。そこで非常に膜厚の薄い薄膜集積回路

、及び薄膜集積回路を有するICチップ等を提供する。

【解決手段】薄膜集積回路を有するICチップは、従来のシリコンウェハにより形成され

る集積回路と異なり、半導体膜を能動領域(例えば薄膜トランジスタであればチャネル形

成領域)として備えることを特徴とする。このようなICチップは非常に薄いため、カー

ドや容器等の商品へ搭載してもデザイン性を損ねることがない。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性および集積性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板1)と、シリコン基板1に設けられた第1のトレンチ3と、第1のトレンチ3に埋め込まれた受動素子層10と、第1のトレンチ3と受動素子層10との間に設けられた第1の絶縁膜(シリコン窒化膜4)と、を備え、上面視において、第1のトレンチ3形成の周縁部分と第1の絶縁膜(シリコン窒化膜4)の周縁部分とが略一致している。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

半導体装置

【課題】待機電力の低減を実現する半導体装置の提供を、目的の一とする。

【解決手段】酸化物半導体を活性層として有するトランジスタをスイッチング素子として用い、該スイッチング素子で、集積回路を構成する回路への電源電圧の供給を制御する。具体的には、回路が動作状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を行い、回路が停止状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を停止する。また、電源電圧が供給される回路は、半導体を用いて形成されるトランジスタ、ダイオード、容量素子、抵抗素子、インダクタンスなどの、集積回路を構成する最小単位の半導体素子を、単数または複数有する。そして、上記半導体素子が有する半導体は、結晶性を有するシリコン(結晶性シリコン)、具体的には、微結晶シリコン、多結晶シリコン、単結晶シリコンを含む。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層を含むトランジスタと、酸化物半導体以外の半導体材料を用いて構成された論理回路と、を有し、前記トランジスタのソース電極またはドレイン電極の一方と、前記論理回路の少なくとも一の入力とは電気的に接続され、前記トランジスタを介して、前記論理回路に少なくとも一の入力信号が供給される半導体装置である。ここで、トランジスタのオフ電流は1×10−13A以下であるのが望ましい。

(もっと読む)

半導体装置

【課題】半導体装置を構成するトランジスタを製造する際にトランジスタ能力のばらつきが発生しても、期待通りの性能を発揮することができる半導体装置を提供する。

【解決手段】半導体基板100上に、トランジスタ104A及び104Bと、電極パッド106とが形成されている。電極パッド106の上側領域を除く半導体基板100を覆うように、保護膜107が形成されている。トランジスタ104Aの上側領域を除く保護膜107を覆うように、凸方向に応力160を生じる保護膜108が形成されている。保護膜108によって、トランジスタ104Bの能力を基準として、トランジスタ104Aの能力が相対的に高く又は低く変動している。

(もっと読む)

半導体装置の製造方法

【課題】SOIデバイスにおいて生じやすい基板浮遊問題やホットキャリアの問題を充分に抑制することが可能で、広く分布する部分分離絶縁膜であっても周囲の構造に対し結晶欠陥を生じさせにくい半導体装置の製造方法を提供する。

【解決手段】各MOSトランジスタTR1の間に設けられた部分分離絶縁膜5b内におよそ一定の間隔を置いて、素子としての機能を有しないダミー領域DM1を形成する。これにより、部分分離絶縁膜5b下のシリコン層3bよりも抵抗値の低いダミー領域DM1の占める割合が増加して、基板浮遊問題やホットキャリアの問題の抑制が行えるようになる。

(もっと読む)

半導体装置及びその作製方法

【課題】電気特性が良好で信頼性の高いトランジスタをスイッチング素子として用い、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】加熱処理により脱水化または脱水素化され、表面にナノ結晶からなる微結晶群が形成された酸化物半導体層を形成し、酸化物半導体層上に非晶質で透光性のある酸化物導電層を用いてソース電極層及びドレイン電極層を形成し、酸化物半導体層上の酸化物導電層を選択的にエッチングすることで透光性のあるボトムゲート型のトランジスタを形成し、同一基板上に駆動回路部と画素部を設けた信頼性及び表示品質の高い半導体装置を作製する。

(もっと読む)

半導体装置およびその作製方法

【課題】LSIやCPUやメモリに用いるトランジスタのリーク電流及び寄生容量を低減することを課題の一とする。

【解決手段】酸化物半導体中で電子供与体(ドナー)となる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもエネルギーギャップが大きい酸化物半導体でチャネル領域が形成される薄膜トランジスタを用い、LSIやCPUやメモリなどの半導体集積回路を作製する。水素濃度が十分に低減されて高純度化された酸化物半導体層を用いる薄膜トランジスタは、リーク電流による消費電力の少ない半導体装置を実現できる。

(もっと読む)

電子回路用の保護素子

集積半導体構成体を有する保護素子と、この保護素子の製造方法が記載される。この保護素子は、少なくも1つのショットキーダイオード(S)と少なくとも1つのツェナーダイオード(Z)とを有し、電流供給部と電子回路との間に接続される。ここでは前記ショットキーダイオード(S)のアノードが電流供給部と接続されており、前記ショットキーダイオード(S)のカソードが電子回路および前記ツェナーダイオードのカソードと接続されており、該ツェナーダイオードのアノードがアースと接続されている。ショットキーダイオード(S)は、トレンチ・MOS・バリア・ジャンクション・ダイオードまたはトレンチ・MOS・バリア・ショットキーダイオード(TMBSダイオード)またはトレンチ・ジャンクション・バリア・ショットキーダイオード(TJBSダイオード)であり、少なくとも1つのトレンチ・MOS・バリア・ショットキーダイオードと、ツェナーダイオード(Z)のアノードとして用いられるpドープ基板とを有する集積半導体構成体を含む。  (もっと読む)

(もっと読む)

電界効果型半導体装置

【課題】各種電子機器の中枢であるMOSFETの製造において,微細化技術に頼らない高性能化および超低消費電力化技術を提供する。

【解決手段】MOSFETに印加するゲート電圧に連動してゲート絶縁膜中の電荷分布を変化させ,半導体の表面電位を該ゲート電圧の極性とは反対の極性方向に変化させる機能を利用することによりしきい値電圧を低減し,低電圧動作および低消費電力化を可能にする。

(もっと読む)

半導体デバイスおよび製造方法

【課題】Nチャネル型電界効果トランジスタとPチャネル型電界効果トランジスタとが同一基板上に形成された半導体デバイスにおいて、安定した電気的特性を得る

【解決手段】カーボンナノチューブCMOS1は、N型カーボンナノチューブFET2(以下、N型CN−FET2という)とP型カーボンナノチューブFET3(以下、P型CN−FET3という)とから構成される。N型CN−FET2は、カーボンナノチューブ14と、カーボンナノチューブ14上に形成されたゲート絶縁膜21を備え、ゲート絶縁膜21は酸化ハフニウムである。P型CN−FET3は、カーボンナノチューブ14と、カーボンナノチューブ14上に形成されたゲート絶縁膜31を備え、ゲート絶縁膜31は酸化アルミニウムである。これにより、N型CN−FET2のチャネル層近傍において、P型CN−FET3のチャネル層近傍よりも多くの正の固定電荷が導入される。

(もっと読む)

101 - 120 / 631

[ Back to top ]