Fターム[5F048BF02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 材料 (4,535) | Al (631)

Fターム[5F048BF02]に分類される特許

161 - 180 / 631

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

液晶表示装置

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

半導体表示装置の作製方法

【課題】高精彩・高解像度・高画質・低消費電力の小型半導体表示装置を提供すること。

【解決手段】本発明の半導体表示装置は、画素マトリクス回路、データ線駆動回路、および走査線駆動回路を有しており、これらの構成要素が多結晶TFTによって同一基板上に形成される。また、その製造方法における、触媒元素を用いた結晶性の助長化プロセス、および触媒元素のゲッタリングプロセスによって、小型にもかかわらず、高精細・高解像度・高画質の半導体表示装置が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 インバータ等のハーフブリッジ回路に用いられるMOSFETでは、ハーフブリッジ回路の構成上、MOSFETのオン時に突入電流が発生し、これによる輻射ノイズが発生する問題があった。

【解決手段】 MOSFETのソース領域の濃度を低減し、ソース領域と電極層(ソース電極層)間にショットキー接合を形成する。これにより、オン時にMOSFETを逆流する電流を防止でき、突入電流の発生を回避できる。従って、ハーフブリッジ回路にMOSFETを用いた場合、輻射ノイズを防止できる。更に、MOSFET内の寄生ダイオードをFRD化させることにより、当該MOSFETをモータ等の用途に用いる場合に、外付けのFRDが不要となり、素子数を低減できる。

(もっと読む)

半導体素子及び半導体装置

【課題】高い電流駆動力を有するn型半導体素子を提供する。

【解決手段】第1の主面を有し、III族の不純物を含み、1.2<N<10を満たすNを用いて(11N)面と表される、ないしはそれと結晶学的に等価な第1の面方位のみを前記第1の主面に有する、シリコンとゲルマニウムとの混晶層と、前記第1の主面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記混晶層の[110]方向ないしそれと結晶学的に等価な方向に、前記ゲート電極を挟む様に形成され、V族の不純物を含む半導体よりなるソース・ドレイン領域と、を有し、前記混晶層は面内方向に圧縮歪みが印加されていることを特徴とする。

(もっと読む)

高誘電率ゲート絶縁膜を備えた電界効果トランジスタを有する半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜を用いるFET及びその製造方法において、閾値電圧の制御性を向上する。

【解決手段】基板101上に高誘電率ゲート絶縁膜110、その上にゲート電極111aを形成する。少なくともゲート電極111aをマスクとして基板101にN型不純物を導入し、N型イクステンション領域113を形成する。少なくともゲート電極111aをマスクとして、基板101におけるN型イクステンション領域113の下にP型不純物を導入し、P型ポケット領域114を形成する。N型イクステンション領域113に対するN型不純物のうちのAsの導入量を、当該Asと高誘電率ゲート絶縁膜110中の元素との結合によって生じる異常な短チャネル効果が実質的に抑制される臨界点以下である範囲に設定する。臨界点は、高誘電率ゲート絶縁膜110の膜厚に基づいて算出される。

(もっと読む)

縦型論理素子

【課題】狭い面積で高速応答性の縦型半導体装置を提供する。

【解決手段】基板上に形成された第1の電極と、絶縁膜と、絶縁膜を介し第1の電極の側面の一方に形成された第1の導電型の第1の半導体層と、絶縁膜を介し第1の電極の側面の他方に形成された第2の導電型の第2の半導体層と、一部領域における第1の半導体層上に形成された第2の電極と、他の一部領域における第2の半導体層上に形成された第3の電極と、第1の電極の上層の第1の半導体層及び第2の半導体層上に形成された第4の電極とを有し、第2の電極と前記第4の電極間における第1の半導体層に第1のチャネル領域が形成され、第3の電極と前記第4の電極間における第2の半導体層に第2のチャネル領域が形成されるものであることを特徴とする縦型半導体装置を提供することにより上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】プラグとシリサイド領域との間の電気抵抗を小さくすることができる半導体装置およびその製造方法を提供する。

【解決手段】シリサイド領域SCs、SCgを各々が有する少なくとも1つの半導体素子NT、PTが半導体基板SB上に形成される。シリサイド領域上に層間絶縁膜が形成される。シリサイド領域SCs、SCgからなる底面を有する内面が設けられたスルーホールTHが層間絶縁膜ILD1に形成される。内面を被覆するTi(チタン)膜が化学気相成長法によって形成される。内面を被覆するバリアメタル膜を形成するためにTi膜TFの少なくとも表面部が窒化される。バリアメタル膜を介してスルーホールTHを埋めるプラグが形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリセルを有する半導体装置において、駆動力の低下を抑えて、信頼度を向上させることのできる技術を提供する。

【解決手段】メモリセルMC1をp型の導電性を示す導電膜からなる選択ゲート電極CGを有する選択用pMIS(Qpc)とp型の導電性を示す導電膜からなるメモリゲート電極MGを有するメモリ用pMIS(Qpm)とから構成し、書込み時には半導体基板1側からホットエレクトロンを電荷蓄積層CSLへ注入し、消去時にはメモリゲート電極MGからホットホールを電荷蓄積層CSLへ注入する。

(もっと読む)

接合型FET、半導体装置およびその製造方法

【課題】JFETの電気的特性を改善すること。

【解決手段】N型基板201上のPウェル202内部にN型チャネル領域203がある。N型チャネル領域203上にP型ゲート領域103がある。ゲート領域103の中にN型ソース領域107及びドレイン領域106が互いに平行に配置され、それらはN型チャネル203に接続されている。ゲート領域103を配線に接続するためにP型ゲートコンタクト領域104がソース領域107及びドレイン領域106から離れた位置に設けられている。N型チャネル203とPウェル202との境界の上に平坦な分離用のシリコン熱酸化膜204があり、その上に分離用の多結晶シリコン101がある。多結晶シリコン101より外側のPウェル202の上に配線を接続するためにPウェルコンタクト領域102がある。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜内に金属原子を拡散させるための膜の除去を容易にする。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上に金属膜を形成する工程と、窒素ガス及び不活性ガスの少なくとも一方の雰囲気中で半導体基板、下地膜、ゲート絶縁膜及び金属膜を熱処理する工程と、ゲート絶縁膜上に残存する金属膜を除去する工程と、ゲート絶縁膜上に、ゲート電極膜を形成する工程とを備える。

(もっと読む)

論理回路及び半導体装置

【課題】電気特性の制御された酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体装置及びその作製方法

【課題】大型の半導体装置で、高速に動作する半導体装置を提供することを目的する。

【解決手段】単結晶の半導体層を有するトップゲート型のトランジスタと、アモルファス

シリコン(またはマイクロクリスタルシリコン)の半導体層を有するボトムゲート型のト

ランジスタとを同一基板に形成する。そして、各々のトランジスタが有するゲート電極を

同じレイヤーで形成し、ソース及びドレイン電極も同じレイヤーで形成する。このように

して、製造工程を削減する。つまり、ボトムゲート型のトランジスタの製造工程に、少し

だけ工程を追加するだけで、2つのタイプのトランジスタを製造することが出来る。

(もっと読む)

BiCDMOS構造及びその製造方法

【課題】DMOS電力回路、CMOSデジタル論理回路、及びコンプリメンタリバイポーラアナログ回路の全てを単一の集積化された回路チップ上に実現するBiCDMOS構造及びその製造方法を提供する。

【解決手段】基層10内に下向きに延出し、且つ基層の上に配置されたエピタキシャル層40内に上向きに延出し、かつエピタキシャル層の上側主面の下に配置された埋め込み絶縁領域21Bと、エピタキシャル層内のみに配置され、かつ埋め込み絶縁領域の上側主面から上向きに延出した埋め込みウェル領域44Bと、エピタキシャル層内に配置され、かつエピタキシャル層の上側主面からエピタキシャル層内に下向きに延出し、かつ埋め込みウェル領域の上側主面に接触する下側主面を備えたウェル領域51Bとを有し、バイポーラトランジスタがウェル領域内に形成され、MOSトランジスタがウェル領域外のエピタキシャル層の上側主面に形成される。

(もっと読む)

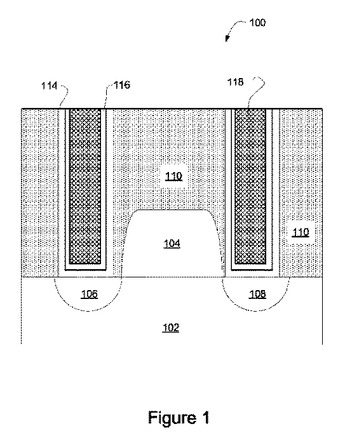

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体構造、半導体構造の形成方法、半導体装置の動作方法(高周波の高調波を減少するためのSOIRFスイッチ)

【課題】SOI基板における容量結合を減少した集積回路を提供する。

【解決手段】底部半導体層と同じ導電型のドーパントを含む第1のドープされた半導体領域18及び反対導電型のドーパントを含む第2のドープされた半導体領域28がSOI基板の埋め込み絶縁層20の直下に形成される。第1のドープされた半導体領域18及び第2のドープされた半導体領域28は、共にグランド電位に接続されるか、又は底部半導体層への少数キャリアの順方向バイアス注入に基づく過剰な電流を生じるには不十分は電圧、即ち、0.6V乃至0.8Vを越えない電位差を保って底部半導体層に対して順方向バイアスされる。上部半導体の半導体装置内の電気信号により誘起される電荷層内の電荷は第1及び第2のドープされた半導体領域に接続されている電気的コンタクトを介して引き出され、これにより半導体装置内の高調波信号を減少させる。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

冷却機構を含む接合型半導体構造体とその形成方法

【課題】 冷却機構を有する接合型半導体基板を形成するための構造体、設計構造体、及びその形成方法を提供すること。

【解決手段】 2つの半導体基板を備える接合型基板が提供される。各々の半導体基板は、半導体デバイスを含む。少なくとも1つの基板貫通ビアが2つの半導体基板の間に設けられ、それらの間に単一の経路を提供する。2つの半導体基板の底側は、冷却機構を含む少なくとも1つの接合材料層によって接合される。1つの実施形態において、冷却機構は冷却チャネルであり、その中を通って冷却流体が流動し、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。別の実施形態において、冷却機構は、2つの端部とそれらの間の連続した経路を備えた導電性冷却フィンである。冷却フィンはヒートシンクに接続され、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。

(もっと読む)

161 - 180 / 631

[ Back to top ]