Fターム[5F048BF18]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 基板(ウェル)コンタクト領域 (940)

Fターム[5F048BF18]に分類される特許

921 - 940 / 940

半導体装置

【課題】 低しきい値電圧のMOSFETを含むCMOS回路の電源投入時あるいは電源遮断時におこすラッチアップを阻止し、通常動作中のサブスレッショルド電流を低減する。

【解決手段】 通常動作時には実質的に十分カットオフできないMOSFETを含むCMOS回路の電源と外部電源との間に、電源電圧制御用のMOSFET(Q)を接続し、電源投入時には低しきい値MOSFETを含むCMOS回路にウエル電圧を投入した後に、上記電源電圧制御用のMOSFETを導通させる。

(もっと読む)

半導体装置

【課題】デュアルゲート構造を有するMIS型トランジスタにおいて、デュアルゲートにおけるシリサイド部分の断線に起因する遅延の劣化を防止して、動作不良を防止できるようにする。

【解決手段】 半導体装置は、上部がシリサイド化されたゲート電極22を有するP型MOSトランジスタ100及びN型MOSトランジスタ200を備え、ゲート電極22におけるP型MOSトランジスタ100部分は、P型不純物が導入されたポリシリコンを含み、そのN型MOSトランジスタ200部分は、N型不純物が導入されたポリシリコンを含む。P型MOSトランジスタ100及びN型MOSトランジスタ200の互いのドレインは、シリサイド化されたポリシリコンを含む共有配線23により接続されている。共有配線23の線幅は、ゲート電極22の線幅よりも大きくなるように設定されている。

(もっと読む)

pinダイオードを備えた集積回路構造およびその製造方法

特に、pinフォトダイオード(14)と、バイポーラトランジスタ(58)の高ドープされた接続領域(62)とを含んだ集積回路構造(10)を開示する。高度な制御方法により、pinダイオード(14)の非常に深い中間領域(30)を、オートドーピングを用いずに形成できる。  (もっと読む)

(もっと読む)

半導体集積回路構造およびその製造方法

【課題】 半導体集積回路構造およびその製造方法を提供する。

【解決手段】 半導体集積回路構造は複数のダイオード、少なくとも一つの嵌入領域および電圧供給ノードを備える。複数のダイオードは基板中に設置され、直列に電性接続される。少なくとも一つの嵌入領域は、基板中に設置され、二つのダイオードの間に設置される。電圧供給ノードは、嵌入領域に電性接続される。また、好適にはこれらのダイオードはガードリングにより囲まれる。

(もっと読む)

半導体装置

【課題】同一なチップ内でNチャネルおよびPチャネルの両チャネルが高い耐圧特性を有する高耐圧MOSトランジスタを実現でき得るデバイス構造の製造方法を提供する。

【解決手段】本発明は、Nch型L−DMOS101 とPch型L−DMOS102と論理部103 から成る半導体装置であり、Nch型L−DMOS101 は、N型ドリフト領域12、Pウエル19、P型高濃度拡散層20、ソース拡散層21、ドレイン拡散層22、ソースコンタクト14、ドレインコンタクト16、ソース電極配線15、ドレイン電極17、ゲート電極18の各主要素から成り、SOI領域であるN型ドリフト領域12に形成されたこのNch型L−DMOS101のソース電極14と、領域11と、を電気的に導通して同電位になるように構成するデバイス構造である。

(もっと読む)

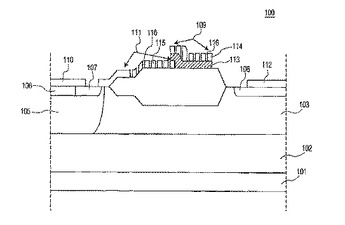

半導体装置

【課題】 寄生トランジスタのオン動作を防止し、回路消費電流を低減するブートストラップ方式の半導体装置を提供する。

【解決手段】 パワーデバイスの低圧側(112)の電力素子を駆動して高圧側駆動部(111)の電源を供給するブートストラップ回路は、少なくともブートストラップコンデンサに電源を供給する低圧半導体素子部(7)と高圧島ドリフト部(Rn,8)を備え、低圧半導体素子部と高圧島ドリフト部は接合分離され、pch−MOSトランジスタ(Tr7)のバックゲート(16)はダイオードが接続されていないオープン構成としている。

(もっと読む)

ショットキーデバイス

ショットキー・ダイオード特性及びMOSトランジスタ(18,92)を有する原理的なショットキー・ダイオード(16)又はデバイス(90)は直列に結合されて、順電流がわずかに劣化するだけで漏れ電流及びブレークダウン電圧の大幅な改善をもたらす。逆バイアスの場合、小さな逆バイアス電流は存在するが、ショットキー・ダイオード(16,90)にかかる電圧はMOSトランジスタ(18,92)により小さく保たれる。MOSトランジスタ(18,92)がブレークダウン状態になるまで、ほとんどすべての逆バイアス電圧がMOSトランジスタにかかる。しかし、ショットキー・ダイオード(16,90)が電流を制限するので、このトランジスタのブレークダウンは始めから破壊的なわけではない。逆バイアス電圧が増加し続けるにつれて、ショットキー・ダイオード(16,90)により多くの電圧がかかり始める。このことにより漏れ電流は増加されるが、トランジスタ(18,92)とショットキー・ダイオード(16,90)との間でブレークダウン電圧はいくらか追加される。  (もっと読む)

(もっと読む)

アバランシェを阻止できる大電流MOSデバイスおよび動作方法。

特に大電流を使用する場合、MOSトランジスタ(51)のドレイン(74)中に、衝撃イオン化によって、電子‐正孔の対が生成されて、それによって寄生バイポーラトランジスタ(38)が破壊的に導電性になる。正孔は、内在の抵抗を有するMOSトランジスタ(51)の本体領域(76)を通過してソース(80)に達し、ソース(80)はグランドのように比較的低電圧で保持される。正孔電流は本体領域(76)中に電圧を発生させてベース(42)として作用する。この増大したベース電圧は寄生バイポーラトランジスタ(38)を導電性にする。この可能性は、エミッタ(44)として作用するソース(80)と本体領域(76)との間のインピーダンスを介してチャネル電流を流すことによって、ソース(80)と本体領域(76)の間に電圧発生させることによって大幅に減少する。これによって、ベース電圧の増大に伴ってエミッタ電圧が増加し、それによって、寄生バイポーラトランジスタ(38)が導電性になるのを防止する。  (もっと読む)

(もっと読む)

高圧接合型電界効果トランジスタ

本発明は、第2の導電型基板(10)内の第1の導電型の第1のウエル(11)と、前記第1のウエル内のそれぞれ第1の導電型からなるソース(14)及びドレイン(15)と、第2の導電型からなる第2のウエル(12)内に配設されている第2の導電型のゲート(16)とを有している高圧接合型電界効果トランジスタに関しており、前記第2のウエルは逆行性のタイプからなり、さらにソース、ゲート、ドレインの素子がフィールド酸化膜領域(13a〜13d)によって相互に離間されていることを特徴としている。またゲート(16)からソース及びドレイン領域の方向にフィールドプレート(17a,17b)がフィールド酸化膜(13a,13b)の上方で延在している。  (もっと読む)

(もっと読む)

CMOSシリサイド金属ゲート集積化

本発明は、ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。本発明の集積化方式を用いて形成される各シリサイド金属ゲートは、シリサイド金属ゲートの寸法に関わりなく、同じシリサイド金属相および実質的に同じ高さを有する。本発明は、半導体構造物の表面全体にわたってポリSiゲート高さが実質的に同じであるシリサイド接点を有するCMOS構造物を形成するさまざまな方法も提供する。

(もっと読む)

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

ラッチアップに対する脆弱性について集積回路をテストする方法及び装置

集積回路設計のラッチアップに対する脆弱性をテストするためのテストモジュールであって、前記テストモジュールは並列接続された複数のテストブロック(30)を有し、各テストブロック(30)は、それぞれのテストブロック(30)にストレス電流又は電圧を印加するためのインジェクタブロック(12)と、それぞれのインジェクタブロック(12)から異なる距離に連続的に配置された複数のセンサブロック(13)とを有し、各センサブロック(13)はPNPNラッチアップテスト構造を有するテストモジュール。本発明は、従来のICストレス電流テスト、及び標準的なPNPNラッチアップテスト構造を利用するラッチアップ・パラメータ測定の、それぞれの利点を併せ持つ。  (もっと読む)

(もっと読む)

電圧発生回路と半導体集積回路装置

第1電流がエミッタに流れるようにされた第1トランジスタと、上記第1トランジスタよりも大きな電流密度となるような第2電流がエミッタに流れるようにされた第2トランジスタとのベース,エミッタ間の電圧差を第1抵抗に流して定電流を形成し、それと直列にして第2抵抗を回路の接地電位側に設け、上記第1トランジスタと第2トランジスタのコレクタと電源電圧との間に第3抵抗と第4抵抗とを設け、上記第1と第2トランジスタの両コレクタ電圧とCMOS構成の差動増幅回路に供給して、出力出力電圧を形成するとともに、かかる出力電圧を上記第1トランジスタと第2トランジスタのベースに共通に供給する。 (もっと読む)

電源システム抑止方法ならびにその装置および構造

電源制御装置システム(25)は、電源制御装置システム(25)のスタートアップ動作を制御するために2つの別個の電流を使用する。2つの電流は、電源制御装置システム(25)の動作を抑止するために接地に分流され、2つの電流のうちの1つは電力消散を最小限にするためにディセーブルにされる。2つの独立した制御電流は、2つの別個の制御信号(23、24)に応答して、マルチ出力電流高電圧装置(12)によって生成される。  (もっと読む)

(もっと読む)

大量にドープされたエピタキシャルSiGeを選択的に堆積させる方法

一実施形態においては、基板上にシリコン膜又はシリコンゲルマニウム膜を堆積させる方法であって、プロセスチャンバ内に基板を配置するステップと、基板表面を約600℃〜900℃の範囲の温度に、プロセスチャンバ内の圧力を約13Pa(0.1トール)〜約27kPa(200トール)の範囲に維持しつつ、加熱するステップと、を含む前記が提供される。堆積ガスは、プロセスチャンバに供給され、SiH4、任意のゲルマニウム源ガス、エッチング剤、キャリヤガス、任意に少なくとも1つのドーパントガスを含んでいる。シリコン膜又はシリコンゲルマニウム膜は、基板上に選択的且つエピタキシャル的に成長する。一実施形態は、シリコン含有膜とキャリヤガスとして不活性ガスを堆積させる方法を含んでいる。方法は、また、選択的シリコンゲルマニウムエピタキシャル膜を用いる電子デバイスの製造を含んでいる。 (もっと読む)

完全空乏型シリコン・オン・インシュレータのCMOSロジック

【課題】SOI技術を用いた部分空乏型CMOSデバイスにおける浮遊ボディの不必要な影響を制御可能とする。

【解決手段】シリコン・オン・インシュレータのCMOSメモリデバイスにおいて、引き出し線を含む領域が用いられる。引き出し線を逆方向にバイアスすることで、部分空乏型メモリセルのボディ領域から少数キャリアを取り除く。これにより、ボディ領域を完全空乏化し、浮遊ボディの不必要な影響を抑制する。

(もっと読む)

電界効果型半導体装置における容量素子の動的制御

電界効果型装置はキャパシタのプレートをそれぞれ形成する複数のセグメントを有する少なくとも1つのセグメント化されたフィールド・プレートを含んでおり、選択されたセグメントを動的に接続してゲート−ドレイン間容量及びドレイン−ソース間容量を選択的に設定する電子素子に電界効果型装置が接続されている。トランスデューサを送信モードスイッチング装置と、受信モードスイッチング装置との間でスイッチングするスイッチング装置に結合されたトランスデューサを超音波装置が含んでおり、このスイッチング装置は電界効果型装置を含んでいる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

半導体装置

【課題】低オン抵抗の縦型トランジスタが形成されてなる半導体装置を提供する。また、マルチチャネル化の自由度の高い半導体装置を提供する。

【解決手段】半導体基板30の一方の表面である主面側に形成された第1電極と、もう一方の表面である裏面側に形成された第2電極とを有する縦型トランジスタ101が形成されてなる半導体装置100であって、第1電極が、主面上に形成された層間絶縁膜43を介して、主面側の半導体基板30表層部に形成された拡散領域41,42,48に接続する第1金属層44からなり、裏面側には、半導体基板30の内部に向かってトレンチ35が形成され、第2電極が、トレンチ内に形成され、トレンチ35によって露出された半導体基板30内の半導体層33に接続する第2金属層37からなる半導体装置100とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

921 - 940 / 940

[ Back to top ]