Fターム[5F048BG07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 絶縁体分離 (5,896) | 素子領域側面・底面を絶縁物で分離するもの (666) | 複数MOS(CMOS)ですべて (452)

Fターム[5F048BG07]に分類される特許

201 - 220 / 452

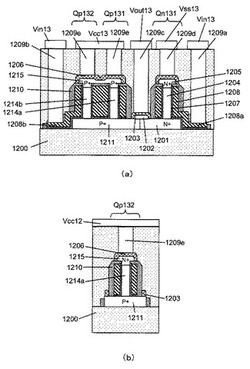

半導体装置およびその製造方法

【課題】縦型MOSトランジスタの小型化、それに伴い増加する寄生抵抗、寄生容量の低減。

【解決手段】基板と、基板上の絶縁膜と、基板上の絶縁膜上に形成された平面状半導体層と、平面状半導体層に形成される第1のドレイン/ソース領域、平面状半導体層上に形成される柱状半導体層、柱状半導体層上部に形成される第2のソース/ドレイン領域、及び柱状半導体層の側壁を包囲するように絶縁膜を介して形成されるゲート電極を含む第1及び第2のMOSトランジスタとを備える半導体装置において、第1又は第2のMOSトランジスタの第2のソース/ドレイン領域の上面の面積は、第1又は第2のMOSトランジスタの柱状半導体層のそれぞれの上面の面積よりも大きく、第1のMOSトランジスタの第1のドレイン/ソース領域の表面の少なくとも一部と第2のMOSトランジスタの第1のドレイン/ソース領域の表面の少なくとも一部とを接続するシリサイド層が形成される。

(もっと読む)

半導体装置

【課題】縦型MOSトランジスタの小型化、及びそれに伴って増加する寄生抵抗、寄生容量を低減すること。

【解決手段】基板と、基板上の絶縁膜と、基板上の絶縁膜上に形成された平面状半導体層と、平面状半導体層に形成されるドレイン又はソース領域、平面状半導体層上に形成される柱状半導体層、柱状半導体層上部に形成されるソース又はドレイン領域、及び柱状半導体層の側壁を包囲するように絶縁膜を介して形成されるゲート電極を含む第1及び第2のMOSトランジスタとを備える半導体装置において、第1のMOSトランジスタの平面状半導体層に形成されるドレイン又はソース領域の表面の少なくとも一部と第2のMOSトランジスタの平面状半導体層に形成されるドレイン又はソース領域の表面の少なくとも一部とを接続するシリサイド層が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】被測定体の表面形状を取得する半導体装置において、表面形状の高解像度化を図る。

【解決手段】被測定体60と各電極28、37との間の静電容量を検出するための各素子29、38が設けられた第1容量検出回路層20および第2容量検出回路層30を積層にし、各素子29、38の各電極28、37を各トレンチ26、35によって保護膜50まで引き伸ばす。これにより、容量検出回路層が一層の場合よりも一定面積当たりに配置できる素子29、38を増加させ、被測定体60の表面形状を高解像度で検出する。

(もっと読む)

SOI基板及びその作製方法並びに半導体装置及びその作製方法

【課題】TFTに適したSOI基板およびその作製方法を提供する。またSOI基板を用いて信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】SIMOX、ELTRAN、Smart−Cutに代表される技術を用いてSOI基板を作製するにあたって、主表面(結晶面)が{110}面である単結晶半導体基板を用いる。その様なSOI基板は下地となる埋め込み絶縁層と単結晶シリコン層との密着性が高く、信頼性の高い半導体装置を実現することが可能となる。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間に配置される絶縁膜(例えば、BOX)にて構成される寄生容量を充放電する変位電流が発生することを抑制し、回路の誤動作を防止する。

【解決手段】低電位基準回路部LVに形成されたシールド層3bをGND電位とし、高電位基準回路部HVに形成されたシールド層3bを仮想GND電位とする。これにより、変位電流が発生した場合には、高電位基準回路部HVの仮想GND配線17bから変位電流引抜き層19およびシールド層3bを通じて支持基板2に至ったのち、低電位基準回路部LVのシールド層3bおよび変位電流引抜き層19を通じてGND配線17aに流れる。したがって、変位電流が低電位基準回路部LVに備えられた各種回路に流れることを防止でき、回路が誤動作してしまうことを防止することが可能となる。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間に配置される絶縁膜(例えば、BOX)にて構成される寄生容量を充放電する変位電流が発生することを抑制し、回路の誤動作を防止する。

【解決手段】低電位基準回路部LVに形成された第1サージ吸収層2aがトレンチ分離部5b内のドープトPoly−Si8bを通じてGND配線17aに電気的に接続されることでGND電位とされ、高電位基準回路部HVに形成された第2サージ吸収層2bがトレンチ分離部5b内のドープトPoly−Si8bを通じて仮想GND配線17bに電気的に接続されることで仮想GND電位とされるようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】膜厚の異なるSOI層に複数種のトランジスタを形成した半導体装置において、複数種のトランジスタ間の素子分離が精度良く行える半導体装置及びその製造方法を得る。

【解決手段】SOI層3は厚膜SOI領域101及び薄膜SOI領域102を有し、厚膜SOI領域101の上層部はエピタキシャルSOI層で形成され、このエピタキシャルSOI層の膜厚分、厚膜SOI領域101のSOI膜厚t1は、薄膜SOI領域102のSOI膜厚t2より厚い。厚膜SOI領域101,薄膜SOI領域102間は完全分離酸化膜10fにより素子分離される。厚膜SOI領域101内及び薄膜SOI領域102内はそれぞれ部分分離酸化膜10pにより隣接するトランジスタ間が素子分離される。完全分離酸化膜10f及び部分分離酸化膜10pの上面は厚膜SOI領域101及び薄膜SOI領域102におけるSOI層3の上面よりも高く形成される。

(もっと読む)

表示モジュールの作製方法

【課題】半導体素子の作製時に用いた基板から、半導体素子を含む素子形成層を剥離するときに、剥離によって発生した静電気による放電を抑える。

【解決手段】基板10上に剥離層12、素子形成層11を形成する。素子形成層11の上面には、後で剥離可能な支持基材13が固定される。支持基材13を介して、素子形成層11を変形させ、素子形成層11と剥離層12の界面で剥離を生じさせる。剥離によって逐次現れる素子形成層11および剥離層12が純水などの液体15で濡れるように、液体15を供給しながら剥離を行う。液体15により素子形成層11および剥離層12の表面に発生した電荷が拡散され、剥離帯電による放電をなくすことができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】多数キャリアの移動度を向上させたSBSIデバイスを実現可能とした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】Si基板1上にSiGe層を形成する工程と、SiGe層上にSi層5を形成する工程と、Si層5及びSiGe層をエッチングして、Si層5及びSiGe層を貫く支持体穴を形成する工程と、支持体穴に支持体11、12を形成する工程と、Si層5をエッチングして、SiGe層を露出させる溝H1、H2を形成する工程と、溝H1、H2を介してSiGe層をエッチングすることにより、Si層5とSi基板1との間に空洞部を形成する工程と、空洞部にSiO2膜23を形成する工程と、引っ張り応力を有する埋め込み膜31を溝H1、H2に形成する工程と、を含む。支持体11には引っ張り応力を有する絶縁膜を用い、支持体12には圧縮応力を有する絶縁膜を用いる。

(もっと読む)

半導体装置の製造方法及び混成トランジスタ用半導体装置の製造方法

【課題】MOSトランジスタの寄生抵抗の低減化を図るとともに、ソース・ドレイン領域及びエクステンション部を構成するエピタキシャル成長領域の安定化を図った半導体装置の製造方法を得る。

【解決手段】ポリシリコンゲート5の側面にオフセット部をオフセットスペーサ用酸化膜31及びオフセットスペーサ用窒化膜32の2層構造で形成し、さらにその側面にサイドウォール用酸化膜33及びダミーサイドウォール用窒化膜を形成した後、当該ダミーサイドウォール用窒化膜を熱燐酸を用いて除去する。その結果、選択エピ成長領域12とポリシリコンゲート5との間に段差部19が形成される。そして、ポリシリコンゲート5、上記酸化膜及び窒化膜31〜33をマスクとして、ゲート外SOI領域3e、選択エピ成長領域11及び12にExt用不純物22及びHalo用不純物23を順次注入,拡散する。

(もっと読む)

半導体装置

【課題】良好な特性を得ながら、小型化、高耐圧化および低消費電力化が可能な半導体装置を提供する。

【解決手段】この半導体装置1は、シリコンよりも大きいバンドギャップを有し、パワートランジスタ2が形成されたSiC層11と、SiC層11の主表面11aよりも上側の所定領域に形成されるとともに、制御回路用のNMOSトランジスタ3およびPMOSトランジスタ4が形成され、SiC層11とは別の層からなるシリコン層21と、SiC層11のパワートランジスタ2とシリコン層21のNMOSトランジスタ3およびPMOSトランジスタ4とを接続するAl配線5とを備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】キャリアの移動度が高い歪SOI構造を、結晶欠陥少なく且つ安価に形成できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】Si基板1上にSiGe層とSi層5とを順次形成し、その上にSi3N4膜9、13を形成する。次に、Si3N4膜9、13と、Si層5及びSiGe層を貫く支持体穴hを形成する。そして、支持体穴hを埋め込むようにSiO2膜21を形成する。次に、SiO2膜21とSi層5とを部分的にエッチングして、SiGe層を露出させる溝Hを形成する。そして、この溝Hを介してSiGe層をエッチングすることにより、Si層5とSi基板1との間に空洞部25を形成し、空洞部25を埋め込むようにSiO2膜を形成する。この際、Si3N4膜9が有する圧縮応力と、Si3N4膜13が有する引っ張り応力とをSi層5にそれぞれ作用させてSi層5の歪を増大させる。

(もっと読む)

半導体装置の作製方法、半導体装置及び電子機器

【課題】製造コストを低減しつつ、高速動作が可能な回路を有する半導体装置の作製方法を提供することを課題の一とする。または、該半導体装置を提供するための半導体基板の作製方法を提供することを課題の一とする。または、該半導体装置を用いた電子機器を提供することを課題の一とする。

【解決手段】基板上に非単結晶半導体層を形成した後、非単結晶半導体層の一部の領域上に単結晶半導体層を形成する。これにより、非単結晶半導体層を用いて大面積が必要とされる領域(例えば、表示装置における画素領域)の半導体素子を形成し、単結晶半導体層を用いて高速動作が求められる領域(例えば、表示装置における駆動回路領域)の半導体素子を形成することができる。

(もっと読む)

SOI基板を用いた半導体装置およびその製造方法

【課題】信号処理回路や大電力回路のような様々な回路を混載する場合にも1チップで対応でき、かつ、SOI層の厚膜化を抑制できる構造の半導体装置を提供する。

【解決手段】SOI基板4を用い、SOI層1を小電力回路部R1とし、支持層2を大電力回路部R2とする。このため、SOI層1の膜厚を小電力回路部R1を考慮した厚みにすれば良く、大電力回路部R2の耐圧等を考慮した厚みにしなくても良い。したがって、厚いSOI層内にウェル層を形成した場合のようなウェル層の境界部を無くすことが可能となり、寄生容量を無くせると共に、寄生容量に起因する消費電力の増大や演算速度の低下を防止することが可能となる。一方、大電力回路部R2を十分な厚みを有する支持層2に形成しているため、耐圧等も確保することが可能となる。

(もっと読む)

半導体基板及びそれを用いた半導体装置、並びにそれらの作製方法

【課題】より動作特性の高い半導体装置の作製及び半導体集積回路の低消費電力化を課題とする。

【解決手段】同一基板平面上に形成されたN導電型薄膜トランジスタのチャネル領域とP導電型薄膜トランジスタのチャネル領域となる単結晶半導体層の結晶面方位が、それぞれの薄膜トランジスタにおいて最適な結晶面方位となるように形成する。このような構成とすることで、チャネルを流れるキャリア移動度が向上し、より動作特性の高い半導体装置を提供できる。また、低電圧で駆動することが可能となり、低消費電力化を図ることができる。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間の絶縁膜にて構成される寄生容量を充放電する変位電流が発生することを抑制し、回路の誤動作を防止する。

【解決手段】低電位基準回路部LVの下と高電位基準回路部HVの下にのみ支持基板2を残す。これにより、支持基板2のうち低電位基準回路部LVの下の部分と高電位基準回路部HVの下の部分とが絶縁部材30にて絶縁された状態となる。このため、埋込酸化膜3のうち高電位基準回路部HVと支持基板2との間に配置される部分にて構成される寄生容量と低電位基準回路部LVと支持基板2との間に配置される部分にて構成される寄生容量が電気的に遮断される。したがって、寄生容量を充放電する変位電流の発生を抑制することができ、回路を誤動作させてしまわないようにできる。

(もっと読む)

バススイッチおよび電子スイッチ

【課題】バスに異常が発生したとしても当該異常状態を回避して通常動作を維持できるようにする。スイッチング素子をオフしたときにも生じる寄生素子によるリーク電流の発生を抑制して正常な切断を可能にする。

【解決手段】ハイサイドスイッチSWHが高電位側バスDnHの入力端子INHと出力端子OUTHとの間に接続されていると共に、ロウサイドスイッチSWLが低電位側バスDnLの入力端子INLと出力端子OUTLとの間に接続されているため、当該スイッチSWHおよびSWLが共にオフすることでモジュール間のバス接続を確実に切断することができ、たとえバスに異常が発生したとしても安定した動作を保持できる。ロウサイドスイッチSWLおよびハイサイドスイッチSWHは、MOSトランジスタM1、M2がソース共通で直列接続されているため寄生素子が発生しにくく、ゲート‐ソース間が抵抗接続されているため幅広い電圧範囲に対して確実にバス接続を切断することができる。

(もっと読む)

半導体装置

【課題】応答性に優れ、瞬間的な動作や過大入力がある場合においてもダイオード素子の順方向動作時の損失増加や過剰電流による絶縁ゲートトランジスタ素子の破壊を防止できる小型の半導体装置を提供する。

【解決手段】絶縁ゲートトランジスタ素子21とダイオード素子22とが同じ半導体基板に形成され、絶縁ゲートトランジスタ素子21とダイオード素子22が逆並列に接続されてなる半導体装置60であって、ダイオード素子22に電流が流れた場合に、絶縁ゲートトランジスタ素子21のゲート(G)端子の電位を下げて、該絶縁ゲートトランジスタ素子21のゲートをオフする第1制御トランジスタ素子ST1が、前記半導体基板に形成されてなる半導体装置60とする。

(もっと読む)

単結晶半導体層の形成方法、結晶性半導体層の形成方法、多結晶半導体層の形成方法、及び、半導体装置の作製方法

【課題】大型の絶縁基板上に、大面積を有する単結晶半導体層を形成することを課題とする。

【解決手段】単結晶半導体インゴットの側面に第1の多孔層及び第2の多孔層を形成し、第2の多孔層上の一部に、溝と単結晶半導体層を形成し、大型絶縁基板上に、単結晶半導体インゴットを貼り合わせ、第1の多孔層と第2の多孔層の界面に、ウォータージェットを当て、単結晶半導体層を大型絶縁基板に貼り合わせる単結晶半導体層の形成方法、あるいは、結晶性半導体インゴットに水素イオンを照射し、結晶性半導体インゴット中に水素イオン照射領域を形成し、結晶性半導体インゴットを加熱しながら大型絶縁基板上で回転させ、水素イオン照射領域から結晶性半導体層を分離し、大型絶縁基板上に貼り合わせる結晶性半導体層の形成方法に関する。

(もっと読む)

半導体基板の作製方法及び半導体装置の作製方法

【課題】ガラス基板など耐熱温度が低い基板を用いた場合にも、実用に耐えうる単結晶半導体層を備えた半導体基板の作製方法を提供することを目的の一とする。また、そのような半導体基板を用いた信頼性の高い半導体装置を作製することを目的の一とする。

【解決手段】単結晶半導体基板より支持基板に転載され、全領域においてレーザ光照射による溶融状態を経て再単結晶化された単結晶半導体層を有する半導体基板を用いる。従って、単結晶半導体層は結晶欠陥も低減され結晶性が高く、かつ平坦性も高い。

(もっと読む)

201 - 220 / 452

[ Back to top ]