Fターム[5F048CA03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | バイポーラトランジスタの構造 (853) | 基板上のエピ層に形成 (158)

Fターム[5F048CA03]に分類される特許

1 - 20 / 158

半導体装置の製造方法

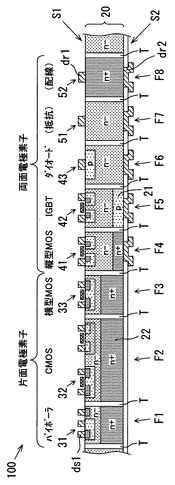

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体装置及びその製造方法

【課題】バーティカル型のバイポーラトランジスタにおいて、エミッタ領域からベース領域にかけて存在する界面準位を安定に低減することを可能とした半導体装置とその製造方法を提供する。

【解決手段】バーティカル型のバイポーラトランジスタ10は、シリコン基板1に形成されたP型のベース領域13と、シリコン基板1に形成されてベース領域13に接するエミッタ領域15と、シリコン基板1の表面であってベース領域13とエミッタ領域15との境界部21上に形成されたシリコン酸化膜17と、シリコン酸化膜17上に形成されたポリシリコンパターン19と、を有する。シリコン酸化膜17とシリコン基板1との界面に塩素が1×1017cm−3以上の濃度で存在する。

(もっと読む)

半導体デバイス

【課題】高い電流増幅率と高いアーリー電圧を両立することができ、CMOSトランジスタとともに製造する場合でもより少ない製造工程により製造することができる半導体デバイスを提供する。

【解決手段】基板P11の表面に形成された第1導電型のベースP14と、ベースの表面に形成された第2導電型のエミッタN23と、ベースの表面においてエミッタと離間して配置され、エミッタから第1の種類のキャリアを受け取るとともに、その第1の種類のキャリアをベースへ注入する、第2導電型のドープ領域N24と、ベースを挟んで、エミッタおよびドープ領域の反対側に形成された、第2導電型のコレクタN15とを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタポリシリコンに対する良好なコンタクトを得ることができる半導体装置及びその半導体装置の製造方法を提供する。

【解決手段】ラテラル・バイポーラトランジスタを有する半導体装置であって、ラテラル・バイポーラトランジスタは、第1の導電層を構成する基板と、第1の導電層上に配置されたn−hill層312と、n−hill層312を囲む素子分離酸化膜320に開口されたオープン領域と、オープン領域上に形成されるポリシリコン膜910と、ポリシリコン膜910から固相拡散されたエミッタ領域と、素子分離酸化膜320に形成されたダミーゲートポリシリコン706と、を有し、ダミーゲートポリシリコン706によってポリシリコン膜910からの固相拡散されるエミッタ領域の形状が制御される。

(もっと読む)

半導体装置

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタ、コレクタ間の耐圧をより高めることができる半導体装置を提供する。

【解決手段】HCBT100は、第1の導電層を構成する基板1と、n−hill層11と、素子分離酸化膜6とを備え、n−hill層11は第2の導電層と第3の導電層を含み、第3の導電層は第4の導電層を含み、第4の導電層はエミッタ電極31Aと接続し、コレクタ電極31Bをさらに備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bを備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bは、コレクタ電極31B同士を結ぶ直線と、n−hill層11に備わる少なくとも一つの側面の2つの対向する位置を結ぶ直線とが直交する位置にあることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】BiCMOSプロセスにより製造される半導体装置において、V−NPNトランジスタの製造工程を合理化する。また、そのトランジスタのhFEを大きな値に調整する。

【解決手段】N+型エミッタ領域14Eの下のP型ベース領域7の底部に接触してN型ベース幅制御層9が形成されている。N型ベース幅制御層9が形成されることで、N+型エミッタ領域14Eの下のP型ベース領域7が局所的に浅くなっている。また、P型ベース領域7は、P型ウエル領域6の形成工程を用いて形成し、N型ベース幅制御層9は、N型ウエル領域8の形成工程を用いて形成することにより、工程合理化を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】異なる不純物濃度の埋め込み層を有する半導体装置を短時間かつ低コストで製造する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の表面に第1の酸化膜11を形成する第1の酸化膜形成ステップと、フォトダイオードが形成される第1の領域に形成された前記酸化膜の一部を除去して第1の間隔で第1の開口部を形成すると共に、トランジスタが形成される第2の領域に形成された前記酸化膜を除去して前記半導体基板の表面を露出させる第1の開口部12を形成ステップと、前記第1の酸化膜をマスクとして利用して前記第1の開口部及び前記第2の領域に対して第1の不純物を注入する第1の不純物注入ステップと、前記第1の不純物を熱拡散させる第1の熱拡散ステップと、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

半導体装置

【課題】逆耐圧を高くしてもオン抵抗が高くなることのない半導体装置を提供する。

【解決手段】n型半導体層116と、n+型半導体層116よりも低濃度のn型不純物を含有するn型のドリフト層112と、ドリフト層112の表面に形成した、拡散深さが深いボディ部分118aと、拡散深さが浅いチャネル部分118bとからなるp型のボディ領域118と、ボディ領域118の表面に形成したn+型のソース領域120と、チャネル部分118bの上にゲート絶縁層122を介して形成したゲート電極124とを備える半導体装置であって、平面的に見てボディ領域118と重ならない領域に位置するドリフト層112には、ドリフト層112よりも高濃度のn型不純物を含有するn型の低抵抗領域144aがn+型半導体層116と接するように形成されている半導体装置100。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

半導体装置及びその製造方法

【課題】容易なプロセスにより単結晶半導体層を形成したSOI構造のMISFETの提供

【解決手段】半導体基板1上に、第1の絶縁膜2を介して、一部に空孔4を有する第2の絶縁膜3が設けられ、空孔4上及び第2の絶縁膜3の一部上に島状に絶縁分離された半導体層6が設けられ、半導体層6上にゲート酸化膜12を介して、空孔4直上に空孔4の幅以下のゲート電極13が設けられ、半導体層6には、ゲート電極13に自己整合して低濃度のソースドレイン領域(9,10)が、ゲート電極13の側壁に設けられたサイドウォール14に自己整合して高濃度のソースドレイン領域(8,11)がそれぞれ設けられ、ゲート電極13(配線図示せず)及び高濃度のソースドレイン領域(8,11)にはバリアメタル17を有する導電プラグ18を介してバリアメタル20を有する配線21が接続されているMISFET。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に含まれる静電気保護装置の面積を大きくすることなく、その破壊耐量及び維持電圧を大きくする。

【解決手段】第1導電型である半導体基板1と、半導体基板の上又は上部に形成された第2導電型である第1拡散層3と、第1拡散層の上部に形成され、第1導電型である第2拡散層5と、第2拡散層の上部に形成され、第2導電型である第3拡散層6と、第1拡散層の上部で且つ第2拡散層から間隔をおいて形成された第2導電型である第4拡散層8と、少なくとも第3拡散層の下に、第2拡散層と間隔をおき且つ下端部が第1拡散層の下端部よりも下に位置するように形成された第1導電型の第5拡散層2とを備えている。第3拡散層から第5拡散層までの最短距離と、第5拡散層から第4拡散層までの最短距離及び第1拡散層の下端部から第4拡散層までの最短距離のいずれか短い方の距離との和は、第3拡散層から第4拡散層までの最短距離よりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】結晶欠陥による接合リークを防止しながら、バイポーラトランジスタの面積を縮小し、コレクタ容量の低減によってトランジスタ特性を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】活性領域1からSTI4上にかけて連続して形成したSiGe膜は、半導体基板3上ではSiGeエピ膜6となり、STI4上ではSiGeポリ膜7となる。半導体基板3とSTI4の境界はSiGe−HBT形成工程以前の洗浄工程によって段差15が生じており、SiGeエピ膜6及び半導体基板3には、上記境界を基点とした結晶欠陥が応力によって発生する可能性がある。この境界に第1のP型不純物層8及び第2のP型不純物層9を設けることで、結晶欠陥をこれらP型不純物層8、9に内包し、接合リークの発生を抑制する。

(もっと読む)

トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

【課題】表面上に素子をより高密度に実装する。

【解決手段】第1のトレンチと第2のトレンチとの間の位置において、エピタキシャル層の表面から基板へと下方に延在するドーパントのウェルは、エピタキシャル層の背景ドーピング濃度とは異なるドーピング濃度を有し、エピタキシャル層の残りの部分と第1および第2の接合を形成する。第1の接合は、第1のトレンチの底部から基板に延在し、第2の接合は、第2のトレンチの底部から前記基板に延在する。ウェルおよび第1および第2のトレンチは分離構造を構成し、分離構造は、分離構造の一方側のエピタキシャル層に形成された第1の素子と分離構造の他方側のエピタキシャル層に形成された第2の素子とを電気的に分離する。分離構造による電気的分離は第1および第2のトレンチとPN接合とによってもたらされ、ウェルは第1の導電型の材料でドープされ、基板およびエピタキシャル層は、第1の導電型とは反対の第2の導電型の材料でドープされ、第1および第2の接合はPN接合である。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】CMOS回路側の仕様で不純物領域の深さや濃度が制約を受けるような場合でもhFEの向上を可能とする。

【解決手段】1つのバイポーラトランジスタが、横型の主トランジスタ部と、縦型の補助トランジスタ部とから形成されている。横型の主トランジスタ部は、エミッタ領域31と、ベース領域14Bの表面側部分とコレクタ側部領域13Bとを電流チャネルとして動作する。縦型の補助トランジスタ部は、エミッタ領域31と、その底面に接するベース領域14Bの深部側部と、コレクタ深部領域12Bとを電流チャネルとして動作する。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSプロセスへの導入が容易で、エミッタ−ベース間のリーク電流(電界強度)を低減し、ノイズやサージ電圧の影響を受けにくい高性能な半導体装置とその製造方法の提供。

【解決手段】導電膜をマスクとして、2回のイオン注入を行ってエミッタを形成する。第2エミッタ領域111bは、低濃度の不純物イオン注入によって形成し、第1エミッタ領域111aは、高濃度の不純物イオン注入によって形成する。その結果、エミッタの周縁部に低濃度の第2エミッタ領域が形成され、電界が緩和され、リーク電流が低減する。また、導電膜とエミッタ電極116とが接続され、ノイズの影響を受けにくくなる。

(もっと読む)

半導体装置

【課題】低酸素処理を施したシリコン基板は基板表面層が応力に対して非常にもろくなってしまい、ハンド津愛想うちの製造プロセスの過程でクラックや反りが発生する原因ともなってしまう。

【解決手段】チャネル形成領域に形成された不純物領域に応力を集中させるため、チャネル形成領域に対して人為的かつ局部的に不純物領域を設ける。チャネル形成領域に局部的に添加された不純物元素(炭素、窒素、酸素から選ばれた一種または複数種類の元素)の領域は、低酸素処理を施したシリコン基板の応力を緩和する緩衝領域として機能する。

(もっと読む)

半導体装置

【課題】バイポーラの高耐圧縦型PNPプロセスをベースにして、寄生PNPトランジスタに起因する漏洩電流の発生しない高耐圧IGBTを形成する。

【手段】P型半導体基板1に、IGBTのコレクタ電極15と電気的に接続するP+型コレクタ層8と、当該P+型コレクタ層8と連続するP+型埋め込み層4と、該P+型埋め込み層4の下層のN型埋め込み層2と、該P+型埋め込み層4と該N型埋め込み層2の間のN+型埋め込み層3とを形成する。また、N+型埋め込み層3の端部と一体となり、前記P型半導体基板1上に形成されたN型エピタキシャル層5の表面まで延在し、コレクタ電極15と電気的に接続されたN+型導電層7を形成する。

(もっと読む)

半導体装置およびプラズマディスプレイデバイス

【課題】寄生抵抗が小さく、かつ電流駆動能力が大きい高耐圧ハイブリッドトランジスタのような半導体装置の構造を提供する。

【解決手段】第1導電型の半導体層22に第1導電型のベース領域9を備える。ベース領域9には第2導電型のエミッタ領域10が設けられる。半導体層22にはベース領域9に隣接して半導体層22の表面から半導体層22の厚さより小さい所定深さにわたって第2導電型の不純物層23が設けられる。不純物層23にはベース領域9から離間して第1導電型のコレクタ領域11および第2導電型のドレイン領域14が設けられる。半導体層22の表面上には、エミッタ領域10の端部上、ベース領域9上および不純物層23上の一部にわたってゲート絶縁膜12を介してゲート電極13が設けられる。エミッタ領域10とベース領域9とに共通接続された第1電極15と、コレクタ領域11とドレイン領域14とに共通接続された第2電極16とを備える。

(もっと読む)

1 - 20 / 158

[ Back to top ]