Fターム[5F048CB07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 3次元MOSIC(BiMOSを含む) (767) | 縦型MOSIC、ダブルゲートMOS (373) | 垂直チャネル (271)

Fターム[5F048CB07]に分類される特許

1 - 20 / 271

半導体装置の製造方法

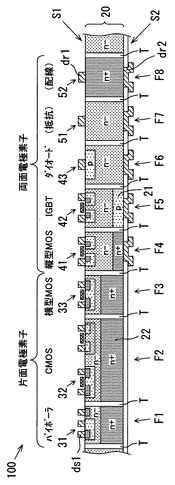

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体装置

【課題】 過電流検出による保護と、温度検出による保護とを、好適に行うことが可能な半導体装置を提供する。

【解決手段】 半導体基板を有する半導体装置であって、半導体基板が、メイン素子領域と、メイン素子領域よりも小さい電流が流れるサブ素子領域を有しており、サブ素子領域が、半導体基板を平面視したときに半導体基板の中心と重なる位置に形成されており、半導体基板上であって、半導体基板を平面視したときにサブ素子領域と重なる位置に、温度検出素子が形成されている。

(もっと読む)

CMOS垂直置換ゲート(VRG)トランジスタ

【課題】本発明は、CMOS垂直置換ゲート(VRG)トランジスタを提供する。

【解決手段】集積回路構造は平面に沿って形成された主表面を有する半導体領域及び表面中に形成された第1及び第2のソース/ドレインドープ領域を含む。絶縁トレンチが第1及び第2のソース/ドレイン領域間に形成される。第1のソース/ドレイン領域とは異なる伝導形のチャネルを形成する第3のドープ領域が、第1のソース/ドレイン領域上に配置される。第4のドープ領域が第2のソース/ドレイン領域上に形成され、第2のソース/ドレイン領域とは相対する伝導形をもち、チャネル領域を形成する。第5及び第6のソース/ドレイン領域が、それぞれ第3及び第4のドープ領域上に形成される。

(もっと読む)

炭化珪素半導体装置

【課題】 少ない工程数で形成でき、耐熱性に優れた温度センサを備える炭化珪素半導体装置を得る。

【解決手段】 炭化珪素基板1の活性領域ARに形成された半導体素子と、活性領域ARを取り囲むように炭化珪素基板1中に形成されたウエル領域5と、炭化珪素基板1上に配設される多結晶シリコンからなるゲート電極8と、ゲート電極8と同時に形成され、その一部を用いて形成した測温抵抗体17と、を備えることを特徴とする。

(もっと読む)

ゲート駆動回路

【課題】逆導通IGBTに内蔵されたダイオードで発生するリカバリ電流を低減させる。

【解決手段】逆導通IGBTに内蔵されているダイオードに順方向電流が流れている間に、逆導通IGBTのゲート−エミッタ間にゲート閾値電圧よりも低い電圧を印加することで、逆導通IGBTのドリフト領域への正孔の注入を抑制し、リカバリ電流を低減させる。

(もっと読む)

トレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法

【課題】製造コストの増加を抑制し、キャパシタの端部の段差を小さくできるトレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法を提供することにある。

【解決手段】トレンチ52内壁に分離絶縁層53を配置し、この分離絶縁層53を介して下部電極となる第1ポリシリコン54を埋め込んだトレンチ型PIPキャパシタ50を半導体基板に形成することで、キャパシタの端部に形成される段差を低減できる。その結果、配線となるメタル層59を過度に厚くする必要がなく、メタル層59を微細化することができる。その結果、パワーICを微細化することができる。

(もっと読む)

半導体装置

【課題】IGBT終端部でのリカバリ破壊を防ぎ、ダイオードのスナップバックを抑制することができる半導体装置を提供する。

【解決手段】N−型のドリフト層30の上に形成されたP型のチャネル層31を含む半導体基板32のうちチャネル層31側の一面33とは反対側の他面34側に、P++型のコレクタ層53とN++型のカソード層54とが同じ階層に形成されている。そして、P++型のコレクタ層53がトレンチ35の延設方向における表面IGBT専用領域10および表面ダイオード専用領域20の周辺部25にそれぞれ設けられていることによりN++型のカソード層54は四角形状にレイアウトされている。また、P++型のコレクタ層53がエミッタ領域39の終端部39aから距離aを半径とする円形状に設けられていることにより当該四角形状の角部が窪んだ形状にレイアウトされている。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のトランジスタのシリコンピラー上部に活性領域を設ける際に、エピタキシャル成長により前記シリコンピラー上部に形成されるシリコン膜の高さが、前記トランジスタ毎にばらつくことを防ぎ、前記シリコン膜への導電型ドーパントの注入深さを均一にする半導体装置の製造方法を提供する。

【解決手段】基板の主面に柱状のシリコンピラーを形成するシリコンピラー形成工程と、前記シリコンピラーを覆うように第1の絶縁膜を形成する第1絶縁膜形成工程と、前記第1の絶縁膜を上面から除去し、前記シリコンピラー上部の上面及び側面を露出させる第1絶縁膜除去工程と、前記シリコンピラー上部の上面及び側面にエピタキシャル成長法によりシリコン膜を形成するシリコン膜形成工程とを有する。

(もっと読む)

半導体装置

【課題】抵抗値が制御されることができる抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、絶縁膜14bと、半導体素子と、抵抗素子4tとを有する。絶縁膜14bは半導体基板101の少なくとも一部を被覆している。半導体素子は、半導体基板101の一部からなるチャネル領域と、電極とを有する。抵抗素子4tは、電極を流れる電流に対する抵抗となるように電極と電気的に接続され、かつ絶縁膜14bを介して半導体基板101上に設けられている。抵抗素子4tは半導体領域を含む。半導体基板101と抵抗素子4tとの間の電位差により半導体領域に空乏層が生じる。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

ダイオード、半導体装置およびMOSFET

【課題】 ダイオードにおけるスイッチング時の損失を低減することが可能な技術を開示する。

【解決手段】 本明細書で開示するダイオードは、カソード電極と、第1導電型の半導体からなるカソード領域と、低濃度の第1導電型の半導体からなるドリフト領域と、第2導電型の半導体からなるアノード領域と、金属からなるアノード電極を備えている。そのダイオードは、前記ドリフト領域と前記アノード領域の間に形成された、前記ドリフト領域よりも濃度が高い第1導電型の半導体からなるバリア領域と、前記バリア領域と前記アノード電極を接続するように形成された、前記バリア領域よりも濃度が高い第1導電型の半導体からなるピラー領域を備えている。そのダイオードでは、前記ピラー領域と前記アノード電極がショットキー接合している。

(もっと読む)

ダイオードおよび半導体装置

【課題】 ダイオードにおけるスイッチング時の損失を低減することが可能な技術を提供する。

【解決手段】 本明細書は、カソード電極と、第1導電型の半導体からなるカソード領域と、低濃度の第1導電型の半導体からなるドリフト領域と、第2導電型の半導体からなるアノード領域と、アノード電極を備えるダイオードを開示する。そのダイオードは、ドリフト領域とアノード領域の間に形成された、ドリフト領域よりも濃度が高い第1導電型の半導体からなるバリア領域と、アノード電極と接触するように形成された、第1導電型の半導体からなるコンタクト領域と、コンタクト領域とバリア領域の間のアノード領域に対して絶縁膜を挟んで対向する制御電極を備えている。そのダイオードでは、制御電極に電圧が印加されると、コンタクト領域とバリア領域の間のアノード領域に第1導電型のチャネルが形成される。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】スイッチング用のパワーMOSFETと、そのパワーMOSFETよりも小面積でかつそのパワーMOSFETに流れる電流を検知するためのセンスMOSFETとが1つの半導体チップCPH内に形成され、この半導体チップCPHはチップ搭載部上に導電性の接合材を介して搭載され、樹脂封止されている。半導体チップCPHの主面において、センスMOSFETが形成されたセンスMOS領域RG2は、センスMOSのソース用のパッドPDHS4よりも内側にある。また、半導体チップCPHの主面において、センスMOS領域RG2は、パワーMOSFETが形成された領域に囲まれている。

(もっと読む)

半導体装置

【課題】1個の柱を用いてインバータを構成することにより、高集積なCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】第1のシリコンと、該第1のシリコンとは極性が異なる第2のシリコンと、前記第1のシリコンと前記第2のシリコンとの間に配置され、基板に対して垂直方向に延びている第1の絶縁物とからなる1本の柱と、前記第1のシリコンの上下のそれぞれに配置され、前記第1のシリコンとは極性が異なる第1の高濃度不純物を含むシリコン層と、前記第2のシリコンの上下のそれぞれに配置され、前記第2のシリコンとは極性が異なる第2の高濃度不純物を含むシリコン層と、前記第1のシリコンと前記第2のシリコンと前記第1の絶縁物とを取り囲む第2の絶縁物と、前記第2の絶縁物を取り囲む導電体とを含む半導体装置により、上記課題を解決する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型トランジスタの特性にばらつきが生じることを抑制する。

【解決手段】半導体基板100には縦型MOSトランジスタ20が形成されている。半導体基板100の表面上には、第1層間絶縁膜300及び第1ソース配線312が形成されている。第1ソース配線312は、第1層間絶縁膜300上に形成されており、平面視で縦型MOSトランジスタ20と重なっている。第1層間絶縁膜300にはコンタクト302が埋め込まれている。コンタクト302は、縦型MOSトランジスタ20のn型ソース層140と第1ソース配線312とを接続している。そして第1ソース配線312には、複数の開口316が形成されている。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置、半導体装置の製造方法、電子装置、及び車両

【課題】縦型バイポーラトランジスタのSOA(安全動作領域)が狭くなることを抑制する。

【解決手段】p型ベース層150は、厚さ方向の不純物プロファイルにおいて、第1のピーク、第2のピーク、及び第3のピークを有している。第1のピークは、最も半導体基板100の表面側に位置している。第2のピークは、第1のピークよりも半導体基板100の裏面側に位置しており、第1のピークよりも高い。第3のピークは、第1のピークと第2のピークの間に位置している。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 基板表面にパターンニングされたポリシリコン層(ゲート配線や保護ダイオード)が閉ループ状の場合、特にウエハの周辺部分に配置されるチップでは、層間絶縁膜形成時にSOG膜のスピンコートでチップコーナー部分などにおいてSOG液の液だまりが生じ、層間絶縁膜の膜厚が不均一となり、厚膜化した箇所ではコンタクトホールの形成不良が発生する問題があった。

【解決手段】 ゲート配線と保護ダイオードが連続した閉ループ状とならないように、ゲート配線のコーナー部と、ゲート配線および保護ダイオードの隣接部分に開放部を設ける。

(もっと読む)

1 - 20 / 271

[ Back to top ]