Fターム[5F049PA05]の内容

受光素子−フォトダイオード・Tr (21,418) | 製造方法(工程) (2,065) | 薄膜技術 (312)

Fターム[5F049PA05]の下位に属するFターム

Fターム[5F049PA05]に分類される特許

61 - 80 / 103

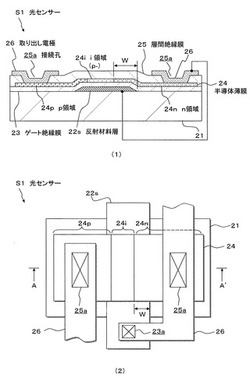

光センサーおよび表示装置

【課題】基板の上方からの光の受光感度の向上を図ることが可能な光センサー、およびこの光センサーを用いた表示装置を提供することを目的とする。

【解決手段】第1基板21上の半導体薄膜24中に、p領域(p型の不純物領域)24pと、i領域(i型の不純物領域)24i、n領域(n型の不純物領域)24nとをこの順に接して設けてなる光センサーS1において、第1基板21と半導体薄膜24との間には、第1基板21側から順に、i領域24iに積層された反射材料層22sと、これを覆うゲート絶縁膜23とが設けられている。反射材料層22sは、n領域24nに接続されている。

(もっと読む)

光電子デバイス

本発明は、基板上に第1層と第2層とを具備する光電子デバイスに関する。前記光電子デバイスは、前記第1層がフッ素含有基を有する電極材料を含み、前記第2層がフッ素含有基を有する高分子材料を含み、前記第1層と前記第2層のフッ素含有基の一部の間で接着性のフッ素−フッ素相互作用を生じることを特徴とする。本発明はさらに、本発明による光電子デバイスの使用および本発明による光電子デバイスの製造方法にも関する。 (もっと読む)

プラズモン共鳴型光電変換素子および該製造方法

【課題】プラズモン共鳴により光を吸収する金属の腐食、電解質溶液中への溶出が抑えられたプラズモン共鳴型光電変換素子および該製造方法を提供する。

【解決手段】酸化還元種を含む電解質溶液20を介して配置されているカソード電極10とアノード電極30とを備え、カソード電極10が、透明基板11と、透明基板11上に順次積層された透明導電性電極12、金属薄膜13、およびn型半導体からなる半導体薄膜14とを有し、半導体薄膜14表面が電解質溶液20に接触していることを特徴とするプラズモン共鳴型光電変換素子1、および該製造方法。

(もっと読む)

PINフォトダイオードの製造方法

【課題】 従来と比較して光電変換効率(感度)をより向上させたフォトダイオードおよびフォトダイオードの製造方法を提供する。

【解決手段】 PINフォトダイオード100は、P型シリコン基板と、P型のシリコン層112と、P型のシリコン層112上に形成され、シリコン層112との接合面を含むN型のシリコン層114と、シリコン層114の表面から一定の深さに形成され、シリコン層114の不純物濃度よりも不純物濃度が高いN型の低抵抗のシリコン領域116と、シリコン領域116上に形成されたシリコン酸化膜120と、シリコン酸化膜120上に形成されたシリコン窒化膜122とを有する。

(もっと読む)

撮像素子及び撮像装置

【課題】発光領域と受光領域とが混在するシート状の撮像素子であって、医療用に最適な撮像素子を提供する。

【解決手段】平面視において発光領域2bと受光領域2aとが混在したシート状の撮像素子2であって、シート状の透光性基板23と、透光性基板23の表面上方の受光領域2aに形成された光電変換素子25と、透光性基板23の表面上方の発光領域2bに形成された光を透過する透光部24と、透光性基板23の裏面側から透光性基板23を介して透光部24に光を入射する発光シート22とを備え、透光性基板23が赤外光を透過するものであり、光電変換素子25が赤外光を検出するものであり、透光部24が赤外光を透過するものであり、発光シート22が赤外光を透光部24に入射するものである。

(もっと読む)

イメージセンサ及びその製造方法

【課題】本発明は、トランジスタ回路とフォトダイオードの新たな集積を提供できるイメージセンサ及びその製造方法を提供するためのものである。

【解決手段】本発明に係るイメージセンサは、基板上に形成された回路(circuitry)と、上記基板上に形成された下部配線と、上記下部配線上に形成されたカーボンナノチューブと、上記カーボンナノチューブに形成された導電性高分子と、上記カーボンナノチューブ上に形成された透明電極とを含むことを特徴とする。

(もっと読む)

アモルファスシリコンフォトダイオード及びその製造方法ならびにX線撮像装置

【課題】高感度のアモルファスシリコンフォトダイオードおよびその製造方法ならびにそのアモルファスシリコンフォトダイオードを用いた低被爆量型のX線撮像装置を提供する。

【解決手段】絶縁性基板と、前記絶縁性基板の上に形成された第1導電型アモルファスシリコン層と、前記第1導電型アモルファスシリコン層の上に形成されたi型アモルファスシリコン層と、前記i型アモルファスシリコン層の上に形成された第2導電型のアモルファスシリコン層と、前記絶縁性基板と前記第1導電型アモルファスシリコン層との間において、その周端面が前記第1導電型のアモルファスシリコン層の周端面よりも内側となるように設けられた金属電極と、を備えたことを特徴とするアモルファスシリコンフォトダイオードが提供される。

(もっと読む)

イメージセンサ及びその製造方法

【課題】本発明は、トランジスタ回路(circuitry)とフォトダイオードの新たな集積を実現できるイメージセンサ及びその製造方法を提供するためのものである。

【解決手段】本発明によるイメージセンサは、下部配線を含むCMOS回路(circuitry)が形成された基板、上記基板の上に分離されて形成された第1配線及び第2配線、上記第1配線の側面に形成された第1導電型伝導層、上記第2配線の側面に形成された第2導電型伝導層、及び上記第1導電型伝導層と上記第2導電型伝導層との間に形成された真性層(intrinsic layer)を含むことを特徴とする。

(もっと読む)

量子ドット型光検知器及びその製造方法

【課題】感度を向上させることができる量子ドット型光検出器及びその製造方法を提供する。

【解決手段】中間層4上に、InAsからなる複数の量子ドット5が形成されている。中間層4上で量子ドット5の間の領域には、真性AlAsからなるAlAs層6が形成されている。AlAs層6の厚さは、量子ドット5の高さよりも小さい。更に、量子ドット5上に、真性AlSbからなるAlSb層7が量子ドット5の表面に倣って形成されている。また、AlAs層6及びAlSb層7を覆う中間層4が形成されている。この中間層4も真性GaAsからなる。量子ドット5、AlAs層6、AlSb層7及びこれらを覆う中間層4から光吸収単位層が構成されている。そして、このような光吸収単位層が更に9層積層されている。従って、総計で10層の光吸収単位層が設けられている。なお、薄いAlAs層6が量子ドット5とAlSb層7との間に介在していてもよい。

(もっと読む)

イメージセンサ及びその作製方法

【課題】受光部での隣接画素への漏れ込みを防止して、高開口率、高密度の受光画素を備えたイメージセンサおよびその作製方法を提供することを目的とする。

【解決手段】光電変換層に溝部を形成し、この溝部に絶縁性の光吸収物を埋め込む。光吸収物の下部の光電変換層(溝部の下に残存した光電変換層)は光吸収物によって遮光されるため、フォトキャリアが生じないことを利用する(段落0013)。なお、光吸収物が確実に溝部に埋め込まれる深さである必要があるので、溝部は光電変換層を貫通せず、溝部の下に光電変換層を残存させている(段落0070)。

(もっと読む)

半導体装置

【課題】光センサとして機能する半導体装置の静電破壊を防止する。

【解決手段】フォトダイオード103およびフォトダイオード103の出力を増幅する回路101を有する。フォトダイオード103および回路101上に、絶縁層を介して2つの端子111、112と共に、2つの端子111、112に隣接し、2つの端子111、112よりも面積の広いダミー電極110が形成されている。ダミー電極110は半導体装置のフォトダイオード103および回路101のいずれにも接続されない。面積を広くすることで、2つの端子111、112よりもダミー電極110に静電破壊を起こりやすくすることで、半導体装置が静電破壊することを防止する。

(もっと読む)

半導体装置

【課題】出力電圧もしくは出力電流の範囲を広げることなく、検出可能な照度範囲が広い光電変換装置を得ること、光センサの特性ばらつきによる出力ばらつきが小さい光電変換装置を得ること、消費電力が小さい光電変換装置を得ること、歩留まりが高く、製造コストが小さい光電変換装置を得ることを課題とする。

【解決手段】照度に対応する電流信号を出力する光センサと、光センサから出力された電流信号を電圧信号に変換する電流電圧変換回路を有する光検出回路と、光検出回路から出力された電圧信号を増幅する増幅器と、増幅器から出力された電圧と基準の電圧を比較し、制御回路に結果を出力する比較回路と、比較回路からの出力によって、検出する照度範囲を決定し、制御信号を光検出回路へ出力する制御回路とを有し、電流電圧変換回路は、制御信号に従って抵抗値を変える半導体装置を有する。

(もっと読む)

カルコゲナイド層を持つ薄膜トランジスタ及びその製造方法

【課題】カルコゲナイド層を有する薄膜トランジスタ及びその製造方法を提供する。

【解決手段】チャンネル層を構成する非晶質のカルコゲナイド層と、非晶質のカルコゲナイド層の両側部にそれぞれ形成されてソース及びドレイン領域を構成する結晶質のカルコゲナイド層と、結晶質のカルコゲナイド層に連結されたソース電極及びドレイン電極と、非晶質のカルコゲナイド層の上部または下部に、ゲート絶縁層を介在して形成されたゲート電極とを備える薄膜トランジスタである。これにより、カルコゲナイド層を光伝導層として利用して光薄膜トランジスタを具現したり、非晶質のカルコゲナイド層と結晶質のカルコゲナイド層とによって、ダイオード整流機能を具備する電気薄膜トランジスタを具現できる。

(もっと読む)

光デバイス

【課題】ゲルマニウムは、半導体プロセスを用いて光電気混載LSIに搭載される長波長帯光デバイスに用いる場合、吸収の長波長化又は長波長帯での吸収が実用化されていない。

【解決手段】ゲルマニウム原子を主成分とする四面体結合される半導体であり、基板格子定数がゲルマニウムよりも小さく、基板面方位が{111}面であり、基板面と垂直な<111>軸方向に半導体格子を伸長される光電変換層を用いる光デバイスである。

(もっと読む)

受光装置および受光装置の製造方法

【課題】受光部のフォトダイオード周囲の少なくとも一部にフォトダイオードと同導電型の領域を形成し、その領域側に入射した光子によって発生したキャリアを掃き出すことで、フォトダイオードの受光感度特性の向上を可能にする。

【解決手段】第1導電型の半導体基板10に形成されたもので前記第1導電型とは逆の第2導電型の第1領域21を有する受光部11と、前記受光部11の周囲の前記半導体基板10の少なくとも一部に、第1導電型の分離領域23を介して形成されたもので前記第1領域21と電気的に独立した第2導電型の第2領域22とを備え、前記第2領域22は、前記第1領域21とは独立した電位に固定され、前記受光部11上に形成された層間絶縁膜41の開口部42は前記第1領域21上から前記分離領域23上を通り前記第2領域22の一部上に形成されていることを特徴とする。

(もっと読む)

pin型フォトダイオードを作製する方法

【課題】暗電流のばらつきを低減可能なpin型フォトダイオードを作製する方法を提供する。

【解決手段】パッシベーションのためのInP半導体29を成長した後に、燐雰囲気中で熱処理31を行うので、半導体メサ上に成長されたInP半導体がマイグレートする。熱処理の結果、マイグレートによりInP半導体29aの厚みの均一性が良好になる。

(もっと読む)

イメージセンサ及びその製造方法

【課題】CMOSイメージセンサ及びその製造方法を提供する。

【解決手段】基板上部に第1絶縁膜を形成する段階と、前記基板の光活性領域の上部の前記第1絶縁膜の一部分を除去して前記第1絶縁膜に凹部を形成する段階と、を有する。内部レンズ及びエッチング阻止膜は前記基板上部に同時に形成される。前記内部レンズは前記第1絶縁膜の凹部を埋め込み、前記エッチング阻止膜は前記内部レンズを覆って前記第1絶縁膜上部に延長される。第2絶縁膜は前記内部レンズと前記エッチング阻止膜上部に形成することができる。前記第2絶縁膜は前記エッチング阻止膜と相違する物質で形成することができる。キャビティーは前記内部レンズ上部の前記第2絶縁膜に形成されることができる。

(もっと読む)

半導体、p型半導体、半導体接合素子、pn接合素子、および光電変換装置

【課題】禁制帯幅および導電型のうちの少なくとも一つを応用目的に応じて正確に制御できて、実用に足る、半導体、p型半導体、半導体接合素子、pn接合素子、および光電変換装置を提供すること。

【解決手段】硫化鉄に、Mg、Zn、または、Ia族元素を混ぜることにより、半導体を作製する。また、この半導体を用いて、半導体結合素子または光電変換装置を作製する。

(もっと読む)

半導体装置及びそれを用いた電子機器

【課題】外部環境に対しより安定した光検出機能を有する半導体装置を得ることを課題とする。

【解決手段】第1のフォトダイオードと、遮光された第2のフォトダイオードと、ボルテージフォロワ回路を含む第1の回路群と、第2の回路群と、補正用回路とを有し、第1のフォトダイオードの出力は第1の回路群のボルテージフォロワ回路に入力され、第1の回路群の出力は補正用回路に入力され、第2のフォトダイオードの出力は第2の回路を介して補正用回路に入力される。これら入力を補正用回路にて加算及び減算、もしくはそのいずれか一方を行うことで、第1のフォトダイオードにおける温度に起因した出力変動を除去する。なお、第1のフォトダイオードには開放電圧が出力されるよう基準電位が供給され、第2のフォトダイオードには順方向のバイアスが印加されるよう電位が供給されている。

(もっと読む)

光検出素子及びその製造方法

【課題】ゲッタリング効果を向上させつつ、電気的特性のばらつきを低減する。

【解決手段】シリコンを母材としており、炭素を所定濃度で含有する半導体基板101と、半導体基板101上にシリコンを母材としてエピタキシャル成長されてなり、半導体基板101から所定距離だけ離間する領域に光検出部(主に104)を有するエピタキシャル層102とを備え、半導体基板101は、半導体基板101に含有される炭素が所定濃度になるようにシリコンを含有する材料と炭素を含有する材料とが溶融された原料融液から結晶成長されてなる。

(もっと読む)

61 - 80 / 103

[ Back to top ]