Fターム[5F049RA03]の内容

受光素子−フォトダイオード・Tr (21,418) | モジュール化 (1,539) | 同種複数素子 (827) | アレイ (818) | PN分離 (175)

Fターム[5F049RA03]に分類される特許

161 - 175 / 175

固体撮像装置

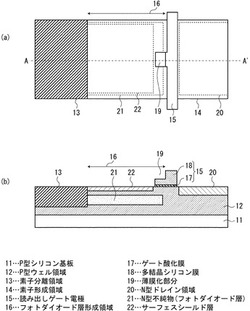

【課題】 受光感度を向上させることができる固体撮像装置を提供する。

【解決手段】 半導体基板11と、半導体基板11上に形成されるウェル領域12と、ウェル領域12内に形成されるフォトダイオード層21と、ウェル領域12上のフォトダイオード層21に隣接し、ゲート酸化膜17と半導体材料18との積層構造である読み出しゲート電極15と、読み出しゲート電極15の側部に形成されるドレイン層20を備える。そして、フォトダイオード層21側の半導体材料18の一部が、ドレイン層20側の半導体材料18の一部よりも薄いことを特徴としている。

(もっと読む)

イメージセンサの画素及びその製造方法

本発明は、イメージセンサの画素で充填率をより高めるために、画素内部のフィールド酸化膜の一部領域または全領域をフォトダイオードとして使えるようにするものである。本発明のイメージセンサの画素は、半導体基板の内部に埋め込まれて形成されたフォトダイオードと、フォトダイオードの前記形成後に形成された画素トランジスタと、を含む。本発明のイメージセンサの画素は、画素トランジスタと、画素トランジスタを分離するフィールド酸化膜と、フィールド酸化膜の一部面積または全面積の下部に位置するフォトダイオードと、を含む。本発明のイメージセンサの画素の製造方法は、(a)半導体基板の所定の領域にトレンチを形成するステップと、(b)前記トレンチ領域の少なくとも一部分を含むフォトダイオードを形成するステップと、(c)前記フォトダイオードの前記形成後に、画素トランジスタを形成するステップと、を含む。本発明によれば、フォトダイオードの表面積が広がって、充填率が向上し、光感度を向上することができ、イメージセンサの単位画素でトランジスタが形成される領域を除いては、全てフォトダイオード領域となり、充填率が最大化する。  (もっと読む)

(もっと読む)

半導体装置

【課題】 4分割光検出器において、素子分離構造の形成工程が複雑である。

【解決手段】 区画毎のPINフォトダイオード(PIN−PD)の共通のアノードとなるP-sub層80の上に、PIN−PDのi層となる高比抵抗のエピタキシャル層82を成長させる。区画62境界に、基板表面からのイオン注入によって、p+領域である分離領域64を形成する。各区画毎に形成したカソード領域66と、P-sub層80とを逆バイアスしてPIN−PDを機能させる際、分離領域64はP-sub層80と共に接地電位とされアノードとなる。その結果、分離領域64とP-sub層80とに挟まれた位置のエピタキシャル層82には、電子に対する電位障壁が形成される。これにより、各区画にて光の吸収で発生した電子が隣接する区画へ移動することが防止され、素子分離が実現される。

(もっと読む)

受光装置およびそれを用いた電子機器

【課題】 複数のフォトダイオードを組み合わせて所望の分光感度特性を実現可能な受光装置を提供する。

【解決手段】 受光装置100において、複数のフォトダイオード10は、同一の半導体基板30上に平面的に配置され、分光感度特性が異なるように設計される。フォトダイオード10は、それぞれ異なる濃度、深さのプロファイルを有する拡散層を用いて形成される。フォトダイオード10は、異なる位置に平面的に配置され、アノード電極50およびカソード電極52は、独立に設けられている。各フォトダイオード10に流れる光電流Ipは、合成回路により合成される。

(もっと読む)

固体撮像装置およびその製造方法

【課題】 赤外域の光に対して高い感度を有する固体撮像装置において、その空乏化領域の深さの低減化を図ることができるようするものである。

【解決手段】 シリコン半導体による受光センサ部1を有する固体撮像装置であって、受光センサ部1の光電変換素子を構成する空乏化領域を構成する第1導電型のウエル領域13の受光面側にβ−FeSi2等のシリコンに比しバンドギャップが小さく赤外領域に高い吸収性を有する金属シリサイド層20を設ける。

(もっと読む)

固体撮像素子及びその製造方法

【課題】 電荷蓄積領域の実効面積を犠牲にすることなく単位画素の微小化を可能とする固体撮像素子及びその製造方法を提供する。

【解決手段】 基板上に所定の開口を有するハードマスクを形成する工程と、前記基板に前記開口側に一部延長し、該延長部分が主要部分と異なる不純物濃度を有する前記画素を構成する第1導電型の電荷蓄積領域を形成する工程と、前記電荷蓄積領域の延長部分の、少なくとも一部の第1導電型不純物濃度を、前記電荷蓄積領域の主要部分の形成とは独立に制御する工程と、前記開口下に形成された前記拡散層に接するように、前記開口内に前記絶縁膜を形成する工程とによって固体撮像素子を製造する。

(もっと読む)

半導体受光装置及び半導体受光装置の製造方法

【課題】

半導体受光装置におけるフォトダイオードを分割する領域での受光感度の低下を抑制する。

【解決手段】

複数のフォトダイオード部2−1、2−2と、分離部21とを具備する半導体受光装置を用いる。複数のフォトダイオード部2−1、2−2は、半導体基板10上に設けられ、受光した光を電気に変換する。分離部21は、複数のフォトダイオード部2−1、2−2を互いに電気的に分離する。分離部21は、表面部分の不純物濃度が、第1濃度以下である。第1濃度は、青紫レーザ光以上の波長に対する分離部21の受光感度が、複数のフォトダイオード部2−1、2−2の各々における受光感度に概ね等しくなる濃度である。

(もっと読む)

半導体装置およびその製造方法

【課題】開口部を形成してもリークの原因となるダメージを与えることなく、短絡せずにフォトダイオードを構成することができる半導体装置とその製造方法を提供する。

【解決手段】第1導電型の第1半導体層(10,11)の主面に第2導電型の第2半導体層(12,16)が形成され、少なくとも上記第2半導体層において形成された素子分離領域(13,14,15,17)が形成されて複数のフォトダイオードの領域(PD1〜PD4)に分離されており、複数のフォトダイオード全体に対する外周部において第2半導体層(16)に接続し、個々のフォトダイオード毎に分割されたパターンで、第2半導体層(16)の上層に導電層18が形成されており、導電層18を被覆して全面に絶縁層(19,21)が形成されており、導電層18のパターンより内側の領域において絶縁層(19,21)に第2半導体層(16)に達する開口部が形成されている構成とする。

(もっと読む)

半導体受光素子を有する集積回路

【課題】 複数の受光素子による受光感度を同程度にし、かつ、不要な波長帯域の光強度をほぼ同じ状態にして演算回路で除去することにより、カラーイメージセンサや可視光の照度センサとし得るように所望の波長での光強度を正確に検出することができる受光素子を有する集積回路を提供する。

【解決手段】 p型の半導体基板1上にほぼ均一な厚さのn型半導体層2が設けられ、そのn型半導体層2の異なる場所に、n型半導体層2の表面から複数個(第1〜第3)のp型領域31〜33が異なる深さで設けられることにより、複数個(第1〜第3)の受光用pn接合ダイオードD1〜D3が形成されている。そして、複数個の受光用pn接合ダイオードD1〜D3の検出電流を演算することにより異なる深さのpn接合に対応する波長の光を検出する演算回路が半導体基板1上に形成されている。

(もっと読む)

固体撮像装置及びその製造方法

【課題】暗電流や白キズの発生を従来に比べて低減すると共に、フォトダイオードの飽和電荷量の向上をも図り得る固体撮像装置、及びその製造方法を提供する。

【解決手段】受光部15が形成された半導体基板1を備える固体撮像装置である。受光部15は、半導体基板1に形成されたp型の第1不純物領域(表面反転層)6と、表面反転層6の下に形成されたn型の第2不純物領域(光電変換領域)4とを有している。光電変換領域4は、半導体基板1にn型の不純物を導入して形成する。表面反転層6は、半導体基板1の光電変換領域4が形成された領域に、インジウムを導入して形成する。

(もっと読む)

受光素子およびその製造方法

【課題】受光部と、信号処理回路部とを備えた受光素子において、信号処理回路部の最表面に形成された遮光膜を配線として利用し、高性能かつ低コストの受光素子を提供する。

【解決手段】本発明の受光素子には、光ディスク(不図示)からの戻り光を受ける受光部100、信号処理回路部200、ボンディングパッド部300などが形成されている。信号処理回路部200には、各種トランジスタや配線8、10などが配置されて、その上に保護膜としてSiN膜11が全面に形成されている。SiN膜の上にはさらに、Au/Ti層13が形成されている。Au/Ti層13は、遮光膜の役割を果たすとともに、スルーホール12を介して配線10と電気的に接続され、配線の一部あるいはボンディングパッドの一部として機能する。

(もっと読む)

光電変換装置、その製造方法及び撮像システム

【課題】 電荷蓄積領域から電荷を出力する際の電荷転送特性の改善と電荷蓄積時の暗電流発生の抑制を両立する。

【解決手段】 電荷蓄積領域の空乏化電圧を0から電源電圧/2(V)の範囲で形成し、電荷転送期間中の転送MOSトランジスタのゲート電位を電源電圧/2から電源電圧(V)の範囲で形成し、電荷蓄積期間中の転送MOSトランジスタのゲート電位を−(電源電圧/2)から0(V)の範囲で形成することを特徴とする。

(もっと読む)

イメージセンサ及びその製造方法

【課題】 優れた感度(sensitivity)を有するイメージセンサを提供する。

【解決手段】 本発明のイメージセンサは半導体基板上に形成された活性画素アレイ領域のメイン画素アレイ領域を備えている。前記センサ上部にパッシベーション膜が形成され、前記パッシベーション膜は少なくとも前記メイン画素アレイ領域のすべてを露出させる。その結果、前記メイン画素アレイ領域上で前記パッシベーション膜による光吸収率及び屈折率を取り除いてイメージセンサの光感度を改善させる。

(もっと読む)

集積されたピンダイオードおよび関連の回路構造を製造する方法

特に、埋め込まれた領域(20)と、埋め込まれた領域(20)に通じる端子領域(32)とを含む集積されたピンフォトダイオードを製造する方法に関する説明が与えられる。本発明による製造方法は、1つの伝導型のドーピングされた領域(20)を生成するステップと、基板から遠いドーピングされた領域(42)を生成するステップと、中間領域(30)を生成するステップと、少なくとも1つの導電性端子領域(32)を生成するステップとを含む。本製造方法は、ピンフォトダイオード(14)が単純な方法で集積されることを可能にする。さらに、ピンダイオードを製造するプロセスステップはまた、遮蔽ウェル(22、56)を製造するためにも利用され得る可能性がある。  (もっと読む)

(もっと読む)

キャリアの移動性と画像の青感度を改善するひずみシリコン層を有するピクセル

付随するひずみシリコン層を備えるピクセルセルを有するイメージャである。ひずみシリコン層は電荷転送効率を増大し、残像を減少し、撮像デバイスにおける青感度を改善する。  (もっと読む)

(もっと読む)

161 - 175 / 175

[ Back to top ]