Fターム[5F049RA03]の内容

受光素子−フォトダイオード・Tr (21,418) | モジュール化 (1,539) | 同種複数素子 (827) | アレイ (818) | PN分離 (175)

Fターム[5F049RA03]に分類される特許

1 - 20 / 175

半導体装置の製造方法

【課題】X線検出用フォトダイオード等においては、初期結晶材料として、裏面側に高濃度の不純物がドープされた単結晶ウエハ等を使用する場合がある。このような場合、裏面側不純物の外方拡散によるクロスコンタミネーション等を防止するために、予め、ウエハの裏面に、酸化シリコン膜等の不純物外方拡散防止膜等を形成しておく等の対策が講じられる。しかし、裏面に不純物外方拡散防止膜を形成する際に、ウエハの表面を損傷する等の問題が有る。

【解決手段】本願発明は、裏面に高濃度の不純物ドープ層を有する半導体ウエハの裏面に、不純物防止膜を形成するに当たり、まず、前記半導体ウエハの表面に酸化シリコン系絶縁膜等の表面保護膜を形成し、その状態で、前記裏面に、前記不純物防止膜を形成し、その後、ウエットエッチングにより、前記不純物防止膜を残した状態で、前記表面保護膜をほぼ全面的に除去するものである。

(もっと読む)

光検出装置

【課題】開口率を著しく向上することが可能な光検出装置を提供すること。

【解決手段】光検出装置1は、半導体基板1Nを有する半導体光検出素子10Aと、半導体光検出素子10に対向配置される搭載基板20とを備える。半導体光検出素子10Aは、ガイガーモードで動作すると共に半導体基板1N内に形成された複数のアバランシェフォトダイオードAPDと、それぞれのアバランシェフォトダイオードAPDに対して電気的に接続されると共に半導体基板1Nの主面1Nb側に配置された電極E7とを含む。搭載基板20は、電極E7毎に対応して主面20a側に配置された複数の電極E9と、それぞれの電極E9に対して電気的に接続されると共に主面20a側に配置されたクエンチング抵抗R1とを含む。電極E7と電極E9とが、バンプ電極BEを介して接続されている。

(もっと読む)

光電変換回路

【課題】 BPDに濃度勾配を設ける特別なウェハプロセスを用いることなく、感度が高く規定の時間内にBPD内の信号電荷がFDに転送される光電変換回路を得る。

【解決手段】 受光領域への入射光により電荷が生成され蓄積される複数のBPDと、一方の端子に少なくとも2つの前記BPDが接続され、オン状態/オフ状態に切り替える制御信号が入力される制御端子が共通接続された少なくとも1つのTGと、各々の前記TGの他方の端子が接続され、各々の前記TGが同時にオン状態に切り替わることにより、各々の前記BPDの前記電荷が同時に転送され集約するFDとを備え、前記FDから各々の前記BPDの前記受光領域の最遠部の間の最大距離が、規定の時間内で各々の前記BPDの前記電荷の全てが各々の前記BPDから前記FDに転送される距離である。

(もっと読む)

撮像素子

【課題】 撮像性能の向上に適した撮像素子の新たな構造を提供する。

【解決手段】 撮像素子は、第1チップ、および第2チップを備える。この第1チップには、受光画素、および貫通配線とが形成される。複数の受光画素は、受光面に配列され、入射光に応じた電気信号を生成する。貫通配線は、受光画素の電気信号を受光面の反対面へ伝達する。一方、第2チップには、読み出し回路が形成される。読み出し回路は、貫通配線を介して電気信号を読み出して画像信号として出力する。この撮像素子は、上記の第1チップの反対面と、上記の第2チップの読み出し回路とが対向する向きに配置され、貫通配線と読み出し回路との端子間が電気的に接合される。

(もっと読む)

放射線検出器

【課題】半導体基板に発生したキャリアが流れ込む半導体領域を半導体基板の一方の主面側に配置した上で、放射線の入射位置を2次元で検出することが可能な放射線検出器を提供すること。

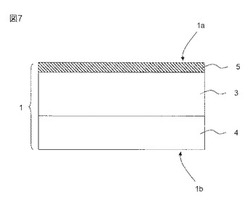

【解決手段】放射線検出器RD1は、第一導電型の半導体基板1と、半導体基板1と接合を構成する複数の第二導電型の半導体領域10と、対応する半導体領域10に接合された複数の電極21,23とを備える。電極21,23は、第一主面1aに直交する方向から見て、対応する半導体領域10を覆う。半導体領域10は、2次元配列された複数の第一及び第二半導体領域11,13を含む。複数の第一半導体領域11のうち2次元配列における第一方向に配列された第一半導体領域11同士が互いに電気的に接続され、複数の第二半導体領域13のうち第一方向に交差する第二方向に配列された第二半導体領域13同士が互いに電気的に接続される。

(もっと読む)

光検出素子、光検出素子の制御方法

【課題】光電変換部での飽和の可能性を低減して光電変換部の小型化を可能にし、全体としてのサイズの小型化を可能にする。

【解決手段】分離電極14aと蓄積電極14bとが障壁制御電極14cを挟んで配置される。分離電極14aと蓄積電極14bと障壁制御電極14cとに正極性の電圧が印加されてウェル12にポテンシャル井戸が形成された状態で光照射による電子が集積される。その後、障壁制御電極14cに印加された電圧に応じて形成されるポテンシャル障壁の高さが調節されることにより、規定した一定量の不要電荷が電荷分離部で分離される。電子の集積と不要電荷の分離とが複数回繰り返された後、蓄電電極14bに対応して形成された電荷蓄積部に流れ込んだ有効電荷が受光出力として取り出される。

(もっと読む)

フォトダイオード及びフォトダイオードアレイ

【課題】シリコンフォトダイオード及びシリコンフォトダイオードアレイであって、近赤外の波長帯域に十分な分光感度特性を有しているフォトダイオード及びフォトダイオードアレイを提供すること。

【解決手段】フォトダイオードPD5は、P−型半導体基板20を備え、裏面入射型である。P−型半導体基板20は、互いに対向する第1及び第2主面0a,20bを有し、光感応領域21を含む。光感応領域21は、N+型不純物領域23と、P+型不純物領域25と、P−型半導体基板20においてバイアス電圧を印加した際に空乏化する領域とからなる。P−型半導体基板20の第2主面20bには、不規則な凹凸10が形成されている。P−型半導体基板20の第2主面20b側には、アキュムレーション層37が形成されており、アキュムレーション層37における、光感応領域21に対向している領域は光学的に露出している。

(もっと読む)

フォトダイオードアレイ

【課題】シリコンフォトダイオードアレイであって、近赤外の波長帯域に十分な分光感度特性を有しているフォトダイオードアレイを提供すること。

【解決手段】フォトダイオードアレイPDA1は、複数の光検出チャンネルCHがn型半導体層32を有する基板Sを備える。フォトダイオードアレイPDA1は、n型半導体層32上に形成されたp−型半導体層33と、光検出チャンネルCH毎に設けられると共に信号導線23に一端部が接続される抵抗24と、複数の光検出チャンネルCHの間に形成されるn型の分離部40とを備える。p−型半導体層33は、n型半導体層32との界面でpn接合を構成し、被検出光の入射によって生じたキャリアをアバランシェ増倍させる増倍領域AMを光検出チャンネルに対応して複数有する。n型半導体層32の表面には不規則な凹凸10が形成されており、当該表面は光学的に露出している。

(もっと読む)

プラズマ損傷からフォトダイオードを保護するCMOSイメージセンサの製造方法

【課題】暗電流の原因となるプラズマ損傷や感光膜除去工程による重金属汚染を防止する

ことのできるCMOSイメージセンサのフォトダイオードの製造方法を提供すること。

【解決手段】本発明のCMOSイメージセンサの製造方法は、所定の工程が完了した基板

を用意するステップと、該基板のフォトダイオードの形成される領域の上部にパターニン

グされたブロック層を形成するステップと、該パターニングされたブロック層を残した状

態で、前記フォトダイオードの形成される領域を除く残りの領域に対して、マスクを用い

たイオン注入を行うステップと、前記マスクを除去するステップとを含む。

(もっと読む)

固体撮像素子

【課題】 暗電流の抑制や受光部の入射光量の増大により、得られる画像データ画質を改善した固体撮像素子を提供する。

【解決手段】 固体撮像素子1は、半導体から成る基板10と、基板10中に形成され光電変換によって生じた電荷を蓄積する基板とは逆の導電型の半導体から成る受光部11と、基板10上に設けられる絶縁層12と、絶縁層12上に設けられ受光部11が蓄積する電荷と同じ極性の固定電荷を有する固定電荷層13と、固定電荷層13上に設けられる反射防止層14と、基板10中の受光部11と隣接する位置に設けられ受光部11から読み出された電荷が一時的に蓄積される電荷転送部15と、少なくとも電荷転送部15の直上に設けられる転送電極16と、を備える。反射防止層14は、受光部11の直上の領域内に設けられる。

(もっと読む)

フォトダイオードアレイ

【課題】特性の高いフォトダイオードアレイを提供する。

【解決手段】アバランシェフォトダイオードに一端が電気的に接続され、その光入射面上に配置された抵抗4と、抵抗4の他端に接続された信号導線の読み出し部3aとを備え、エピタキシャル半導体層上に形成された第1の絶縁膜16aと、第1の絶縁膜16a上に形成された第2の絶縁膜16bとを備え、抵抗4は、第1の絶縁膜16aと第2の絶縁膜16bとの間に介在し、信号導線3は、第2の絶縁膜16b上に設けられている。

(もっと読む)

光電変換素子及び撮像装置、太陽電池

【課題】十分な感度を有し、かつ低いコストで実現することが可能な構成の光電変換素子を提供する。

【解決手段】チオインジゴ誘導体を含んで成る光電変換層12を有する、光電変換素子10を構成する。

(もっと読む)

光電変換素子用蒸着材料及び光電変換素子、センサ、撮像素子

【課題】光電変換効率が高く、光電流/暗電流のS/N比の良好であり、且つ、応答速度の速い光電変換素子を提供する

【解決手段】一対の電極(20,40)と、一対の電極(20,40)に挟持された少なくとも光電変換層32を含む受光層30を有する光電変換素子1は、受光層30の少なくとも一部の層が、フラーレン又はフラーレン誘導体を主成分とする複数の粒子又は該複数の粒子が成形されてなる成形体であり、複数の粒子のD50%で表される平均粒径が50μm〜300μmであるの光電変換素子用蒸着材料を用いて蒸着されたフラーレン又はフラーレン誘導体を含むものである。

(もっと読む)

光センサ、及び、その製造方法

【課題】光の左右比の検出精度の低下が抑制された光センサ、及び、その製造方法を提供する。

【解決手段】半導体基板(10)に受光素子(20)が形成され、受光素子(20)の形成面(10a)上に、透光膜(30)を介して遮光膜(40)が形成され、遮光膜(40)に透光用の開口部(50)が形成された光センサであって、仮想直線(VL)を介して線対称の関係にある一対の受光素子(21,22)及び一対の開口部(51,52)を有し、形成面(10a)に直交する高さ方向に沿う光を、開口部(51,52)を介して受光素子(21,22)に照射した際に、一対の受光素子(21,22)から出力される出力信号に基づいて、高さ方向に沿う光が開口部(51,52)を介して受光素子(21,22)に入射した際に出力される一対の受光素子(21,22)の出力信号が互いに一致するように、各出力信号を補正する。

(もっと読む)

固体撮像装置及びその製造方法

【課題】光電変換層に対して位置合わせずれの小さい色フィルタを備えた固体撮像装置及びその製造方法を提供する。

【解決手段】半導体基板10内に形成され、入射光を電気信号に変換する光電変換層15と、半導体基板10の表面に形成され、光電変換層15から出力された電気信号を処理する回路と、半導体基板10の裏面に光電変換層15に対応するように配置された赤、緑、青フィルタ23R、23G、23Bとを備える。赤フィルタ23Rは、半導体基板10を通過する光を透過する。半導体基板10の裏面に対して垂直な断面において、赤フィルタ23Rの下面の長さはその上面の長さより長く、緑フィルタ23Gの下面の長さはその上面の長さより短い。

(もっと読む)

受光素子アレイ、その製造方法および検出装置

【課題】 近赤外の長波長領域まで受光でき、かつ画素ピッチを密にしても受光感度を確保できる、受光素子アレイ等を提供する。

【解決手段】 この受光素子アレイ10は、近赤外波長領域に対応するバンドギャップエネルギを有する受光部Pが、複数、配列され、受光部は、選択拡散によって形成されたp型領域6の先端部にpn接合15を有し、受光部Pを区分けするように、n型領域7が該受光部の間に位置することを特徴とする。

(もっと読む)

半導体受光装置

【課題】 キャパシタンスおよびインダクタンスの両方を抑制することができる半導体受光装置を提供する。

【解決手段】 半導体受光装置は、基板と、前記基板上に設けられ、第1導電型領域および第2導電型領域を備え、上面および側面を有する半導体受光素子と、前記上面において、前記第1導電型領域と電気的に接続された第1電極と、前記第2導電型領域に電気的に接続された第2電極と、前記半導体受光素子の前記上面および側面を覆う絶縁膜と、前記第1電極と接続され、前記上面および側面の前記絶縁膜上を経て前記基板上にまで延在して設けられた引出配線と、前記半導体受光素子の上面あるいは側面に位置し、前記基板上における前記引出配線の第1の幅よりも狭い前記引出配線の第2の幅の領域と、を有する。

(もっと読む)

光検出装置および電子機器

【課題】単一の受光素子を用いた簡単な構成による小型かつ低コストな近接/方向センサとして、対象物体の近接/非近接状態の変化とそれに直交する移動方向を、同時に最も効率よく検出して人体の動作に十分に追随させるための光検出装置を提供する。

【解決手段】受光素子200は、反射光103が直接入射する第1のウェル301と、第1のウェル301を挟んで対向し、かつ反射光103は遮光されて入射しない第2のウェル302及び第3のウェル303とを備えている。受光素子200による受信信号は、第1のウェル301の出力と第2のウェル302の出力との和、及び、第1のウェル301の出力と第3のウェル303との出力の和を、時間軸上で交互に出力する。この受信信号に基づいて、光検出装置天面の法線方向である第1の軸方向に沿う対象物体の近接状態と、前記対象物体の近接状態が変化した際の移動方向とが判定される。

(もっと読む)

フォトダイオードアレイモジュール及びその製造方法

【課題】 精密な計測が可能なフォトダイオードアレイモジュールを提供する。

【解決手段】 このフォトダイオードアレイモジュールは、第1波長帯域の光に感応する第1フォトダイオードアレイを有する第1半導体基板2と、第2波長帯域の光に感応する第2フォトダイオードアレイを有する第2半導体基板2’と、複数のアンプAMPが形成されると共に第1及び第2半導体基板2,2’が重なることなく横に並べ、各フォトダイオードをバンプを介してアンプAMPに接続した第3半導体基板3とを備えている。第1半導体基板2及び第2半導体基板2’の隣接する端部には、段差部が形成されており、これにより各画素を双方の基板に渡って連続して整列させた場合においても、低ノイズで計測ができるようになる。

(もっと読む)

半導体装置及びその製造方法

【課題】異なる不純物濃度の埋め込み層を有する半導体装置を短時間かつ低コストで製造する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の表面に第1の酸化膜11を形成する第1の酸化膜形成ステップと、フォトダイオードが形成される第1の領域に形成された前記酸化膜の一部を除去して第1の間隔で第1の開口部を形成すると共に、トランジスタが形成される第2の領域に形成された前記酸化膜を除去して前記半導体基板の表面を露出させる第1の開口部12を形成ステップと、前記第1の酸化膜をマスクとして利用して前記第1の開口部及び前記第2の領域に対して第1の不純物を注入する第1の不純物注入ステップと、前記第1の不純物を熱拡散させる第1の熱拡散ステップと、を有する。

(もっと読む)

1 - 20 / 175

[ Back to top ]